真正的瓶頸-CoWoS 《下一個風口?》

盡管Nvidia試圖大幅增加產量,最高端的Nvidia GPU H100將一直售罄到明年第一季度。

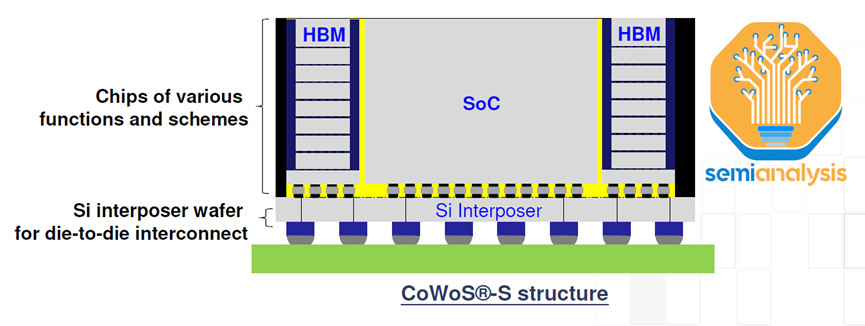

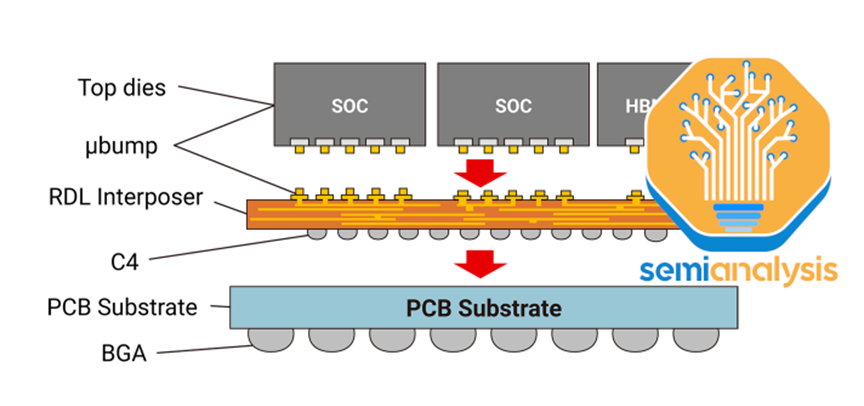

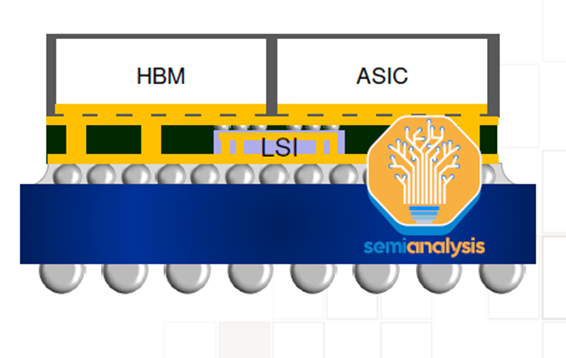

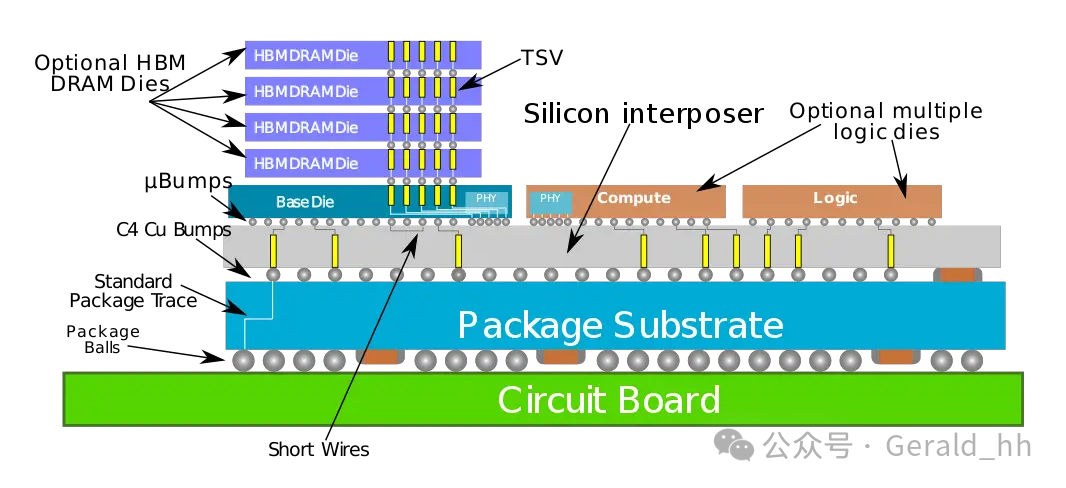

真正的瓶頸是CoWoS容量。CoWoS是臺積電的一種“2.5D”封裝技術,其中多個有源硅芯片(通常的配置是邏輯和HBM堆棧)集成在無源硅中介層上。中介層充當頂部有源芯片的通信層。然后將內插器和有源硅連接到包含要放置在系統PCB上的I/O的封裝基板。

HBM和CoWoS是相輔相成的。HBM的高焊盤數和短跡線長度要求需要2.5D先進封裝技術,如CoWoS,以實現這種密集的短連接,這在PCB甚至封裝基板上是無法實現的。CoWoS是主流封裝技術,以合理的成本提供最高的互連密度和最大的封裝尺寸。由于目前幾乎所有的HBM系統都封裝在Co Wos上,所有先進的人工智能加速器都使用HBM,因此幾乎所有領先的數據中心GPU都是臺積電封裝在Co Wos上的。

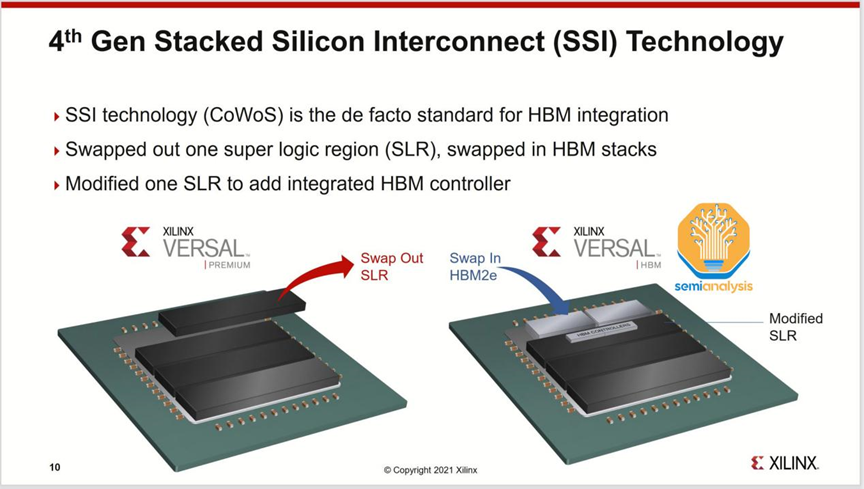

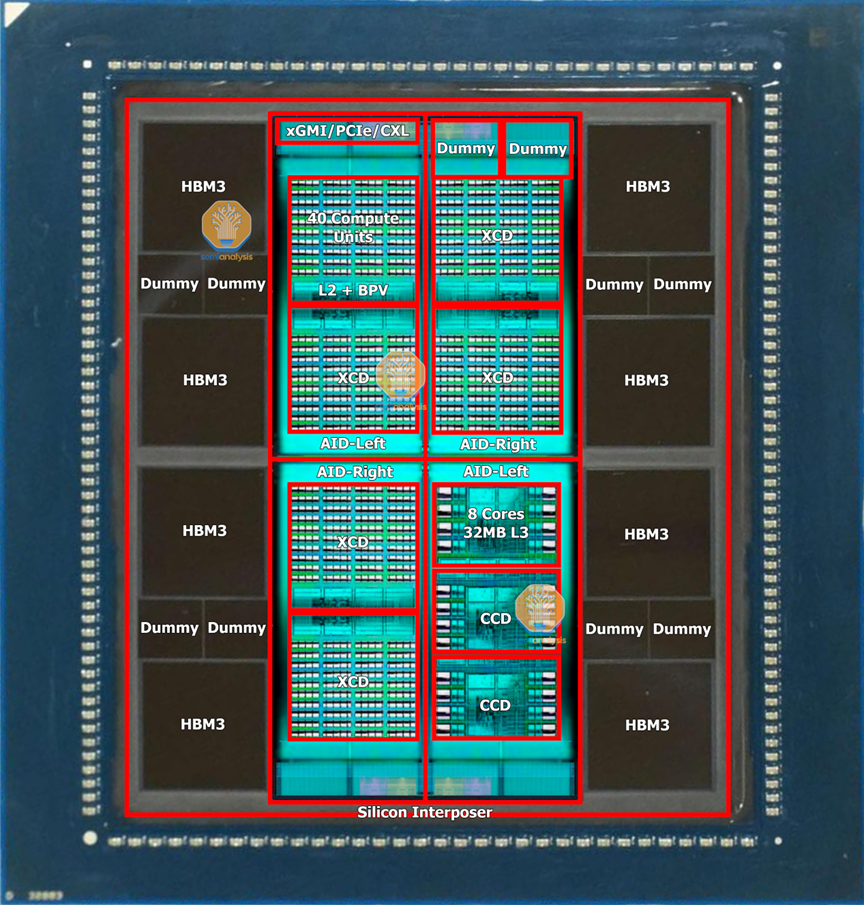

雖然3D封裝技術,如臺積電的SoIC可以直接在邏輯上堆疊芯片,但由于熱量和成本,它對HBM沒有意義。SoIC在互連密度方面處于不同的數量級,更適合用芯片堆疊來擴展片內緩存,這一點可以從AMD的3D V-Cache解決方案中看出。AMD的Xilinx也是多年前將多個FPGA芯片組合在一起的第一批CoWoS用戶。

雖然還有一些其他應用程序使用CoWoS,例如網絡(其中一些用于網絡GPU集群,如Broadcom的Jericho3-AI)、超級計算和FPGA,但絕大多數CoWoS需求來自人工智能。與半導體供應鏈的其他部分不同,其他主要終端市場的疲軟意味著有足夠的閑置空間來吸收GPU需求的巨大增長,CoWoS和HBM已經是大多數面向人工智能的技術,因此所有閑置空間已在第一季度被吸收。隨著GPU需求的爆炸式增長,供應鏈中的這些部分無法跟上并成為GPU供應的瓶頸。

臺積電首席執行官魏哲家表示:“就在最近這兩天,我接到一個客戶的電話,要求大幅增加后端容量,特別是在CoWoS中。我們仍在評估這一點。”

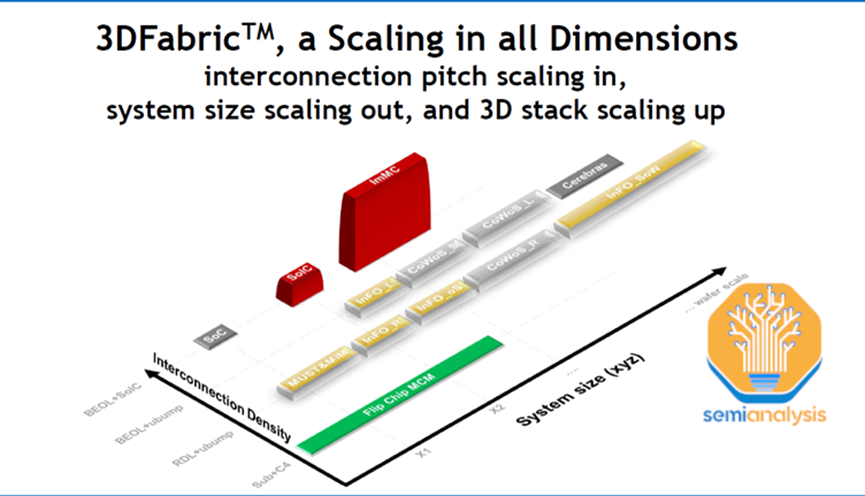

臺積電一直在為更多的封裝需求做好準備,但可能沒想到這一波生成式人工智能需求來得如此之快。6月,臺積電宣布在竹南開設先進后端晶圓廠6。該晶圓廠占地14.3公頃足以容納每年100萬片晶圓的3DFabric產能。這不僅包括CoWoS,還包括SoIC和InFO技術。

有趣的是,該工廠比臺積電其他封裝工廠的總和還要大。雖然這只是潔凈室空間,遠未配備齊全的工具來實際提供如此大的容量,但很明顯,臺積電正在做好準備,預計對其先進封裝解決方案的需求會增加。

確實有點幫助的是,在Wafer級別的扇出封裝能力(主要用于智能手機SoC)方面存在不足,其中一些可以在CoWoS過程中重新使用。特別是有一些重疊的過程,如沉積,電鍍,反磨,成型,放置,和RDL形成。我們將通過CoWoS流程和所有的公司誰看到了積極的需求,因為它在一個后續部分。設備供應鏈中存在著有意義的轉變。

還有來自英特爾、三星和OSAT的其他2.5D封裝技術(如ASE的FOEB),CoWoS是唯一在大容量中使用的技術,因為TSMC是人工智能加速器的最主要的晶圓廠。甚至英特爾哈巴納的加速器都是由臺積電制造和封裝的。

CoWoS變體

CoWoS有幾種變體,但原始CoWoS-S仍然是大批量生產中的唯一配置。這是如上所述的經典配置:邏輯芯片+HBM芯片通過帶有TSV的硅基中介層連接。然后將中介層放置在有機封裝基板上。

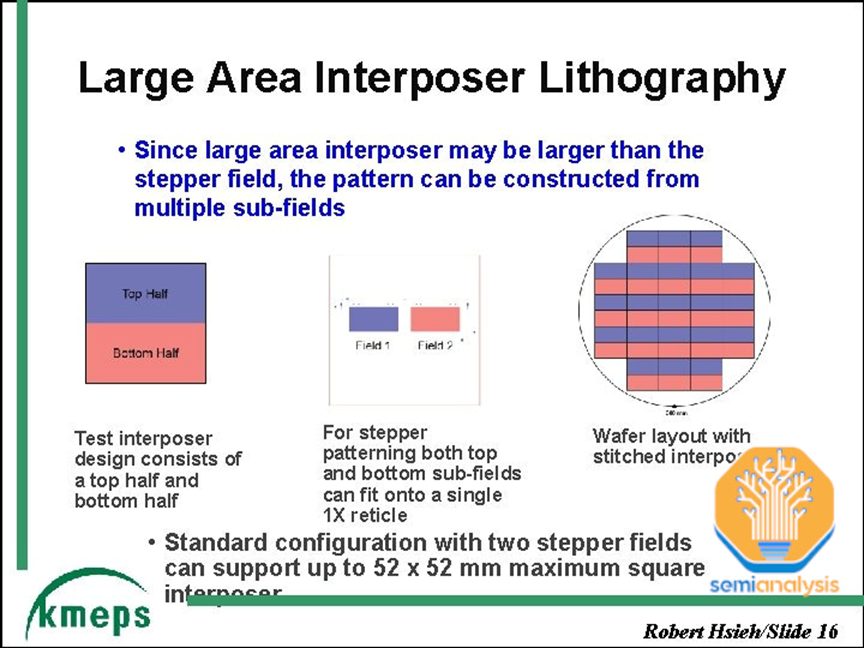

硅中介層的一項支持技術是一種稱為“掩模版縫合”的技術。由于光刻工具狹縫/掃描最大尺寸,芯片的最大尺寸通常為26mmx33mm。隨著GPU芯片本身接近這一極限,并且還需要在其周圍安裝HBM,中介層需要很大,并且將遠遠超出這一標線極限。臺積電解決了這與網線拼接,這使他們的模式插入式多次的刻線限制(目前最高3.5倍與AMD MI 300)。

CoWOS-R使用在具有再分布層(RDL)的有機襯底上,而不是硅中間層。這是一個成本較低的變體,犧牲的I/O密度,由于使用有機RDL,而不是基于硅的插入物。正如我們已經詳細介紹的,AMD的MI300最初是在CoWoS-R上設計的,但我們認為,由于翹曲和熱穩定性問題,AMD不得不使用CoWoS-S。

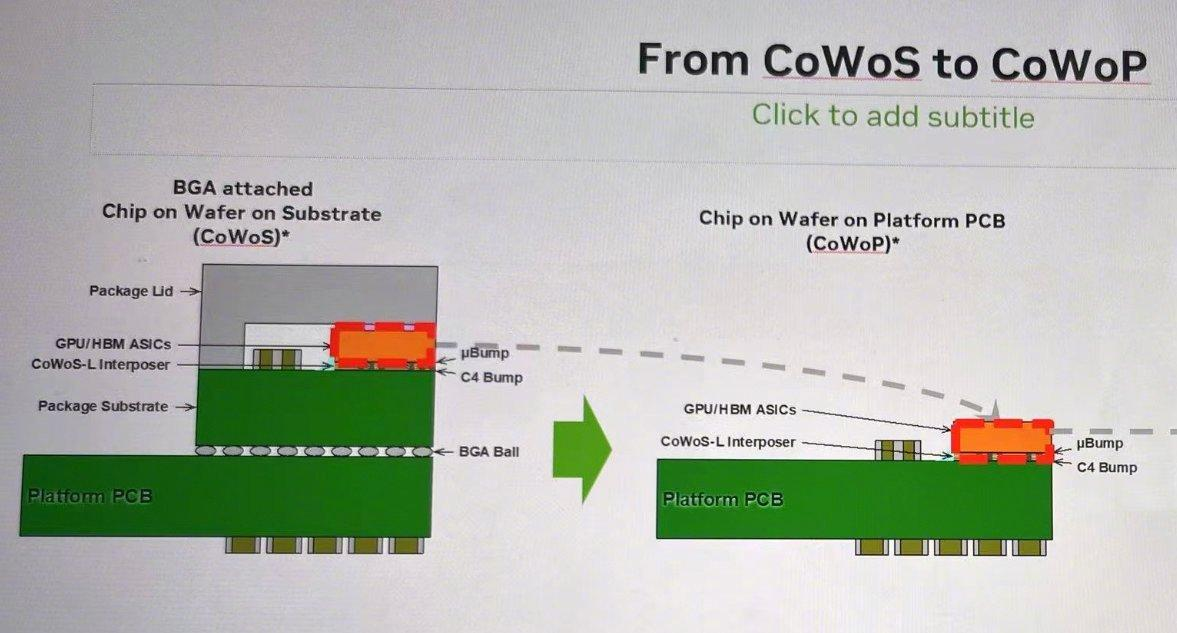

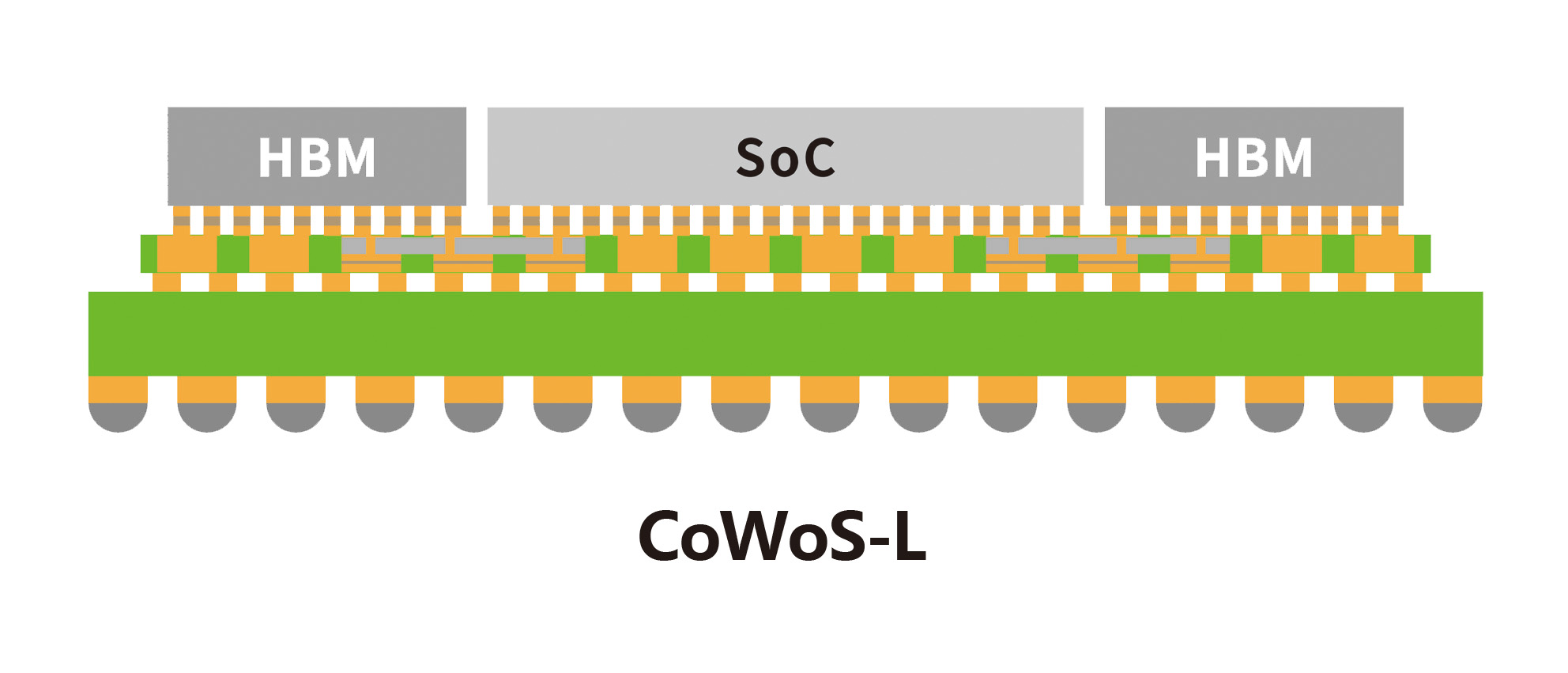

CoWoS-L預計將在今年晚些時候推出,它采用RDL內插器,但包含有源和/或無源硅橋,用于嵌入內插器中的管芯到管芯互連。這是臺積電的相當于英特爾的EMIB封裝技術。這將允許更大的封裝尺寸,因為硅插入物越來越難以擴展。MI300 Co WO S-S可能是一個單一的硅插入器的限制附近。

這將是更經濟的更大的設計去與CoWoS-L臺積電正在研究一個CoWoS-L的超級載波內插器在6倍分劃板的大小。對于CoWOS-S,他們沒有提到 4x reticle 之外的任何內容。這是因為硅插入物的脆弱性。這種硅中間層只有100微米厚,在工藝流程中,隨著中間層尺寸的增大,存在分層或開裂的風險。

據 DigiTimes 報道,臺積電正在加快與后端設備供應商的合作,因為它開始了晶圓基板上芯片(CoWoS)封裝產能的擴張計劃。英偉達在人工智能和高性能計算領域占據主導地位的計算GPU短缺,主要歸因于臺積電有限的CoWoS封裝生產能力。

有報道稱,臺積電計劃到 2023 年底將其目前的 CoWoS 產能從每月 8,000 片晶圓增加到每月 11,000 片晶圓,然后到 2024 年底增加到每月 14,500 至 16,600 片晶圓左右。此前有傳言稱英偉達將提高 CoWoS 產能到 2024 年底,每月生產 20,000 片晶圓。請記住,這些信息來自非官方來源,可能不準確。

Nvidia、亞馬遜、博通、思科和賽靈思等主要科技巨頭都增加了對臺積電先進 CoWoS 封裝的需求,并消耗了他們能獲得的每一片晶圓。據 DigiTimes 報道,臺積電因此被迫重新訂購必要的設備和材料。人工智能服務器的產量顯著增加,刺激了對這些先進封裝服務本已強烈的需求。

Nvidia 已經預訂了臺積電明年可用 CoWoS 產能的 40%。然而,報告稱,由于嚴重短缺,Nvidia 已開始探索與其二級供應商的選擇,向 Amkor Technology 和聯華電子 (UMC) 下訂單,盡管這些訂單相對較小。

臺積電還開始實施戰略變革,例如將其部分 InFO 產能從臺灣北部龍潭工廠重新分配到臺灣南部科學園區 (STSP)。它還在快速推進龍潭基地的擴建。此外,臺積電正在增加其內部 CoWoS 產量,同時將部分 OS 制造外包給其他封裝和測試 (OSAT) 公司。例如,Siliconware Precision Industries (SPIL) 就是這一外包計劃的受益者之一。

臺積電前段時間開設了先進后端 Fab 6 工廠。它將擴大其前端 3D 堆疊 SoIC(CoW、WoW)技術和后端 3D 封裝方法(InFO、CoWoS)的先進封裝產能。目前,該晶圓廠已為 SoIC 做好準備。先進后端 Fab 6 每年可處理約 100 萬片 300 毫米晶圓,每年進行超過 1000 萬小時的測試,其潔凈室空間大于臺積電所有其他先進封裝設施的潔凈室空間總和。

Advanced Backend Fab 6 最令人印象深刻的功能之一是廣泛的五合一智能自動化物料搬運系統。該系統控制生產流程并立即檢測缺陷,從而提高良率。這對于 AMD MI300 等復雜的多小芯片組件至關重要,因為封裝缺陷會立即導致所有小芯片無法使用,從而導致重大損失。該工廠的數據處理能力比平均速度快 500 倍,可以維護全面的生產記錄并跟蹤其處理的每個芯片。

Nvidia 將 CoWoS 用于其非常成功的 A100、A30、A800、H100 和 H800 計算 GPU。AMD 的 Instinct MI100、Instinct MI200/MI200/MI250X 以及即將推出的 Instinct MI300 也使用 CoWoS。

審核編輯:劉清

-

加速器

+關注

關注

2文章

839瀏覽量

40111 -

人工智能

+關注

關注

1817文章

50101瀏覽量

265502 -

FPGA芯片

+關注

關注

4文章

250瀏覽量

41014 -

硅芯片

+關注

關注

0文章

93瀏覽量

17661 -

CoWoS

+關注

關注

0文章

169瀏覽量

11507

原文標題:CoWoS是什么?

文章出處:【微信號:光刻人的世界,微信公眾號:光刻人的世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

LabVIEW 變體:萬能數據容器的藝術

【深度報告】CoWoS封裝的中階層是關鍵——SiC材料

AI芯片發展關鍵痛點就是:CoWoS封裝散熱

CoWoS產能狂飆下的隱憂:當封裝“量變”遭遇檢測“質控”瓶頸

先進封裝市場迎來EMIB與CoWoS的格局之爭

CoWoS產能狂飆的背后:異質集成芯片的“最終測試”新范式

高算力低功耗背后的半導體革新

臺積電CoWoS平臺微通道芯片封裝液冷技術的演進路線

HBM技術在CowoS封裝中的應用

CoWoP能否挑戰CoWoS的霸主地位

最近大火的CoWoP跟CoWoS、CoPoS有什么區別?

普萊信成立TCB實驗室,提供CoWoS、HBM、CPO、oDSP等從打樣到量產的支持

國產AI芯片破局:國產TCB設備首次完成CoWoS封裝工藝測試

CoWoS是什么?CoWoS有幾種變體?

CoWoS是什么?CoWoS有幾種變體?

評論