隨著高性能計算(HPC)、人工智能(AI)和大數據分析的快速發展,諸如CoWoS(芯片-晶圓-基板)等先進封裝技術對于提升計算性能和效率的重要性日益凸顯。

CoWoS技術的基本原理

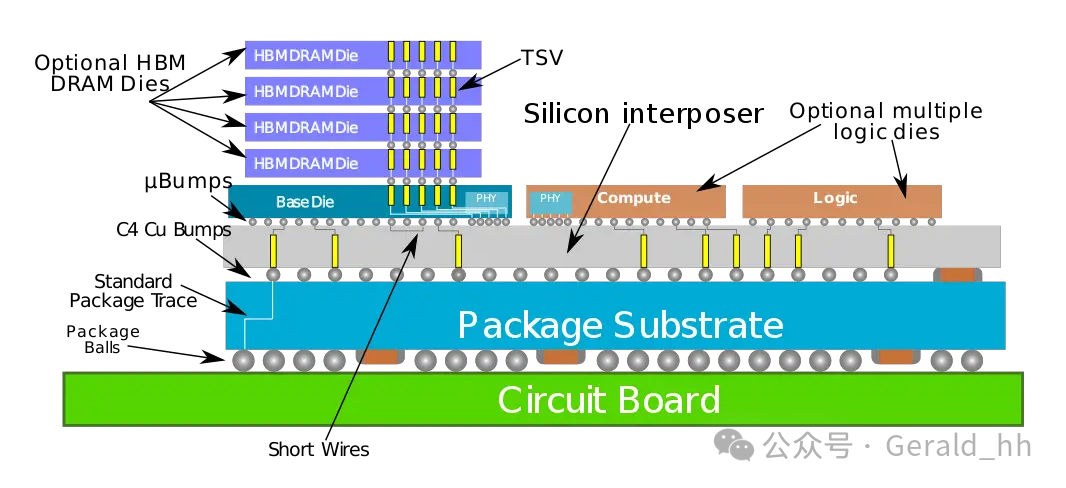

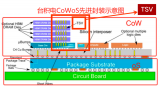

臺積電推出的CoWoS技術是一種先進的封裝技術,它將多個處理器芯片(例如SoC)直接封裝在硅中介層上。這些芯片通過中介層上的硅通孔(TSV)垂直連接,形成高度集成的系統封裝。然后,將該硅中介層集成到基板(例如PCB)上。這種方法顯著縮短了芯片之間的連接距離,提高了數據傳輸速度,降低了延遲,并提升了系統的整體性能。

CoWoS技術的關鍵在于其高度集成的封裝方式。通過將多個芯片集成在單個封裝中,CoWoS能夠提供更高的數據傳輸速率和更低的功耗,使其特別適用于高性能、高效率的計算應用,例如高性能計算(HPC)和人工智能(AI)。

CoWoS-S、CoWoS-R 和 CoWoS-L 技術簡介

CoWoS架構融合了2.5D水平堆疊和3D垂直堆疊兩種配置,徹底革新了傳統的芯片封裝模式。這種創新方法允許將各種處理器和內存模塊逐層堆疊,形成互連的芯片組,最終構成一個完整的系統。與傳統的2D封裝方法相比,CoWoS利用硅通孔(TSV)和微凸點,實現了更短的互連長度、更低的功耗和更高的信號完整性。

從實際應用角度來看,CoWoS 技術能夠將 GPU 和 AI 加速器等先進處理單元與高帶寬內存 (HBM) 模塊無縫集成。這種集成對于 AI 應用尤為重要,因為 AI 應用對強大的計算能力和快速的數據訪問速度有著極高的要求。通過將處理單元和內存單元緊密地放置在一起,CoWoS 最大限度地降低了延遲,提高了吞吐量,從而為內存密集型任務帶來了前所未有的性能提升。

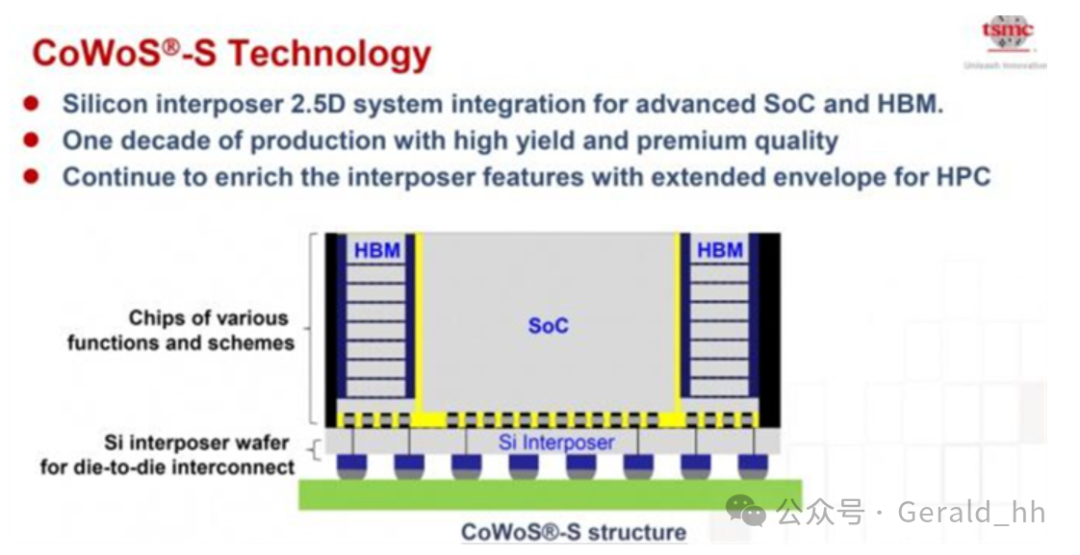

臺積電的CoWoS技術平臺包括CoWoS-S、CoWoS-R和CoWoS-L,分別針對不同的高性能計算需求進行了優化。

CoWoS-S:

CoWoS-S 是臺積電的首款 CoWoS 技術,采用單片硅中介層和硅通孔(TSV),以實現芯片和襯底之間高速電信號的直接傳輸。該技術可容納最大尺寸為光罩尺寸 3.3 倍(或約 2700mm2)的中介層,并支持多達四個 HBM2/HBM2E 內存堆疊。這種封裝方式顯著提升了高性能計算應用的性能和集成密度。

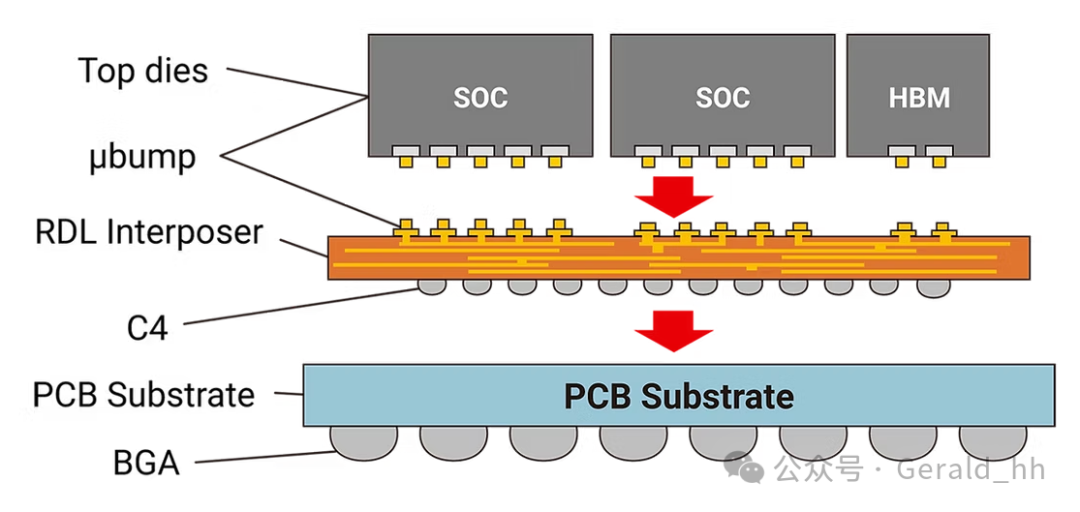

CoWoS-R:

CoWoS-R結合了臺積電的InFO技術和用于芯片連接的重分布層(RDL)中介層。用有機中介層取代了CoWoS-S中的硅中介層。該有機中介層具有細間距的RDL,可在HBM和芯片之間,甚至在芯片和基板之間提供高速連接。與CoWoS-S相比,CoWoS-R具有更高的可靠性和良率,因為有機中介層本身具有柔性,可以起到應力緩沖作用,從而緩解因基板和中介層熱膨脹系數不匹配而導致的可靠性問題。

RDL interposer:重分配層 (RDL) 用于重新分配芯片與封裝基板之間的電氣連接。RDL 通常由聚合物材料和銅線構成,將芯片的輸入/輸出 (I/O) 信號重新分配到封裝觸點。這使其具有出色的機械柔韌性和電氣性能,能夠處理高密度互連并確保信號完整性。重分配層 (RDL) 用于重新分配芯片與封裝基板之間的電氣連接。RDL 通常由聚合物材料和銅線構成,將芯片的輸入/輸出 (I/O) 信號重新分配到封裝的各個觸點。這使其具有出色的機械柔韌性和電氣性能,能夠處理高密度互連并確保信號完整性。

C4 bump:這些連接通過 RDL 層連接不同的芯片和高帶寬存儲器 (HBM),提供穩定可靠的電氣連接。這些連接點通過 RDL 層連接不同的芯片和高帶寬存儲器 (HBM),提供穩定可靠的電氣連接。

(圖片來源:臺積電)CoWoS封裝技術架構——該圖展示了CoWoS封裝技術的架構,圖中顯示了集成在同一硅中介層上的多個系統級芯片(SoC)和高帶寬內存(HBM)。這些組件通過硅通孔(TSV)連接到PCB基板。

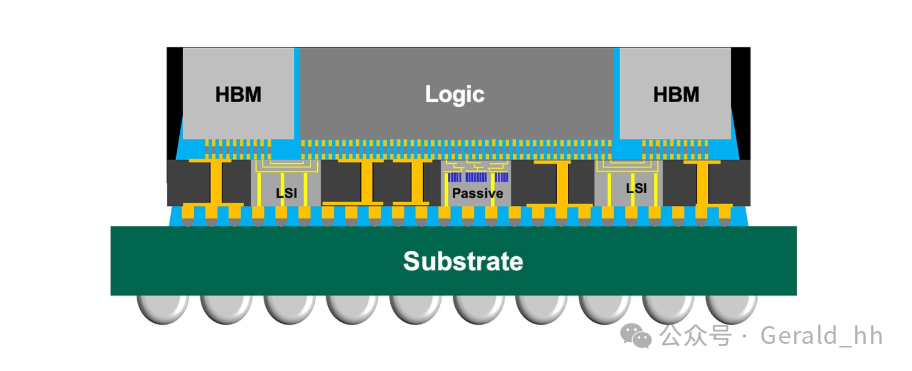

CoWoS-L:

CoWoS-L 是臺積電 CoWoS 平臺內的一種芯片后封裝技術。它結合了 CoWoS-S 和 InFO 技術的優勢,該技術采用局部硅互連(LSI)和RDL中介層,共同構成重組中介層(RI)。除了RDL中介層外,它還保留了CoWoS-S的硅通孔(TSV)這一優勢。這也有助于緩解CoWoS-S中因使用大型硅中介層而導致的良率問題。在某些實現方案中,為了最大限度地降低插入損耗,還可以使用絕緣體通孔(TIV)代替TSV。

局部硅互連(LSI):LSI 芯片用于芯片之間的高密度互連,從而實現高效的數據傳輸和低延遲。

Redistribution Layer (RDL):RDL層負責電力和信號傳輸,提供穩定可靠的電氣連接。

Packaging Structure:從 1.5 倍光掩模尺寸的中介層開始,逐步擴展以集成更多芯片,以適應各種應用需求。

(圖片來源:臺積電官網)此圖展示了CoWoS-L技術的封裝結構。圖中可見高帶寬內存(HBM)和片上系統(SoC)通過局部硅互連(LSI)芯片和重分布層(RDL)互連。這些組件最終集成到基板(PCB)上。

CoWoS-L封裝的組成部分和制造步驟:

1.CoWoS-L 是一種芯片后組裝工藝,因為首先制造中介層,然后將晶圓芯片堆疊在其上。中介層是 CoWoS 技術中的關鍵原材料之一,因為多個晶圓芯片(例如 SoC、HBM 等)都安裝在中介層上,從而實現了芯片之間的高效連接和通信。中介層制造完成后,下一步是在晶圓芯片上創建通孔絕緣通孔 (TIV)。

2.然后將已知合格的芯片(KGD)安裝到晶圓上。芯片與TIV之間的間隙用封裝材料填充,之后采用CMP工藝獲得平整的表面。

3.下一步,制造兩個RDL層。一個位于中介層正面,通過μ-bump連接晶圓和基板。第二個 RDL 位于中介層背面,通過 C4 bump連接中介層和基板。

此外,CoWoS-L技術還采用了深溝槽電容器(DTC),這種電容器具有高電容密度,可提升系統的電氣性能。這些電容器充當電荷存儲器,滿足高速計算應用運行時瞬時電流的需求。

-

臺積電

+關注

關注

44文章

5804瀏覽量

176620 -

封裝技術

+關注

關注

12文章

601瀏覽量

69317 -

CoWoS

+關注

關注

0文章

169瀏覽量

11516

原文標題:多芯片封裝技術——CoWoS@TSMC

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

臺積電第五代CoWoS封裝技術即將問世 晶圓代工優勢擴大

臺積電CoWoS訂單增加 生產線滿載運行

消息稱臺積電將CoWoS部分流程外包給OSAT

報告稱臺積電改機增CoWoS產能 預估明年倍增

曝臺積電考慮引進CoWoS技術

曝臺積電考慮引進CoWoS技術 籌劃日本建先進封裝產能

臺積電加速擴產CoWoS,云林縣成新封裝廠選址

消息稱臺積電首度釋出CoWoS封裝前段委外訂單

臺積電CoWoS產能將提升4倍

臺積電CoWoS封裝A1技術介紹

臺積電CoWoS技術的基本原理

臺積電CoWoS技術的基本原理

評論