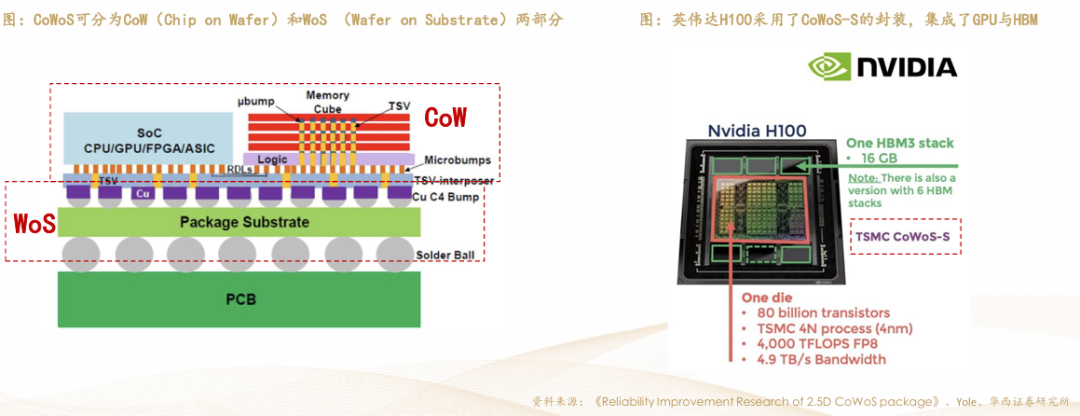

摘要:由于半導體行業(yè)體系龐大,理論知識繁雜,我們將通過多個期次和專題進行全面整理講解。本專題主要從CoWoS封裝的中階層是關鍵——SiC材料進行講解,讓大家更準確和全面的認識半導體地整個行業(yè)體系。我們分為半導體知識、半導體“芯”聞幾個模塊,歡迎各位大佬交流學習。根據(jù)《Reliability Improvement Research of 2.5D CoWoS package》,2.5D CoWoS封裝采用中介層互連技術,使用C2W(芯片到 晶圓)技術將ASIC、HBM和中介層連接為一個整體,再與基板連接,實現(xiàn)芯片、中介層和基板之間的互連。CoWoS技術旨在實現(xiàn) 更高集成度、更小封裝尺寸、更短互連路徑,以優(yōu)化線寬和間距利用,提高傳輸速率,降低損耗和延遲。 ? 根據(jù)天天IC,英偉達CEO黃仁勛在今年5月的采訪中表示,CoWoS是非常先進的技術,“在目前除了CoWoS,我們無法有其他選 擇”。

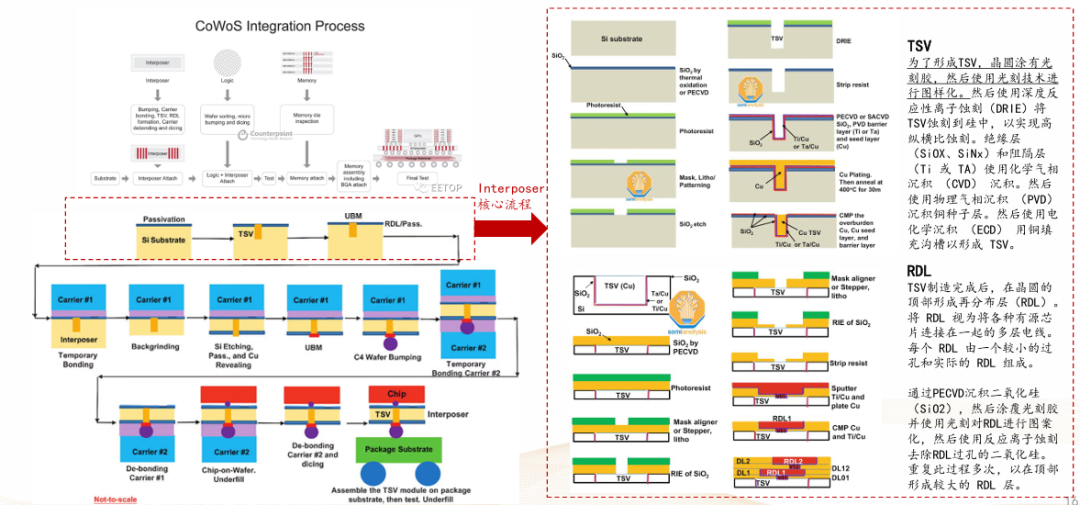

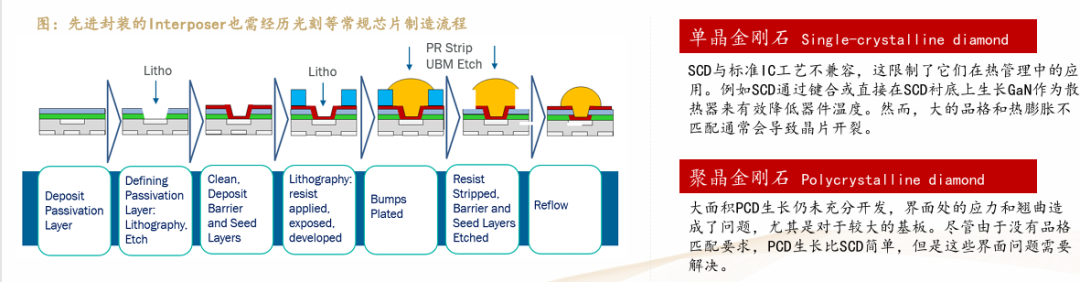

CoWoS制造流程根據(jù)Semianalysis,Interposer(中介層)的制造類似于傳統(tǒng)的前端晶圓制造。

CoWoS核心價值在于interposer(中介層)的連通作用根據(jù)廣電計量,CoWoS是由Chip on Wafer on Substrate縮寫而來,即先將各主芯片和儲存器集成堆疊到無源的Wafer(中介層) 上,再將CoW部分封裝在有機載板Substrate上。 Interposer上的RDL使得各芯片之間的電信號可以直接交流,并通過Interposer中的硅通孔(TSV)傳輸?shù)接袡C載板以完成與外界的 連接。這種封裝形式具有以下優(yōu)點:

1、減小器件所占用的面積,充分利用縱向空間,降低功耗; 2、縮短各芯片之間的電信號傳輸距離,減少導線寄生電容的影響。

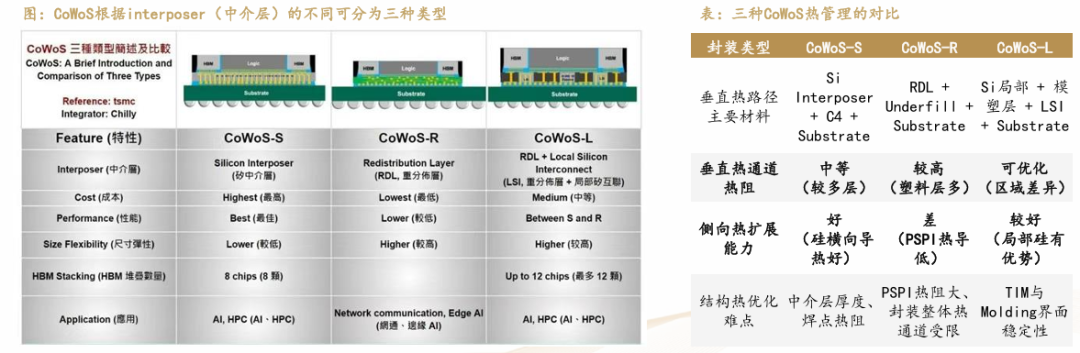

CoWoS核心在于interposer,目前可劃分為S、R、L三種類型根據(jù)洞見熱管理,CoWoS技術根據(jù)中介層所采用的材料不同,可分為CoWoS-S(硅中介層)、CoWoS-R(RDL重布線)和 CoWoS-L(LSI,重布線+部分硅中介層)三種類型。隨著CoWoS封裝在高性能計算(HPC)芯片上的廣泛應用,其熱管理問題正成為影響系統(tǒng)穩(wěn)定性和性能釋放的關鍵瓶頸。與傳統(tǒng)封 裝結構相比,CoWoS具備更高的集成密度和更復雜的堆疊結構,熱流通路不再是單一方向的導熱,而是需要穿越多個功能層、封裝 材料和界面接觸面。熱路徑中任何一層導熱性能的不匹配,都可能導致局部熱點、熱阻疊加,進而限制芯片頻率提升與長期可靠性。

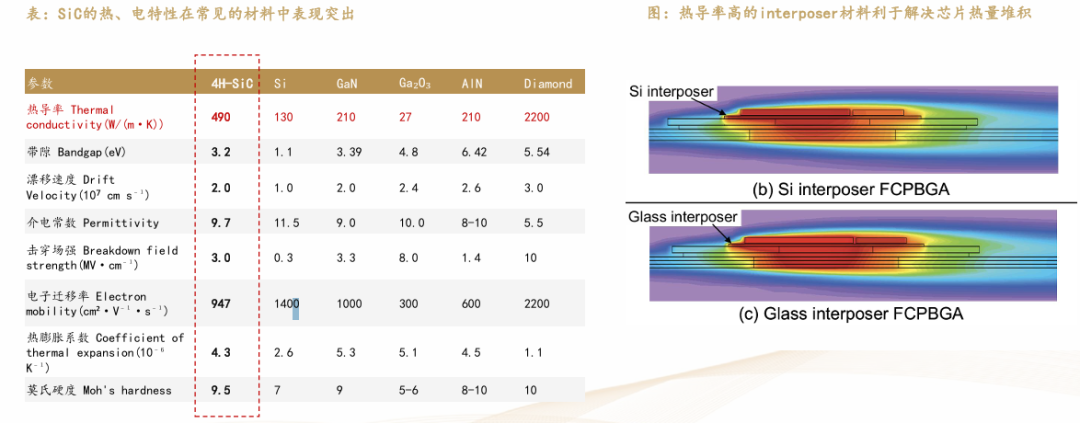

三種CoWoS熱管理的特點CoWos-S:上行為散熱路徑:SoC頂部通過TIM與外部散熱器/蓋板連接,是主要熱釋放方 向; 下行路徑中Si Interposer為硅材質,有較高熱導率(約100-150 W/mK),但其 橫向擴展面積較大,有一定散熱作用,但熱量最終還是需穿越多個熱阻層(C4 bump、基板、焊料球)傳至PCB;CoWoS-S結構下熱路徑較長、層級較多,每層 材料(如NCF、Underfill)均有熱阻積累。 CoWos-R:去除了Si Interposer,減少了一個導熱界面。RDL重布線層通常由聚酰亞胺 /PSPI與銅層構成,熱導率遠低于硅中介層(PSPI約0.3~0.5 W/m·K),成為熱 瓶頸之一。此結構封裝更輕薄、更經(jīng)濟,但熱通道變窄、熱擴展路徑受限,適 合中等功率芯片或結合主動散熱手段(如金屬蓋板/VC等)進行優(yōu)化。CoWos-L :采用混合結構,將Si Interposer與RDL結合,局部引入硅中介層提升熱導性, 同時通過模塑封裝加強結構穩(wěn)定性。LSI區(qū)塊內(nèi)部集成被動器件(IPD),可能 引入一定發(fā)熱,同時也會形成熱阻點。優(yōu)點是兼顧熱性能與良率,可進行定制 化熱優(yōu)化。對TIM、模塑材料(Molding)與Underfill提出更高熱傳導與可靠性 要求。Interposer的材料選擇對芯片散熱起到重要作用根據(jù)IBM的測試,玻璃中介層FCPBGA的邏輯芯片溫度比硅中介層FCPBGA高約14℃,這僅僅是因為玻璃中介層的熱導率較低。可 以看到熱量在封裝芯片中四處發(fā)散,在同等條件下熱導系數(shù)更低的interposer材質,能使整體溫度更低。

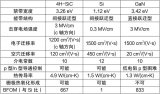

SiC用作Interposer的熱性能有望高于現(xiàn)有的硅和玻璃

根據(jù)北京大學的相關論文,其制備的熱管interposer在散熱性能上顯著優(yōu)于硅與玻璃,證明了SiC襯底作為大功率器件散熱主題材料 的潛力。雖然和CoWoS的interposer有差異,但從側面驗證了SiC在作為CoWoS中interposer的性能與可行性。

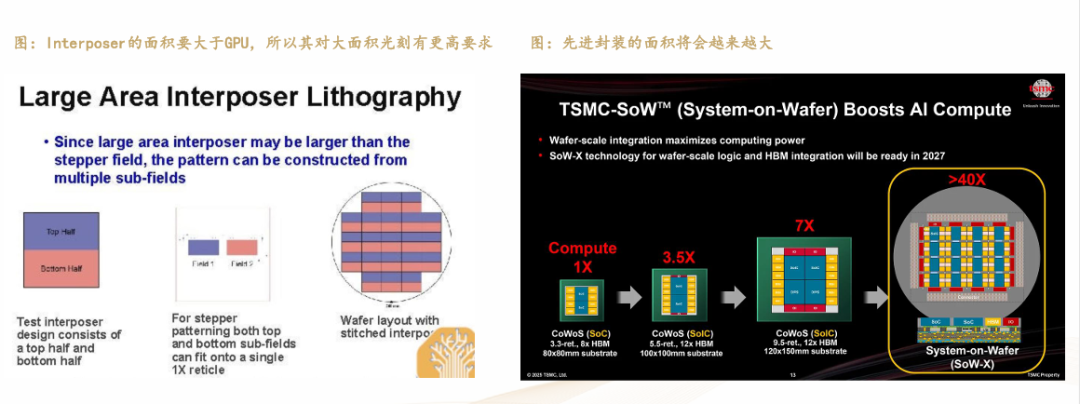

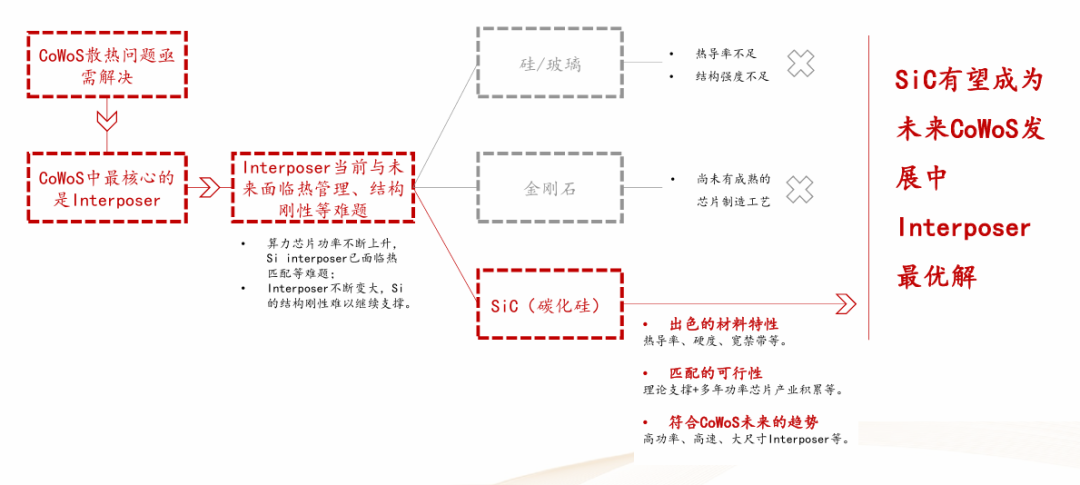

隨著Interposer的變大,CoWoS的硅中介層還面臨開裂等難題 金剛石仍難以匹配芯片制造工藝,使其目前還難以成為Interposer的選擇根據(jù)Nature 25年8月新文章,金剛石無論是單晶或是多晶,在IC散熱領域應用仍存在較多可行性問題。Interposer的制造需要經(jīng)歷光刻等制造工藝,且對材料的要求高。根據(jù)Semianalysis,芯片的最大尺寸通常為26 毫米x 33 毫米, 因為光刻工具的狹縫/掃描將該尺寸最大化。由于僅GPU 芯片就接近這個限制,并且還需要將HBM 安裝在它周圍,因此中介層需 要很大。未來的先進封裝對光刻等制造工藝還提出了更高要求。根據(jù)Veeco,未來五年內(nèi)互連密度要求不斷提高,將推動對更小線路/空間要 求的需求。這些要求正在影響用于創(chuàng)建先進封裝結構的封裝技術。特別是,光刻和相關的濕法工藝在整個工藝領域都面臨著挑戰(zhàn), 從凸塊、柱子和RDL 到貫穿硅通孔(TSV)、中介層和混合鍵合。 ?因此我們認為在金剛石在尚未能解決芯片制造(如光刻、刻蝕、鍍膜等)的基本要求之前,還難以成為interposer的選項.

金剛石仍難以匹配芯片制造工藝,使其目前還難以成為Interposer的選擇根據(jù)Nature 25年8月新文章,金剛石無論是單晶或是多晶,在IC散熱領域應用仍存在較多可行性問題。Interposer的制造需要經(jīng)歷光刻等制造工藝,且對材料的要求高。根據(jù)Semianalysis,芯片的最大尺寸通常為26 毫米x 33 毫米, 因為光刻工具的狹縫/掃描將該尺寸最大化。由于僅GPU 芯片就接近這個限制,并且還需要將HBM 安裝在它周圍,因此中介層需 要很大。未來的先進封裝對光刻等制造工藝還提出了更高要求。根據(jù)Veeco,未來五年內(nèi)互連密度要求不斷提高,將推動對更小線路/空間要 求的需求。這些要求正在影響用于創(chuàng)建先進封裝結構的封裝技術。特別是,光刻和相關的濕法工藝在整個工藝領域都面臨著挑戰(zhàn), 從凸塊、柱子和RDL 到貫穿硅通孔(TSV)、中介層和混合鍵合。 ?因此我們認為在金剛石在尚未能解決芯片制造(如光刻、刻蝕、鍍膜等)的基本要求之前,還難以成為interposer的選項.

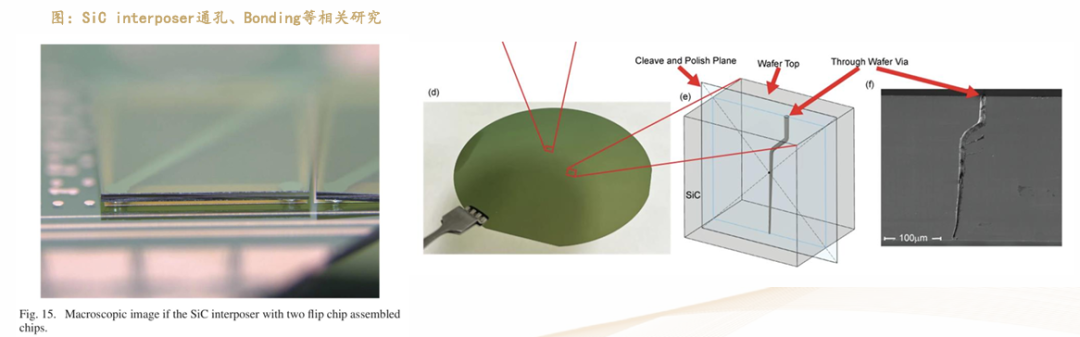

SiC成為解決Interposer痛點的重要方向根據(jù)Semivision,芯片的內(nèi)部熱路徑涉及多層——硅襯底、金屬互連、微凸塊、底部填充、熱界面材料(TIM)等。由于這些分層 的熱界面,熱量無法100% 有效地傳遞到蓋子上,從而導致局部“熱點”。這種累積熱阻是限制芯片最大功率輸出的主要因素之 一。提高熱傳導效率第一個關鍵在于縮短熱路徑并降低每層的界面熱阻,并結合引入高導熱材料,例如:SiC 襯底等。 ? 近些年Piotr Mackowiak、Jared E. Payne等團隊已在SiC的interposer上做了通孔、Bonding等相關研究,我們認為SiC用于先進封裝 領域的interposer做了較好的理論指導,結合SiC產(chǎn)業(yè)鏈在功率器件領域多年的芯片制造經(jīng)驗,SiC作為CoWoS的Si interposer未來替 代者已具備一定的理論和產(chǎn)業(yè)基礎。

SiC在散熱和結構強度等關鍵指標上優(yōu)于當前的Si材質根據(jù)Semisam,英偉達和臺積電要嘗試開發(fā)SiC襯底主要有兩個原因:一是散熱,僅HBM 產(chǎn)生的熱量就很大,GPU 本身也會產(chǎn)生 大量熱量。所需的熱規(guī)格已經(jīng)變得如此苛刻,以至于傳統(tǒng)的硅中介層已經(jīng)達到了極限;二是其非凡的強度,與易碎的玻璃基板不同, SiC 的堅固性要高得多。

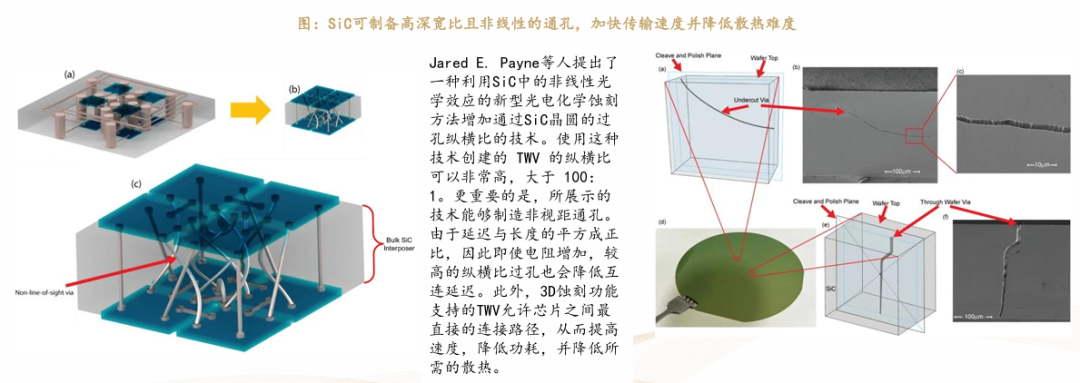

SiC通孔有望實現(xiàn)高深寬比,進一步契合先進封裝未來高速、降溫方向根據(jù)Nature,3D 集成涉及使用具有導電晶圓通孔(TWV)的中介層芯片,該芯片集成了兩個或多個小芯片。這些小芯片可以連接 到中介層的同一側和/或不同側。TWV 提供小芯片之間的電氣互連。為了實現(xiàn)高性能,小芯片之間需要高密度的互連。中介層中 TWV 密度的極限由TWV 的最大縱橫比決定,許多高縱橫比通孔研究都使用硅作為其TWV 襯底。然而,由于連接的小芯片會產(chǎn)生 大量熱量,因此需要具有高導熱性的中介層來實現(xiàn)高性能。單晶碳化硅(SiC)是一種具有高導熱性的半導體,這種屬性可提供高 散熱性。

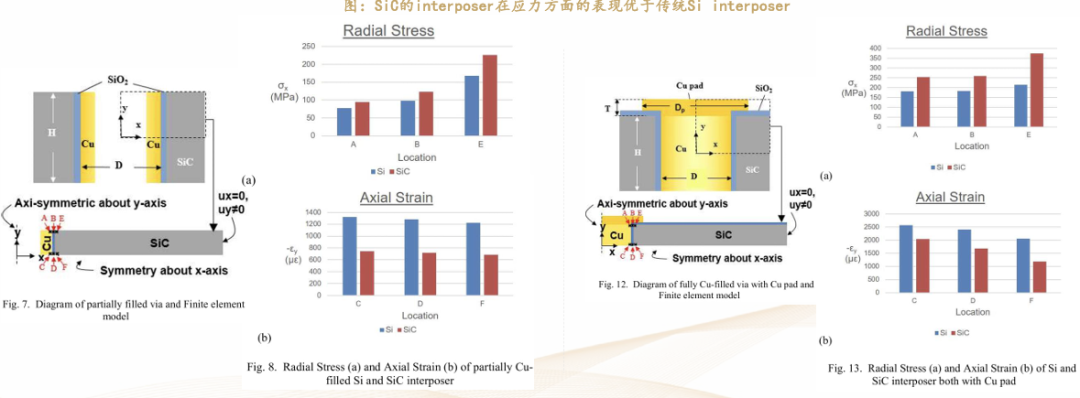

SiC在結構強度上也勝于Si,減少此前開裂、翹曲等問題根據(jù)Semivision,在 CoWoS-S 中,硅中介層與TSV 相結合可提供出色的信號和電源完整性。然而,一旦中介層尺寸超過光罩邊界, 產(chǎn)量和機械脆性風險就會急劇上升。臺積電正在探索使用單晶碳化硅(SiC)作為中介層或襯底,旨在利用SiC卓越的導熱性和機械 堅固性來增強散熱和可靠性,同時克服硅中介層固有的尺寸和材料限制。 ? 根據(jù)《Nonlinear Thermal Stress/Strain Analyses of Through SiC Via》,SiC中介層在界面處比硅中介層具有更高徑向應力和更小 軸向應變。

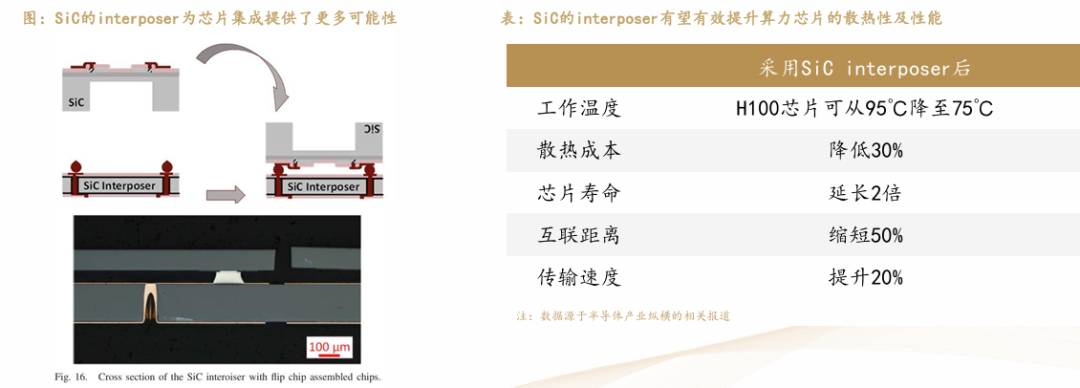

SiC在Interposer上的應用有望進一步擴展未來先進封裝的性能邊界根據(jù)Piotr Mackowiak等人的論文,介紹了碳化硅(SiC)干法蝕刻工藝的開發(fā)與優(yōu)化主要成果,研究成果應用于開發(fā)200μm厚帶銅 金屬化的SiC中介層,所開發(fā)的蝕刻技術利用了SiC優(yōu)異的電學和機械性能,為寬禁帶襯底的3D集成提供了多種應用可能。 ?根據(jù)半導體產(chǎn)業(yè)縱橫,SiC中介層的優(yōu)勢十分顯著:熱導率達490W/mK(是硅的3倍以上),熱膨脹系數(shù)(4.3ppm/℃)與芯片材料 高度契合,既能高效散熱,又能保障封裝穩(wěn)定性。

SiC有望成為未來CoWoS發(fā)展中Interposer最優(yōu)解 本文部分內(nèi)容引自華西證券研究所

本文部分內(nèi)容引自華西證券研究所

-

材料

+關注

關注

3文章

1572瀏覽量

28688 -

SiC

+關注

關注

32文章

3834瀏覽量

69958 -

CoWoS

+關注

關注

0文章

170瀏覽量

11532

發(fā)布評論請先 登錄

如何區(qū)分Info與CoWoS封裝?

金屬封裝材料的現(xiàn)狀及發(fā)展(下)

SiC功率器件的封裝技術研究

GaN和SiC區(qū)別

如何區(qū)分Info封裝與CoWoS封裝呢?

CoWoS先進封裝是什么?

什么是 CoWoS 封裝技術?

什么是CoWoS封裝技術?

華立搭乘CoWoS擴產(chǎn)快車,封裝材料業(yè)績預翻倍

IGBT和SiC封裝用的環(huán)氧材料

CoWoS先進封裝技術介紹

HBM技術在CowoS封裝中的應用

CoWoS(Chip-on-Wafer-on-Substrate)先進封裝工藝的材料全景圖及國產(chǎn)替代進展

【深度報告】CoWoS封裝的中階層是關鍵——SiC材料

【深度報告】CoWoS封裝的中階層是關鍵——SiC材料

評論