電子發燒友網綜合報道

當谷歌憑借TPU芯片與Gemini 3模型加冕AI新王,算力領域的技術迭代正引發連鎖反應。作為高效能運算的核心配套,先進封裝技術市場正經歷前所未有的變革,英特爾推出的EMIB技術悄然崛起,向長期占據主導地位的臺積電CoWoS方案發起挑戰,一場關乎AI產業成本與效率的技術博弈已然拉開序幕。

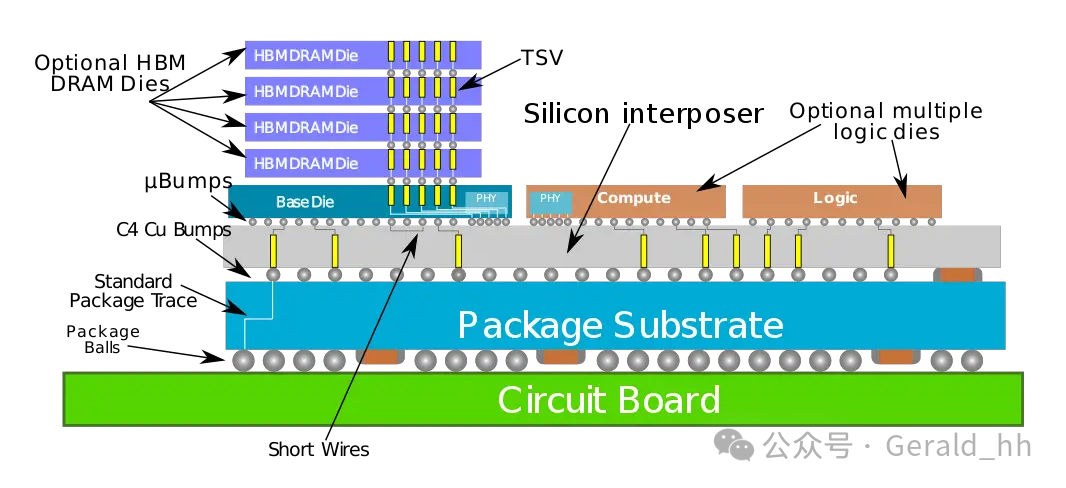

在AI算力需求呈指數級增長的當下,先進封裝技術成為突破芯片性能瓶頸的關鍵。臺積電的CoWoS技術歷經十余年迭代,憑借成熟的工藝和出色的傳輸性能,長期壟斷高端市場。

英偉達、AMD等GPU巨頭對帶寬、傳輸速度及低延遲的極致追求,使其成為CoWoS方案的核心擁躉,英偉達一家便占據了CoWoS超過60%的產能。英偉達CEO黃仁勛曾明確表示,CoWoS是當前最先進的封裝技術,公司目前沒有替代選擇,這一表態也印證了CoWoS在高性能計算領域的核心地位。

然而,AI產業的爆發式增長讓CoWoS的短板日益凸顯,產能短缺成為制約行業發展的關鍵瓶頸。今年10月臺積電坦言,AI應用仍處于早期階段,相關產能極度緊張,雖計劃在2026年提升CoWoS產能,但短期內供需矛盾難以緩解。

與此同時,CoWoS內部大中介層帶來的高昂成本,以及光罩尺寸的限制,讓不少中小型客戶望而卻步,為市場變革埋下了伏筆。

就在CoWoS面臨發展困境之際,英特爾的EMIB技術憑借精準的定位迅速獲得市場關注。作為一種2.5D先進封裝技術,EMIB最大的優勢在于面積靈活性與成本控制。與CoWoS-S僅3.3倍、CoWoS-L當前3.5倍的光罩尺寸相比,EMIB-M已能提供6倍光罩尺寸,預計2026至2027年可進一步拓展至8倍至12倍,遠超CoWoS的發展上限。

在成本方面,EMIB舍棄了價格高昂的中介層,采用將芯片內嵌在載板硅橋的方式實現互連,簡化了整體結構,為對成本敏感的AI客戶提供了更具性價比的選擇。這一技術特性恰好契合了以谷歌為代表的ASIC方案崛起的市場趨勢,有機構指出,谷歌已構建起成熟的訓推一體ASIC體系,其Gemini 3模型依托TPU集群完成訓練,下一代Ironwood(TPU v7)芯片更展現了大規模低功耗推理的工程化優勢。

受此帶動,谷歌計劃在2027年的TPU v9中導入EMIB試用,Meta也在積極評估將其應用于MTIA產品,市場對ASIC芯片的關注度持續升溫。

ASIC方案的爆發預期成為EMIB技術普及的核心推力。Wedbush Securities的Dan Ives觀察到,市場正在重新發現ASIC芯片的巨大潛力,多家機構研判,2026至2027年,谷歌、亞馬遜、Meta、Open AI及微軟的ASIC 芯片數量將迎來爆發式增長。

云端服務業者加速自研ASIC的過程中,對整合復雜功能的芯片封裝面積需求不斷擴大,臺積電CoWoS的產能限制與成本壓力,讓英特爾EMIB成為理想替代方案。除了谷歌、Meta,蘋果在DRAM封裝工程師招聘中明確要求具備EMIB技術經驗,高通為數據中心業務招聘的產品管理總監職位也將EMIB技術列為必備技能,美滿電子、聯發科等廠商更是考慮為ASIC項目導入EMIB封裝,一場由頭部企業引領的技術遷移正在悄然發生。

不過,EMIB想要完全撼動CoWoS的地位仍面臨挑戰。Trendforce指出,EMIB技術受限于硅橋面積與布線密度,在互連帶寬、訊號傳輸距離和延遲性方面存在短板,目前僅能滿足ASIC客戶的需求。對于英偉達、AMD等對性能要求極致的GPU供應商而言,CoWoS仍是不可替代的選擇。這意味著未來先進封裝市場或將呈現雙雄并立的格局,CoWoS繼續主導高性能GPU領域,而EMIB則在ASIC市場快速擴張,兩者根據不同應用場景形成互補。

當谷歌憑借TPU芯片與Gemini 3模型加冕AI新王,算力領域的技術迭代正引發連鎖反應。作為高效能運算的核心配套,先進封裝技術市場正經歷前所未有的變革,英特爾推出的EMIB技術悄然崛起,向長期占據主導地位的臺積電CoWoS方案發起挑戰,一場關乎AI產業成本與效率的技術博弈已然拉開序幕。

在AI算力需求呈指數級增長的當下,先進封裝技術成為突破芯片性能瓶頸的關鍵。臺積電的CoWoS技術歷經十余年迭代,憑借成熟的工藝和出色的傳輸性能,長期壟斷高端市場。

英偉達、AMD等GPU巨頭對帶寬、傳輸速度及低延遲的極致追求,使其成為CoWoS方案的核心擁躉,英偉達一家便占據了CoWoS超過60%的產能。英偉達CEO黃仁勛曾明確表示,CoWoS是當前最先進的封裝技術,公司目前沒有替代選擇,這一表態也印證了CoWoS在高性能計算領域的核心地位。

然而,AI產業的爆發式增長讓CoWoS的短板日益凸顯,產能短缺成為制約行業發展的關鍵瓶頸。今年10月臺積電坦言,AI應用仍處于早期階段,相關產能極度緊張,雖計劃在2026年提升CoWoS產能,但短期內供需矛盾難以緩解。

與此同時,CoWoS內部大中介層帶來的高昂成本,以及光罩尺寸的限制,讓不少中小型客戶望而卻步,為市場變革埋下了伏筆。

就在CoWoS面臨發展困境之際,英特爾的EMIB技術憑借精準的定位迅速獲得市場關注。作為一種2.5D先進封裝技術,EMIB最大的優勢在于面積靈活性與成本控制。與CoWoS-S僅3.3倍、CoWoS-L當前3.5倍的光罩尺寸相比,EMIB-M已能提供6倍光罩尺寸,預計2026至2027年可進一步拓展至8倍至12倍,遠超CoWoS的發展上限。

在成本方面,EMIB舍棄了價格高昂的中介層,采用將芯片內嵌在載板硅橋的方式實現互連,簡化了整體結構,為對成本敏感的AI客戶提供了更具性價比的選擇。這一技術特性恰好契合了以谷歌為代表的ASIC方案崛起的市場趨勢,有機構指出,谷歌已構建起成熟的訓推一體ASIC體系,其Gemini 3模型依托TPU集群完成訓練,下一代Ironwood(TPU v7)芯片更展現了大規模低功耗推理的工程化優勢。

受此帶動,谷歌計劃在2027年的TPU v9中導入EMIB試用,Meta也在積極評估將其應用于MTIA產品,市場對ASIC芯片的關注度持續升溫。

ASIC方案的爆發預期成為EMIB技術普及的核心推力。Wedbush Securities的Dan Ives觀察到,市場正在重新發現ASIC芯片的巨大潛力,多家機構研判,2026至2027年,谷歌、亞馬遜、Meta、Open AI及微軟的ASIC 芯片數量將迎來爆發式增長。

云端服務業者加速自研ASIC的過程中,對整合復雜功能的芯片封裝面積需求不斷擴大,臺積電CoWoS的產能限制與成本壓力,讓英特爾EMIB成為理想替代方案。除了谷歌、Meta,蘋果在DRAM封裝工程師招聘中明確要求具備EMIB技術經驗,高通為數據中心業務招聘的產品管理總監職位也將EMIB技術列為必備技能,美滿電子、聯發科等廠商更是考慮為ASIC項目導入EMIB封裝,一場由頭部企業引領的技術遷移正在悄然發生。

不過,EMIB想要完全撼動CoWoS的地位仍面臨挑戰。Trendforce指出,EMIB技術受限于硅橋面積與布線密度,在互連帶寬、訊號傳輸距離和延遲性方面存在短板,目前僅能滿足ASIC客戶的需求。對于英偉達、AMD等對性能要求極致的GPU供應商而言,CoWoS仍是不可替代的選擇。這意味著未來先進封裝市場或將呈現雙雄并立的格局,CoWoS繼續主導高性能GPU領域,而EMIB則在ASIC市場快速擴張,兩者根據不同應用場景形成互補。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

CoWoS

+關注

關注

0文章

170瀏覽量

11524 -

EMIB

+關注

關注

0文章

15瀏覽量

4060 -

先進封裝

+關注

關注

2文章

553瀏覽量

1051

發布評論請先 登錄

相關推薦

熱點推薦

CoWoS(Chip-on-Wafer-on-Substrate)先進封裝工藝的材料全景圖及國產替代進展

這張圖是CoWoS(Chip-on-Wafer-on-Substrate)先進封裝工藝的材料全景圖,清晰展示了從底層基板到頂層芯片的全鏈條材料體系,以及各環節的全球核心供應商。下面我們分層拆解:一

2026年AI芯片破局指南:晶圓廠不再是瓶頸,先進封裝才是核心勝負手

2026年初,全球半導體產業迎來了一個標志性的拐點:臺積電CoWoS先進封裝產能缺口超過30%,日月光等行業巨頭宣布封裝服務全線漲價30%,

【深度報告】CoWoS封裝的中階層是關鍵——SiC材料

摘要:由于半導體行業體系龐大,理論知識繁雜,我們將通過多個期次和專題進行全面整理講解。本專題主要從CoWoS封裝的中階層是關鍵——SiC材料進行講解,讓大家更準確和全面的認識半導體地整個行業體系

CoWoS產能狂飆下的隱憂:當封裝“量變”遭遇檢測“質控”瓶頸

先進封裝競賽中,CoWoS 產能與封測低毛利的反差,凸顯檢測測試的關鍵地位。2.5D/3D 技術帶來三維缺陷風險,傳統檢測失效,面臨光學透視量化、電性隔離定位及效率成本博弈三大挑戰。解決方案在于構建

五家大廠盯上,英特爾EMIB成了?

電子發燒友網綜合報道 最近,英特爾EMIB封裝火了,在蘋果、高通、博通的招聘信息中,都指出正在招募熟悉EMIB封裝的工程師。近期還有消息稱,由于臺積電

FCCSP驅動下的半導體封裝新格局

,倒裝芯片芯片級封裝)憑借其高密度互連、優異電熱性能以及緊湊尺寸,持續在消費電子、通信、汽車電子和人工智能等多個領域發揮重要作用。 ? 如今,FCCSP不僅在技術層面不斷突破,更在全球市場格局中展現出鮮明的集中化與區域轉移趨勢,

今日看點:加速進化完成新一輪超億元融資;Arm 宣布為 Neoverse 平臺導入英偉達 NVLink Fusion 互聯

CoWoS、EMIB、SoIC和PoP等先進封裝技術經驗。而高通為其數據中心業務部門招聘的產品管理總監職位也要求熟悉英特爾的EMIB技術。

發表于 11-18 10:29

?1112次閱讀

臺積電CoWoS平臺微通道芯片封裝液冷技術的演進路線

臺積電在先進封裝技術,特別是CoWoS(Chip on Wafer on Substrate)平臺上的微通道芯片液冷技術路線,是其應對高性能計算和AI芯片高熱流密度挑戰的關鍵策略。本報告將基于臺積電相關的研究成果和已發表文獻,深

HBM技術在CowoS封裝中的應用

HBM通過使用3D堆疊技術,將多個DRAM(動態隨機存取存儲器)芯片堆疊在一起,并通過硅通孔(TSV,Through-Silicon Via)進行連接,從而實現高帶寬和低功耗的特點。HBM的應用中,CowoS(Chip on Wafer on Substrate)封裝技術

化圓為方,臺積電整合推出最先進CoPoS半導體封裝

電子發燒友網綜合報道 近日,據報道,臺積電將持續推進先進封裝技術,正式整合CoWoS與FOPLP,推出新一代CoPoS工藝。 ? 作為臺積電先進封裝

CoWoP能否挑戰CoWoS的霸主地位

在半導體行業追逐更高算力、更低成本的賽道上,先進封裝技術成了關鍵突破口。過去幾年,臺積電的CoWoS(Chip-on-Wafer-on-Substrate)技術憑借對AI芯片需求的精準適配,成了

從InFO-MS到InFO_SoW的先進封裝技術

在先進封裝技術向超大型、晶圓級系統集成深化演進的過程中,InFO 系列(InFO-MS、InFO-3DMS)與 CoWoS-L、InFO_SoW 等技術持續突破創新。

120×180mm怪獸封裝!EMIB-T讓AI芯片起飛

EMIB技術基礎上引入硅通孔(TSV)的重大升級,旨在解決高性能計算、AI加速器和數據中心芯片的異構集成挑戰。其核心是通過垂直互連提升封裝密度和性能,同時降低功耗和延遲。 ? 傳統EMIB利用嵌入在

英特爾先進封裝,新突破

了英特爾在技術研發上的深厚底蘊,也為其在先進封裝市場贏得了新的競爭優勢。 英特爾此次的重大突破之一是 EMIB-T 技術。EMIB-T 全稱

先進封裝市場迎來EMIB與CoWoS的格局之爭

先進封裝市場迎來EMIB與CoWoS的格局之爭

評論