文章來源:學習那些事

原文作者:小陳婆婆

本文主要講述3D封裝與CoWoS封裝。

集成扇出(InFO)

自戈登·摩爾1965年提出晶體管數(shù)量每18-24個月翻倍的預言以來,摩爾定律已持續(xù)推動半導體技術跨越半個世紀,從CPU、GPU到專用加速器均受益于此。

如今這一規(guī)律正從單一晶體管縮微(1.0時代)向晶圓級系統(tǒng)集成(WLSI)的2.0時代演進——通過將超大芯片拆解為獨立功能單元,結合2D/3D封裝與硅通孔、扇出等前沿技術,在保持甚至加速晶體管密度增長的同時,實現(xiàn)性能、功耗、面積與成本(PPAC)的協(xié)同優(yōu)化。

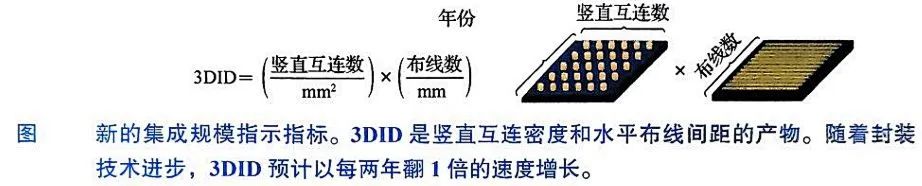

新指標3D互連密度(3DID)的提出,更量化了系統(tǒng)級封裝的擴展能力,配合SoIC等顛覆性3D集成技術,正為摩爾定律的持續(xù)生效注入新動能,開啟半導體技術指數(shù)級增長的新篇章,本文分述如下:

3D封裝和片上集成系統(tǒng)(SoIC)

CoWoS封裝

3D封裝和片上集成系統(tǒng)(SoIC)

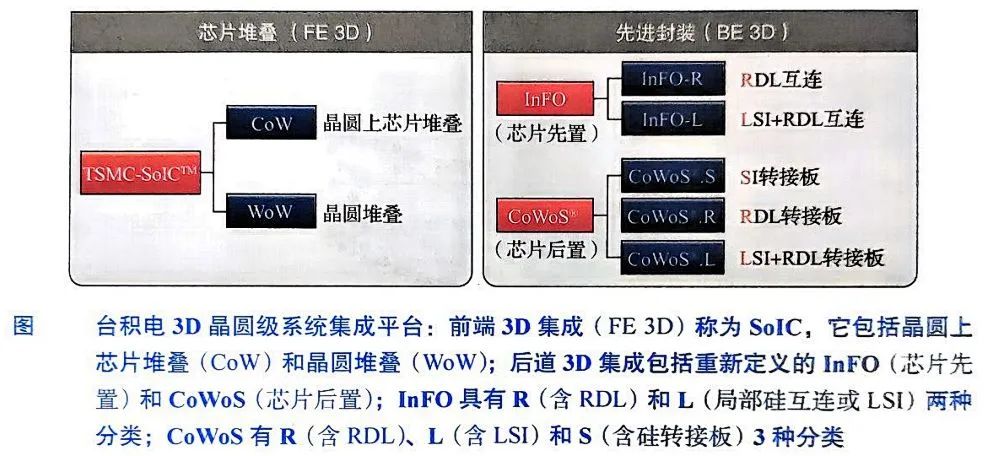

在半導體系統(tǒng)集成領域,3D Fabric技術平臺的演進正推動封裝工藝從單一互連方案向多維協(xié)同架構跨越。作為晶圓級集成技術的集大成者,3D Fabric通過整合扇出型互連(InFO)、硅轉接板集成(CoWoS)及晶圓級系統(tǒng)集成(SoW/SoIS)等模塊化工藝,構建起覆蓋前端制造與后端封裝的完整技術生態(tài)。

其中,InFO技術以芯片預嵌入為核心,通過扇出型重布線層實現(xiàn)高密度橫向擴展,其工藝流程本質(zhì)在于先固定芯片位置再構建互連網(wǎng)絡,這種"芯片先行"的策略為復雜系統(tǒng)提供了靈活的布局空間;而CoWoS則采用"再布線優(yōu)先"的逆向思維,在芯片貼裝前完成多層高密度互連結構的沉積,結合硅轉接板的垂直貫通能力,有效平衡了信號完整性與熱管理需求。

值得注意的是,實際生產(chǎn)中兩者并非非此即彼的選擇,通過混合集成模式——部分芯片采用InFO方式嵌入,其余模塊通過CoWoS實現(xiàn)精密對接——系統(tǒng)架構師得以在局部互連密度、芯片形貌適配及散熱路徑優(yōu)化間找到最佳平衡點,這種工藝組合的靈活性在異構計算時代尤為重要。

作為3D Fabric體系中的顛覆性技術,片上集成系統(tǒng)(SoIC)將前道制造工藝引入封裝領域,通過晶圓級鍵合技術實現(xiàn)多芯片的垂直堆疊與無縫集成。其核心優(yōu)勢在于,通過預先對不同工藝節(jié)點、不同材料體系的芯片進行嚴格測試(KGD篩選),確保堆疊單元的功能可靠性,再利用類似前端制程的銅互連技術(節(jié)距密度媲美后道銅布線),在微米級甚至亞微米級尺度上實現(xiàn)芯片間的等效單片化集成。這種前道與后道工藝的深度融合,不僅使SoIC集成的多芯片系統(tǒng)在電氣性能、機械穩(wěn)定性上達到傳統(tǒng)SoC水準,更通過模塊化設計大幅縮短產(chǎn)品迭代周期。當前,SoIC技術已與CoWoS、InFO等后道工藝形成技術閉環(huán),構建起從芯片級到系統(tǒng)級的多維集成解決方案。

CoWoS封裝

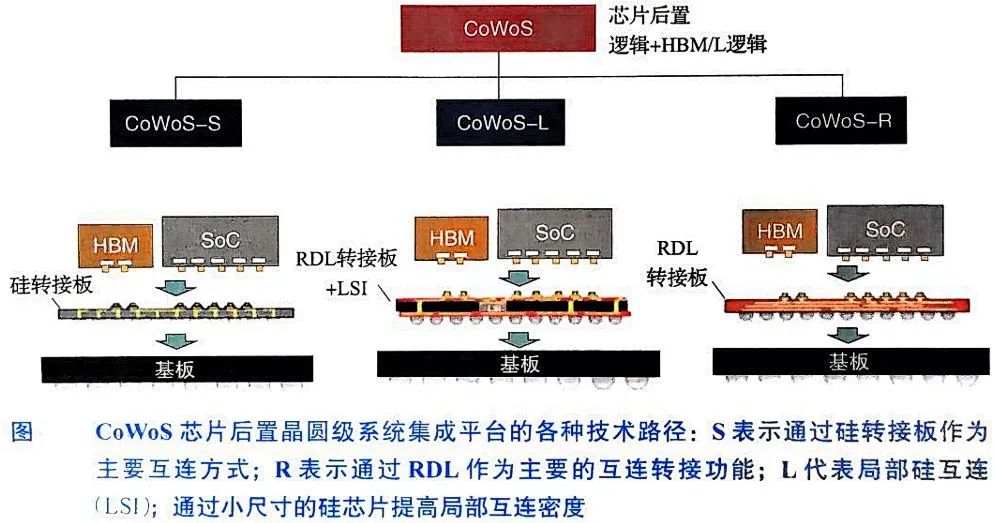

在先進封裝領域,CoWoS(Chip-on-Wafer-on-Substrate)技術平臺通過模塊化設計,構建了覆蓋高密度互連、成本優(yōu)化與異構集成需求的多維解決方案。作為芯片后置工藝的典型代表,CoWoS體系通過預布線層(RDL)與轉接板技術的深度融合,實現(xiàn)了從芯片級到系統(tǒng)級的精準性能調(diào)控。

CoWoS-S作為基礎架構,依托硅轉接板(Silicon Interposer)實現(xiàn)芯片間的高密度互連。其核心優(yōu)勢在于硅基材的高熱導率與低介電損耗特性,可支持微米級節(jié)距的TSV(硅通孔)與微凸點互連,單塊轉接板即可實現(xiàn)超過1000個I/O通道的密集走線。更值得關注的是,有源轉接板技術的引入使硅基板不再局限于被動互連角色——通過集成嵌入式電容、電感或射頻模塊,該平臺可有效縮短信號傳輸路徑,降低寄生效應對高速串行鏈路(如PCIe 5.0/6.0)的影響。據(jù)臺積電2024年技術論壇披露,其5nm CoWoS-S工藝已實現(xiàn)轉接板層數(shù)突破至8層,互連密度達每平方毫米10萬個連接點,成功支撐英偉達Hopper架構GPU與Grace CPU的異構集成。

針對成本敏感型應用,CoWoS-R平臺以RDL(重布線層)替代硅轉接板,通過有機基板上的銅布線實現(xiàn)芯片互連。盡管其線寬/線距(L/S)通常維持在2μm/2μm級別,較硅轉接板的1μm/1μm稍顯寬松,但有機基材的低成本與易加工特性使其在加速器領域獲得廣泛采用。AMD MI300系列APU即采用該技術,通過RDL層將GPU與HBM內(nèi)存垂直堆疊,在保持1.2TB/s帶寬的同時,將封裝成本降低30%。值得補充的是,三星近期公布的X-Cube 3D技術亦采用類似RDL方案,但其通過混合鍵合(Hybrid Bonding)將互連節(jié)距壓縮至4μm,在成本與性能間形成新平衡點。

在需要局部高密度的復雜系統(tǒng)中,CoWoS-L平臺通過嵌入式LSI(局部硅互連)芯片解決了傳統(tǒng)RDL的密度瓶頸。該技術將微型硅橋接片嵌入RDL層中,在特定區(qū)域實現(xiàn)亞微米級互連(如0.8μm節(jié)距),同時保留有機基板的大面積布局優(yōu)勢。英特爾在Ponte Vecchio GPU中采用的EMIB(嵌入式多芯片互連橋接)技術即屬此類,其LSI芯片通過預先植入的深溝槽電容(DTC)有效抑制電源噪聲,使多芯片系統(tǒng)在200W功耗下仍能維持1.2V的核心電壓穩(wěn)定度。行業(yè)動態(tài)顯示,臺積電正將CoWoS-L與SoIC技術結合,開發(fā)出支持3D堆疊與2.5D互連的混合架構,預計2025年量產(chǎn)的CoWoS-L Gen2工藝將實現(xiàn)LSI芯片與RDL層的無縫集成,進一步縮小先進封裝與單片SoC的性能差距。

從技術演進路徑看,CoWoS平臺正通過材料創(chuàng)新與工藝解耦持續(xù)拓展邊界。硅轉接板向玻璃基板的過渡研究已進入實操階段,玻璃基板的高平整度與超薄化特性可支持更精密的TSV制造;而RDL層與LSI芯片的協(xié)同設計,則推動封裝從被動互連向主動功能集成轉型。這些進展共同印證了先進封裝技術正在從"連接載體"演變?yōu)?系統(tǒng)賦能者",為摩爾定律的延續(xù)提供關鍵支撐。

-

半導體

+關注

關注

339文章

30892瀏覽量

265146 -

晶體管

+關注

關注

78文章

10407瀏覽量

148053 -

3D封裝

+關注

關注

9文章

149瀏覽量

28331 -

CoWoS

+關注

關注

0文章

169瀏覽量

11518

原文標題:集成扇出(InFO)應用——3D封裝與CoWoS封裝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

畫PCB 3D封裝問題

AD16的3D封裝庫問題?

X-Cube?3D 系列推進 3D 封裝工藝發(fā)展

如何區(qū)分Info封裝與CoWoS封裝呢?

淺談3D封裝與CoWoS封裝

淺談3D封裝與CoWoS封裝

評論