以下文章來源于算力冷時代圈,作者冷時代

臺積電在先進封裝技術,特別是CoWoS(Chip on Wafer on Substrate)平臺上的微通道芯片液冷技術路線,是其應對高性能計算和AI芯片高熱流密度挑戰的關鍵策略。本報告將基于臺積電相關的研究成果和已發表文獻,深入探討其微通道芯片封裝液冷技術的演進路線。

作為全球領先的晶圓代工企業,臺積電在先進封裝技術方面持續創新,其研發的CoWoS平臺,已成為集成高帶寬內存(HBM)和多個系統級芯片(SoC)的關鍵技術 。CoWoS技術雖然極大地提升了芯片的集成度和性能,但也帶來了前所未有的散熱挑戰。為此,臺積電及其生態系統伙伴積極探索并部署一系列前沿液冷解決方案,以期有效管理這些高性能芯片所產生的巨大熱量,其技術演進主要體現在以下幾個方面。

一、CoWoS平臺與芯片液冷的初期探索

(2009年前后)

CoWoS技術是臺積電開發的一種2.5D/3D堆疊異構集成封裝解決方案,通過將多個芯片集成在單一硅中介層上實現高密度互聯。

工藝流程分為兩個主要步驟:首先芯片通過Chip-on-Wafer(CoW)的方式連接到硅晶圓,隨后,將此結構與基板(Substrate)結合,形成完整的CoWoS封裝。硅中介層作為核心技術組件,利用微凸塊(μBumps)和硅通孔(TSV)替代傳統引線鍵合,顯著提升了芯片間的互聯密度和數據傳輸帶寬。

圖1:CoWoS 2.5D封裝示意圖

技術應用:該技術廣泛應用于數據中心和AI系統的HPC領域,以集成大型中介層、SoC芯片和高帶寬內存(HBM)單元。

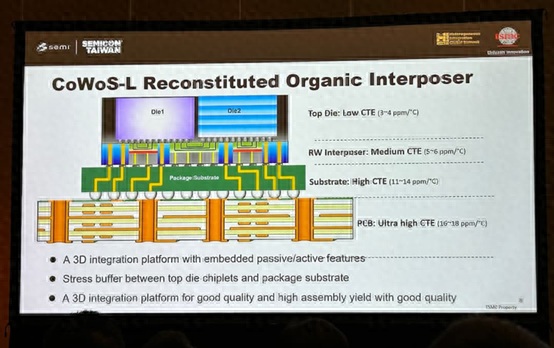

分類與演進:根據硅中介層的設計差異,臺積電將CoWoS封裝技術分為三種類型——CoWoS-S(Silicon Interposer)、CoWoS-R(RDL Interposer)以及CoWoS-L(Local Silicon Interconnect and RDL Interposer)。根據臺積電披露信息,第一個3.5倍光罩尺寸的CoWoS-L 已經開發完成,并于2024年進入生產。針對 5.5倍光罩尺寸中介層的新CoWoS-L開發已于今年開始,以滿足封裝的更高性能目標。

隨著芯片功耗的增加以及芯片內部熱點區域熱流密度達到500W/cm2以上,芯片液冷成為關鍵技術,這為后續臺積電在CoWoS平臺上集成芯片液冷方案奠定了理論基礎。

二、微通道芯片液冷的集成與驗證

2025年

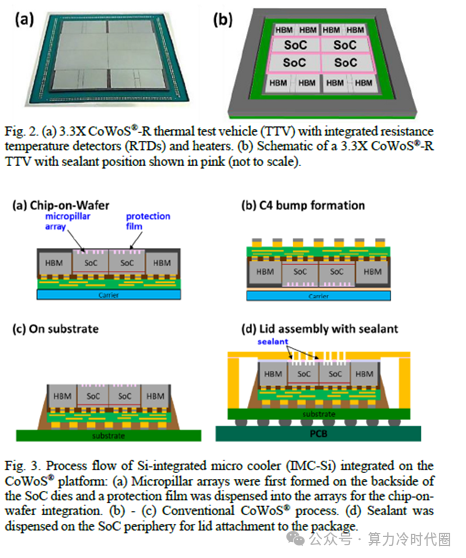

為了解決CoWoS平臺上的高功率和高功率密度散熱問題,臺積電已在2025年的研究中展示了一種芯片液冷解決方案——硅集成微通道冷卻系統(IMC-Si)。

IMC-Si 通過SoIC晶圓鍵合技術,在 SoC 芯片背面制造蛋形硅微柱陣列,冷卻液直接流經硅微柱間隙,與芯片熱源實現無 TIM 層接觸,將熱阻降低至趨近于零。陣列高度 150μm,直徑 340×220μm,形成硅集成微通道。(前文我們對微通道進行系統分析,請點擊查看微納通道冷板的技術路線及進展)該方案已在3.3X倍光罩尺寸的CoWoS-R封裝上進行了演示,其優勢在于只需對現有CoWoS工藝流程進行最小化修改。這種芯片液冷解決方案通過在硅邏輯芯片和液體歧管蓋之間點膠一種耐翹曲密封劑來形成,實現了冷卻劑與芯片的直接接觸 。

這標志著微通道芯片液冷技術從概念驗證走向實際應用的關鍵一步,為未來高性能計算和AI應用提供了強大的散熱支持。

圖2:芯片液冷在 CoWoS平臺上的集成工藝流程

三、微通道芯片液冷設計與優化

持續進行

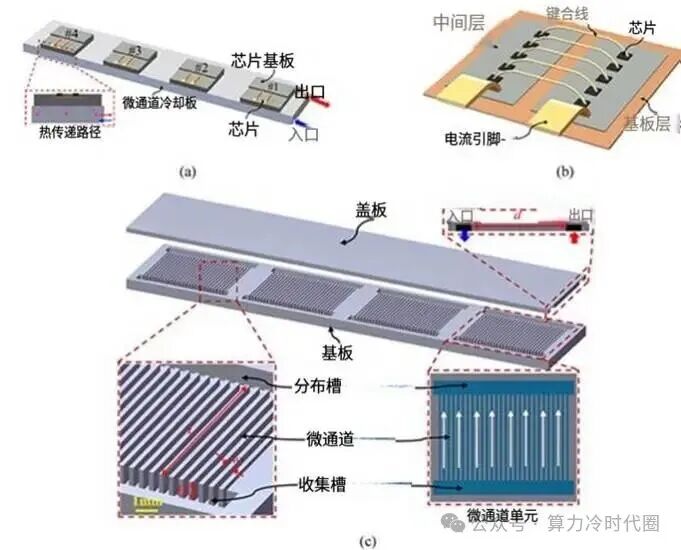

下圖展示了微通道芯片液冷的詳細技術圖,包括芯片冷卻組件的分解圖、芯片相關組件的內部結構圖以及微通道冷卻板的詳細視圖,這些都用于解釋微通道芯片液冷系統的結構和工作原理 。

圖3:微通道芯片液冷技術圖

結構多樣化:研究人員對不同結構的微通道設計進行了評估,例如微通道熱沉(MCHS)、直列微針翅熱沉(I-MPFHS)和交錯微針翅熱沉(S-MPFHS),并通過微加工和硅-硅直接鍵合技術集成到微通道芯片液冷系統中 。

多層微通道:多層微通道芯片液冷已被提出用于4x4芯片陣列的散熱,其熱流密度可達500W/cm2 。

變截面通道:為了進一步優化流動和傳熱性能,研究人員還提出了可變截面微通道液冷板的設計,以解決服務器芯片微通道液冷板的挑戰 。這種設計有助于優化冷卻液的流動,提高熱交換效率 。

低熱阻優化:在實驗室環境中,微通道芯片液冷已被設計和表征用于冷卻單芯片模塊(SCM)中極高功率密度的芯片,通過多個換熱區域和優化的翅片設計,實現了芯片表面與入口冷卻水之間16.2°C·mm2/W的平均單位熱阻 。在實際應用中,單相微通道液冷系統在流體壓降為0.25 MPa時,從冷卻系統表面到入口冷卻水的單位熱阻可達10.5°C·mm2/W。

四、芯片液冷封裝與多物理場耦合分析

持續進行

臺積電的微通道芯片液冷技術路線不僅關注芯片層面的冷卻,也致力于封裝到系統的整體熱解決方案。

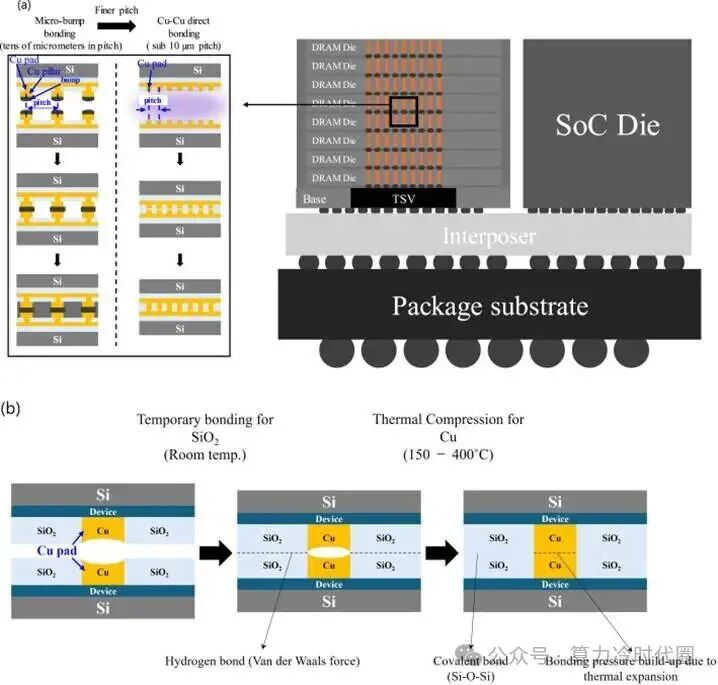

芯片板載封裝:高功率芯片模塊的芯片板載(COB)封裝通過簡化制造流程、降低支撐結構成本和提供更低的熱阻來增強散熱 。

先進鍵合技術:在先進封裝中,無凸塊銅-銅鍵合作為下一代核心技術正在興起,因為它能解決微凸點間距的限制,這對于將冷卻結構與芯片更緊密地集成至關重要 。

圖4:芯片液冷封裝結構

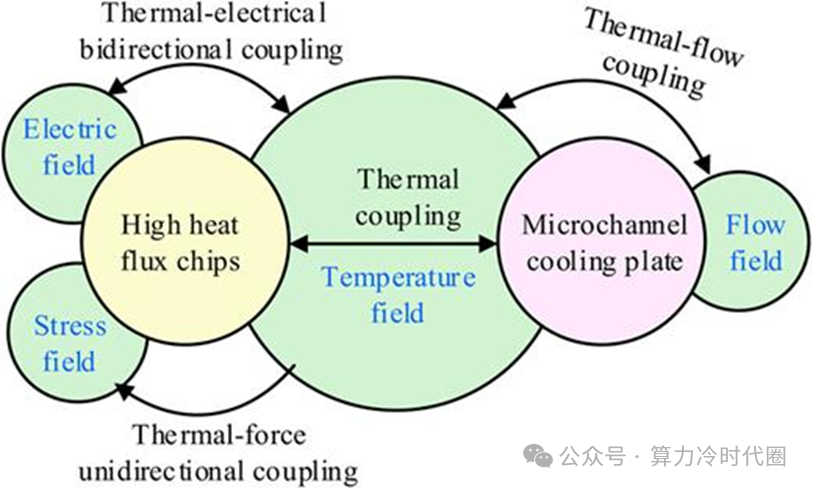

3.多物理場耦合分析:高熱流密度的微通道芯片液冷系統涉及到熱-流-力-電等多物理場耦合特性 。研究發現,芯片的焦耳熱和冷卻水流量對多場耦合效應下的冷卻性能有顯著影響,揭示了多場耦合效應的影響,并提出了增強微通道芯片液冷的方法 。

圖5:芯片液冷多物理場耦合關系圖

上圖展示了高熱流密度微通道芯片液冷系統中多場耦合關系的示意圖,包括熱-電雙向耦合、熱-流耦合以及熱-力單向耦合等。

小結

臺積電在CoWoS平臺上的微通道芯片液冷技術路線,是一個持續演進的、多方面的策略。它通過將先進的液冷解決方案,如微通道直接集成到封裝中,開發和優化芯片微通道結構等增強傳熱機制,并通過多物理場耦合分析來理解和優化冷卻系統的性能,旨在有效管理高性能計算和AI芯片產生的高熱流密度,從而確保未來高性能芯片的可靠性和持續發展 。

-

臺積電

+關注

關注

44文章

5785瀏覽量

174482 -

晶圓

+關注

關注

53文章

5336瀏覽量

131578 -

CoWoS

+關注

關注

0文章

161瀏覽量

11443

原文標題:臺積電高性能芯片熱管理:CoWoS芯片液冷技術演進路線

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

臺積電CoWoS平臺微通道芯片封裝液冷技術的演進路線

臺積電CoWoS平臺微通道芯片封裝液冷技術的演進路線

評論