圖:中國(guó)工程院院士、浙江大學(xué)微納電子學(xué)院院長(zhǎng)吳漢明

無(wú)獨(dú)有偶,6月份,在臺(tái)北電腦展上,AMD總裁兼首席執(zhí)行官蘇姿豐博士展示了全新的 3D chiplet 技術(shù),將引領(lǐng)高性能計(jì)算前沿技術(shù)突破。AMD 正在與臺(tái)積電合作開(kāi)發(fā)的第一個(gè)使用 3D 垂直緩存的芯片,蘇博士拿著一枚由 Ryzen 5900X 為原型開(kāi)發(fā)的芯片,展示這項(xiàng)技術(shù)的初步成果。

圖片來(lái)自AMD

3D堆疊技術(shù)早就用在閃存上,今天AMD把這個(gè)技術(shù)帶在CPU上,突破性將AMD芯片架構(gòu)以3D堆疊技術(shù)相結(jié)合,可以提高超過(guò)2D芯片200倍的互聯(lián)密度,與現(xiàn)有的3D封裝解決方案相比密度也可達(dá)到15倍以上。

圖片來(lái)自AMD

這塊就是采用3D堆疊技術(shù)的銳龍5900X處理器的原型設(shè)計(jì),左邊的芯片上有一塊6mm*6mm的正方形SRAM與CCD結(jié)合在一起,在擁有雙CCD的12核或16核銳龍?zhí)幚砥魃暇鸵还矒碛?92MB的L3緩存。在加入了3D垂直緩存后,12核的Zen 3銳龍?zhí)幚砥髟谕l下《戰(zhàn)爭(zhēng)機(jī)器5》的平均幀率提升了12%,整體游戲性能提升了15%。

3D Chiplet封裝技術(shù)有何魔力?這個(gè)封裝技術(shù)因何誕生?最新的進(jìn)展是怎樣的?筆者集合臺(tái)積電、日月光、長(zhǎng)電科技等芯片代工、芯片封裝領(lǐng)域的明星企業(yè)最新觀點(diǎn)和產(chǎn)品進(jìn)展,和大家做深入分析。

3D IC 時(shí)代加速到來(lái),臺(tái)積電計(jì)劃2022 年 3DFabric 專用晶圓廠正式啟用

在近期舉行的2021年技術(shù)論壇上,臺(tái)積電CEO魏家哲感嘆2021年全球數(shù)字化轉(zhuǎn)型以驚人的速度進(jìn)行,無(wú)論是辦公、教育、娛樂(lè)都需要大量高速運(yùn)算,疫情令全球更多人意識(shí)到半導(dǎo)體對(duì)全球經(jīng)濟(jì)的重要性。

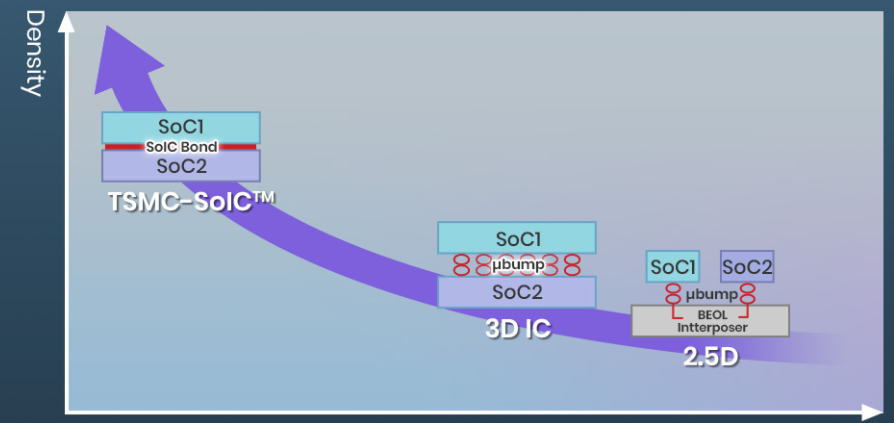

魏家哲表示,2D微縮已經(jīng)不足以支持系統(tǒng)整合需求,由于臺(tái)積電前瞻性投資和研發(fā)部門(mén)的努力,3DIC技術(shù)已經(jīng)是一條可行的道路,同時(shí)滿足系統(tǒng)效能、縮小面積以及整合不同功能的需求。

圖片來(lái)自TSMC網(wǎng)站

在AMD發(fā)布的3D chiplet背后,是臺(tái)積電的先進(jìn)半導(dǎo)體工藝技術(shù)和先進(jìn)封裝技術(shù)。在今年的ISSCC中,臺(tái)積電展示了SOIC技術(shù),這次臺(tái)積電為該技術(shù)商用起名(3DFabric),并且公布了互聯(lián)密度相關(guān)的數(shù)據(jù),其互聯(lián)密度相比傳統(tǒng)的基于bump的3DIC技術(shù)可以提升16倍,該數(shù)據(jù)與AMD這次在Computex發(fā)布的相關(guān)數(shù)字(相比3DIC互聯(lián)密度提升15倍)也大體相符。臺(tái)積電認(rèn)為,高算力芯片除了在先進(jìn)制程上推進(jìn)外,先進(jìn)的封裝技術(shù)是進(jìn)一步擴(kuò)大密度的關(guān)鍵,3D封裝技術(shù)是前進(jìn)的最佳途徑。目前,臺(tái)積電3D IC技術(shù)包括Cowos、InFO、SoIC。

臺(tái)積電業(yè)務(wù)開(kāi)發(fā)資深副總張曉強(qiáng)指出,InFO_B 封裝技術(shù)是 InFO 系列的新技術(shù),基于 InFO_PoP 多年量產(chǎn)經(jīng)驗(yàn)下,可以有效增加包裝的芯片尺寸,而這對(duì)手機(jī)產(chǎn)品非常重要。特別是對(duì)于5G移動(dòng)平臺(tái),TSMC具有InFO POP,用于移動(dòng)應(yīng)用,用于RF前端模塊(FEM)應(yīng)用的InFO Antenna-in-package(InFO_AiP)以及用于RF前端模塊(MUST)的多堆棧(MUST)、基帶調(diào)制解調(diào)器。

而InFO_oS 封裝技術(shù)的特點(diǎn),考慮主要針對(duì) HPC 應(yīng)用的封裝技術(shù),利用 InFO 把不同邏輯芯片整合起來(lái),讓 InFO 能力從一個(gè) reticle 增進(jìn)到 2.5 個(gè) reticle size,能夠在一個(gè)模塊上整合更多更大的芯片,這對(duì)未來(lái) HPC 應(yīng)用有非常積極的作用。

此外,臺(tái)積電還開(kāi)發(fā)了業(yè)界第一個(gè)高密度小芯片的堆疊技術(shù),已經(jīng)開(kāi)發(fā)了Chip-on-wafer、wafer-on-wafer兩種不同技術(shù),能夠堆疊異構(gòu)芯片和同構(gòu)芯片,大幅度提升系統(tǒng)效能,縮小產(chǎn)品尺寸。

日月光推出了晶圓級(jí) FOWLP技術(shù)

近日,在南京半導(dǎo)體大會(huì)上,日月光集團(tuán)副總經(jīng)理郭桂冠指出,隨芯片復(fù)雜度日益提升,測(cè)試更耗時(shí)、耗力,使用不同封裝技術(shù)進(jìn)行異質(zhì)芯片整合是新時(shí)代的發(fā)展趨勢(shì)。

在郭桂冠看來(lái),晶圓成本和良率是業(yè)界一直關(guān)注的焦點(diǎn)。“如果我們一律追求3納米、5納米,在良率上付出的成本極大,如果用Chiplet不需要集合成非常大的芯片,可以離散式分成幾個(gè)小芯片做整合的話,良率得以大大提高。”

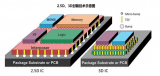

“我認(rèn)為,除了SOC單芯片之外,2.5D甚至結(jié)合2.5D、3D高性能的計(jì)算芯片,同樣SIP會(huì)帶出異質(zhì)系統(tǒng)整合的需求。9月你會(huì)看到更多的產(chǎn)品已經(jīng)應(yīng)用到扇出型就是雙層結(jié)構(gòu)SIP的概念。”郭桂冠表示,筆者在展臺(tái)也看到日月光帶來(lái)了2.5D和3D封裝的成品展示。

5G對(duì)封裝廠帶來(lái)哪些機(jī)會(huì)?郭桂冠認(rèn)為,5G不僅僅是快速傳輸,還有高效能技術(shù),這部分有更快的反應(yīng)速度,我們定義叫HPC。日月光針對(duì)SIP封裝有兩個(gè)明顯的趨勢(shì):一是從單面變成雙面,厚度會(huì)增加,厚度的增加遠(yuǎn)遠(yuǎn)超過(guò)實(shí)際應(yīng)用。蘋(píng)果厚度就是0.75,在座的手機(jī)殼厚度都遠(yuǎn)遠(yuǎn)超過(guò),這部分隨著時(shí)間演進(jìn)一方面不斷縮小;二是開(kāi)始增加很多異形鍵,可以是和外面天線連接的接觸片。好處是不用依賴基板,另外一個(gè)好處是線寬間距做得更優(yōu)化。

日月光推出了晶圓級(jí) FOWLP (Fan-out Wafer-Level Package) 技術(shù),推出面板級(jí) FOPLP (Fan-out Panel-Level Package) 的則有日月光、力成、三星等等,競(jìng)爭(zhēng)相當(dāng)激烈。

長(zhǎng)電科技兩大核心技術(shù)實(shí)現(xiàn)異構(gòu)集成

中國(guó)半導(dǎo)體行業(yè)協(xié)會(huì)副理事長(zhǎng)、長(zhǎng)電科技董事兼首席執(zhí)行長(zhǎng)鄭力表示:“后摩爾時(shí)代半導(dǎo)體器件成品制造技術(shù)和價(jià)值遠(yuǎn)超封測(cè)字義范疇,目前從先進(jìn)封裝到芯片成品制造的產(chǎn)業(yè)升級(jí)趨勢(shì)明顯,長(zhǎng)電兩大核心技術(shù)可以實(shí)現(xiàn)異構(gòu)集成。同時(shí),協(xié)同設(shè)計(jì)優(yōu)化芯片成品集成與測(cè)試一體化趨勢(shì)非常重要。”

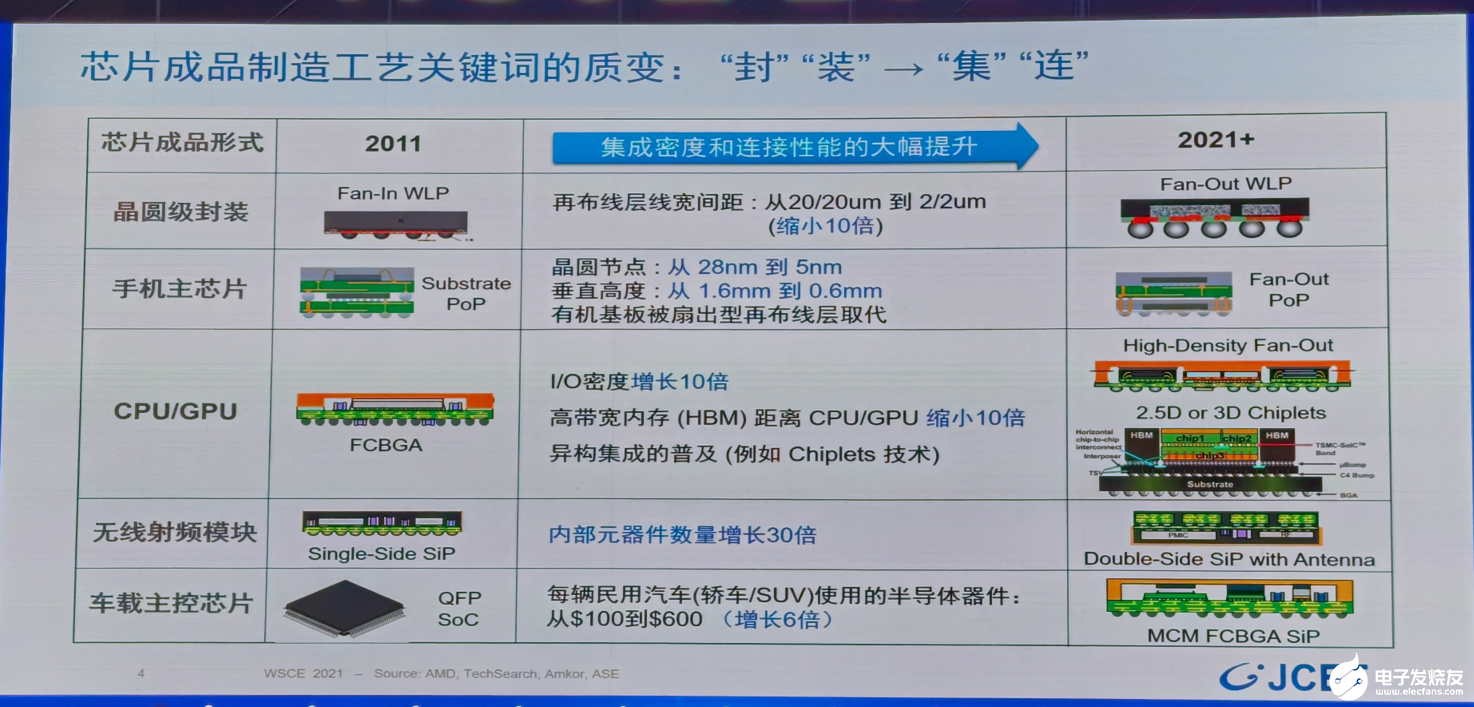

鄭力分析說(shuō),目前,晶圓級(jí)封裝的再布線層線寬間距已經(jīng)從20/20um發(fā)展到2/2um,縮小了10倍,幾乎與手機(jī)主芯片制程演進(jìn)是同樣的速度,從2011年的28nm進(jìn)入到今天的5nm;手機(jī)主芯片的晶圓節(jié)點(diǎn)也從28nm發(fā)展到5nm,從有機(jī)基板變?yōu)樯瘸鲂驮俨季€層,垂直高度從1.6nm到0.6nm;CPU、GPU的I/O密度增長(zhǎng)10倍,集成高帶寬的存儲(chǔ)器,還有異構(gòu)集成技術(shù)加入;無(wú)線射頻模塊內(nèi)布元器件數(shù)量增長(zhǎng)30倍。用一句話概括,先進(jìn)封裝在技術(shù)向前發(fā)展到異構(gòu)集成,微系統(tǒng)集成階段時(shí)實(shí)現(xiàn)了質(zhì)的飛躍。

上周AMD在臺(tái)北電腦展展示的2.5DChiplet、3D Chiplet等異構(gòu)集成,密度提高300倍,臺(tái)積電、Intel,國(guó)際半導(dǎo)體的頭部企業(yè)都在積極布局半導(dǎo)體的異構(gòu)集成應(yīng)用。

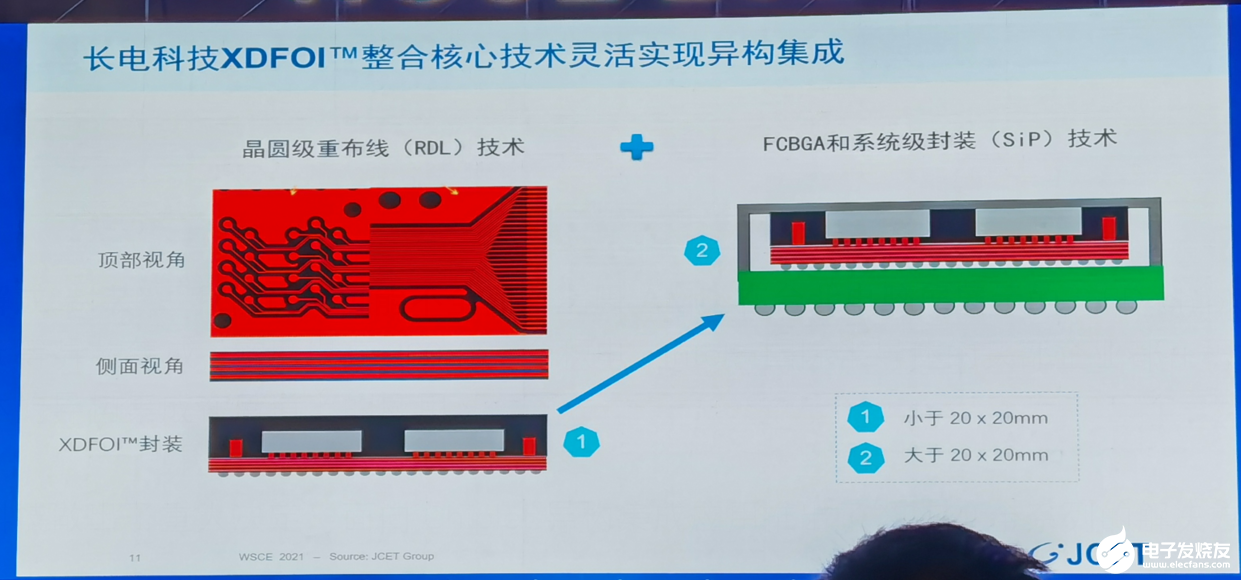

先進(jìn)芯片成品制造技術(shù)正在發(fā)生顛覆性突破,長(zhǎng)電科技也在異構(gòu)集成技術(shù)賽道上不斷換擋提速。針對(duì)Chiplet異構(gòu)集成應(yīng)用,長(zhǎng)電科技推出了XDFO全系列的解決方案,包括2D Chiplet、2.5D Chiplet和3D Chiplet,可適用于移動(dòng)通信、汽車(chē)、醫(yī)療和人工智能等應(yīng)用。

基于設(shè)計(jì)需求,長(zhǎng)電科技的無(wú)硅通孔扇出型晶圓級(jí)高密度封裝技術(shù),可在硅中介層(Si Interposer)中使用堆疊通孔技術(shù)(Stacked VIA)替代硅通孔技術(shù)(TSV)。該技術(shù)可以實(shí)現(xiàn)多層RDL再布線層,2×2um的線寬間距,40um極窄凸塊互聯(lián),多層芯片疊加,集成高帶寬存儲(chǔ)和集成無(wú)源元件。

長(zhǎng)電科技在扇出型技術(shù)積累接近10年,在結(jié)合高密度SIP技術(shù),面向未來(lái)推出2.5D chiplet、3D chiplet等產(chǎn)品解決方案,可靈活實(shí)現(xiàn)異構(gòu)集成。鄭力透露,這些產(chǎn)品在2022年、2023年都有面向量產(chǎn)的項(xiàng)目和解決方案。

鄭力強(qiáng)調(diào)說(shuō):“除了在技術(shù)和工藝上不斷突破,要實(shí)現(xiàn)低成本、高性能、環(huán)保優(yōu)質(zhì)的集成電路產(chǎn)品制造,還需要通過(guò)系統(tǒng)級(jí)電性能、結(jié)構(gòu)、熱仿真模擬與系統(tǒng)設(shè)計(jì),這就使得芯片成品集成測(cè)試一體化成為一種潮流。長(zhǎng)電科技要和IP、設(shè)計(jì)企業(yè)、EDA企業(yè)合作,芯片主體的協(xié)同設(shè)計(jì)要做起來(lái)。”

小結(jié)

中國(guó)科學(xué)院院士毛軍發(fā)院士指出,異質(zhì)集成電路特色突出:一是可以融合不同半導(dǎo)體材料、工藝、結(jié)構(gòu)和元器件或芯片的優(yōu)點(diǎn);二是采用系統(tǒng)設(shè)計(jì)理念;三是應(yīng)用先進(jìn)技術(shù)比如IP和小芯片Chiplet;具有2.5D或3D高密度結(jié)構(gòu)。異質(zhì)集成電路優(yōu)點(diǎn)明顯:首先,實(shí)現(xiàn)強(qiáng)大的復(fù)雜功能、優(yōu)異的綜合性能,突破單一半導(dǎo)體工藝的性能極限;二是靈活性大、可靠性高、研發(fā)周期短;三是三維集成可以實(shí)現(xiàn)小型化、輕質(zhì)化;對(duì)半導(dǎo)體設(shè)備要求相對(duì)比較低,不受EUV光刻機(jī)限制。

臺(tái)積電、日月光、長(zhǎng)電科技的最新實(shí)踐和技術(shù)演進(jìn),相信能給未來(lái)5G高性能計(jì)算、AI和IoT芯片的落地帶來(lái)更多助力,也是中國(guó)芯片彎道超車(chē)的可能路徑之一。

本文由電子發(fā)燒友原創(chuàng),作者章鷹,微信號(hào)zy1052625525,轉(zhuǎn)載請(qǐng)注明以上來(lái)源。如需入群交流,請(qǐng)?zhí)砑游⑿舉lecfans999,投稿發(fā)郵件到huangjingjing@elecfans.com.

-

amd

+關(guān)注

關(guān)注

25文章

5682瀏覽量

139937 -

臺(tái)積電

+關(guān)注

關(guān)注

44文章

5803瀏覽量

176286 -

長(zhǎng)電科技

+關(guān)注

關(guān)注

5文章

394瀏覽量

33484

發(fā)布評(píng)論請(qǐng)先 登錄

臺(tái)積電計(jì)劃建設(shè)4座先進(jìn)封裝廠,應(yīng)對(duì)AI芯片需求

臺(tái)積電CoWoS平臺(tái)微通道芯片封裝液冷技術(shù)的演進(jìn)路線

臺(tái)積電Q3凈利潤(rùn)4523億元新臺(tái)幣 英偉達(dá)或取代蘋(píng)果成臺(tái)積電最大客戶

系統(tǒng)級(jí)立體封裝技術(shù)的發(fā)展與應(yīng)用

臺(tái)積電日月光主導(dǎo),3DIC先進(jìn)封裝聯(lián)盟正式成立

化圓為方,臺(tái)積電整合推出最先進(jìn)CoPoS半導(dǎo)體封裝

今日看點(diǎn):傳臺(tái)積電先進(jìn)2nm芯片生產(chǎn)停用中國(guó)大陸設(shè)備;保時(shí)捷裁員約200人

先進(jìn)封裝轉(zhuǎn)接板的典型結(jié)構(gòu)和分類

后摩爾時(shí)代破局者:物元半導(dǎo)體領(lǐng)航中國(guó)3D集成制造產(chǎn)業(yè)

臺(tái)積電引領(lǐng)全球半導(dǎo)體制程創(chuàng)新,2納米制程備受關(guān)注

看點(diǎn):臺(tái)積電在美建兩座先進(jìn)封裝廠 博通十億美元半導(dǎo)體工廠談判破裂

美國(guó)芯片“卡脖子”真相:臺(tái)積電美廠芯片竟要運(yùn)回臺(tái)灣封裝?

臺(tái)積電先進(jìn)制程漲價(jià),最高或達(dá)30%!

逆變器EMC整改:從干擾超標(biāo)到完美達(dá)標(biāo)的華麗轉(zhuǎn)身

后摩爾時(shí)代,先進(jìn)封裝如何實(shí)現(xiàn)華麗轉(zhuǎn)身?臺(tái)積電領(lǐng)銜的三大企業(yè)放大招

后摩爾時(shí)代,先進(jìn)封裝如何實(shí)現(xiàn)華麗轉(zhuǎn)身?臺(tái)積電領(lǐng)銜的三大企業(yè)放大招

評(píng)論