電子發(fā)燒友網(wǎng)綜合報(bào)道

近日,據(jù)報(bào)道,臺積電將持續(xù)推進(jìn)先進(jìn)封裝技術(shù),正式整合CoWoS與FOPLP,推出新一代CoPoS工藝。

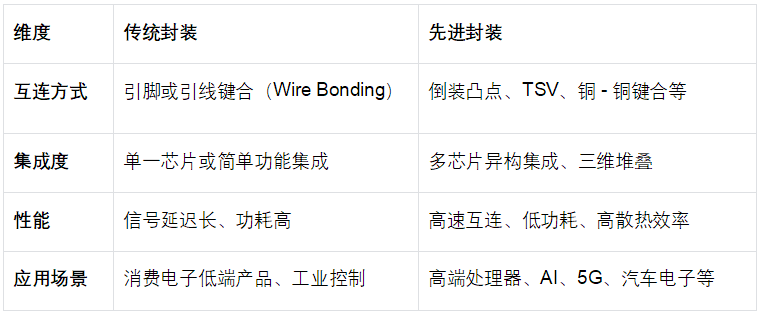

作為臺積電先進(jìn)封裝技術(shù)的集大成者,CoPoS并非憑空出現(xiàn),而是建立在成熟技術(shù)基礎(chǔ)上的創(chuàng)新升級。長期以來,CoWoS作為臺積電的主力封裝技術(shù),憑借在高性能計(jì)算芯片領(lǐng)域的穩(wěn)定表現(xiàn)占據(jù)重要地位,但其采用的圓形硅中介層在面積利用率和大規(guī)模量產(chǎn)方面存在局限。

而 FOPLP作為扇出型面板級封裝技術(shù),雖能在更大面板上進(jìn)行芯片封裝,卻在高集成度場景下的性能表現(xiàn)稍顯不足。CoPoS的誕生正是為了融合兩者優(yōu)勢,通過“化圓為方”的革新設(shè)計(jì),將芯片排列在大型方形基板上,徹底打破傳統(tǒng)圓形中介層的束縛。

CoPoS 技術(shù)的核心突破在于對封裝載體和結(jié)構(gòu)的全面升級。它創(chuàng)新性地采用玻璃或藍(lán)寶石材質(zhì)的方形載具作為中介層,并在其上鍍制 RDL,這一設(shè)計(jì)不僅支持更大的光罩尺寸和更高的集成度,更有效緩解了大尺寸芯片封裝過程中易出現(xiàn)的翹曲問題。

在尺寸與效率方面,CoPoS展現(xiàn)出了驚人的優(yōu)勢。傳統(tǒng)300mm圓形晶圓的封裝面積有限,而CoPoS支持的面板尺寸可達(dá)310x310mm、515x510mm,甚至能達(dá)到750x620mm的超大規(guī)格。

據(jù)Yole的報(bào)告數(shù)據(jù),采用300x300mm面板時(shí),可容納16個(gè)中介層,面積利用率高達(dá)81%;而600x600mm面板更是能集成64個(gè)中介層,同樣保持81%的高面積利用率,遠(yuǎn)超傳統(tǒng)圓形晶圓45%的利用率水平。

面積利用率的大幅提升直接帶來了成本優(yōu)化,數(shù)據(jù)顯示,相比傳統(tǒng)方案,CoPoS技術(shù)可實(shí)現(xiàn)約10%至20%的成本下降,這對于大規(guī)模量產(chǎn)的AI芯片而言,意味著顯著的成本優(yōu)勢。

在量產(chǎn)規(guī)劃方面,臺積電已為CoPoS技術(shù)制定了清晰的路線圖。按照計(jì)劃,首條CoPoS實(shí)驗(yàn)線將于2026年在臺積電子公司采鈺設(shè)立,為技術(shù)成熟度驗(yàn)證和工藝優(yōu)化奠定基礎(chǔ)。

量產(chǎn)階段則將落地嘉義AP7廠的P4、P5廠區(qū),同時(shí)美國亞利桑那州的兩座先進(jìn)封裝廠也將同步布局,其中一座將以CoPoS技術(shù)為主。預(yù)計(jì)最快到2028年底至2029年上半年,CoPoS技術(shù)將實(shí)現(xiàn)大規(guī)模量產(chǎn),為半導(dǎo)體產(chǎn)業(yè)注入新的活力。

隨著相關(guān)設(shè)備規(guī)格與訂單量確定,全球供應(yīng)鏈企業(yè)紛紛加入競標(biāo)行列,首波供應(yīng)鏈名單囊括 KLA、TEL、Screen、Applied Materials、Disco 等國際大廠,以及印能、辛耘、弘塑、均華、致茂、志圣等 13 家臺廠。

從CoWoS到CoPoS,臺積電在先進(jìn)封裝技術(shù)領(lǐng)域的持續(xù)創(chuàng)新,不僅推動了自身技術(shù)壁壘的提升,更深刻影響著全球半導(dǎo)體產(chǎn)業(yè)的發(fā)展格局。在AI技術(shù)加速滲透的當(dāng)下,CoPoS技術(shù)的出現(xiàn)將以更大的尺寸、更高的效率、更低的成本,為大尺寸芯片封裝提供全新解決方案,助力全球半導(dǎo)體產(chǎn)業(yè)邁向更高的集成度與性能水平,為數(shù)字經(jīng)濟(jì)的發(fā)展注入源源不斷的動力。

近日,據(jù)報(bào)道,臺積電將持續(xù)推進(jìn)先進(jìn)封裝技術(shù),正式整合CoWoS與FOPLP,推出新一代CoPoS工藝。

作為臺積電先進(jìn)封裝技術(shù)的集大成者,CoPoS并非憑空出現(xiàn),而是建立在成熟技術(shù)基礎(chǔ)上的創(chuàng)新升級。長期以來,CoWoS作為臺積電的主力封裝技術(shù),憑借在高性能計(jì)算芯片領(lǐng)域的穩(wěn)定表現(xiàn)占據(jù)重要地位,但其采用的圓形硅中介層在面積利用率和大規(guī)模量產(chǎn)方面存在局限。

而 FOPLP作為扇出型面板級封裝技術(shù),雖能在更大面板上進(jìn)行芯片封裝,卻在高集成度場景下的性能表現(xiàn)稍顯不足。CoPoS的誕生正是為了融合兩者優(yōu)勢,通過“化圓為方”的革新設(shè)計(jì),將芯片排列在大型方形基板上,徹底打破傳統(tǒng)圓形中介層的束縛。

CoPoS 技術(shù)的核心突破在于對封裝載體和結(jié)構(gòu)的全面升級。它創(chuàng)新性地采用玻璃或藍(lán)寶石材質(zhì)的方形載具作為中介層,并在其上鍍制 RDL,這一設(shè)計(jì)不僅支持更大的光罩尺寸和更高的集成度,更有效緩解了大尺寸芯片封裝過程中易出現(xiàn)的翹曲問題。

在尺寸與效率方面,CoPoS展現(xiàn)出了驚人的優(yōu)勢。傳統(tǒng)300mm圓形晶圓的封裝面積有限,而CoPoS支持的面板尺寸可達(dá)310x310mm、515x510mm,甚至能達(dá)到750x620mm的超大規(guī)格。

據(jù)Yole的報(bào)告數(shù)據(jù),采用300x300mm面板時(shí),可容納16個(gè)中介層,面積利用率高達(dá)81%;而600x600mm面板更是能集成64個(gè)中介層,同樣保持81%的高面積利用率,遠(yuǎn)超傳統(tǒng)圓形晶圓45%的利用率水平。

面積利用率的大幅提升直接帶來了成本優(yōu)化,數(shù)據(jù)顯示,相比傳統(tǒng)方案,CoPoS技術(shù)可實(shí)現(xiàn)約10%至20%的成本下降,這對于大規(guī)模量產(chǎn)的AI芯片而言,意味著顯著的成本優(yōu)勢。

在量產(chǎn)規(guī)劃方面,臺積電已為CoPoS技術(shù)制定了清晰的路線圖。按照計(jì)劃,首條CoPoS實(shí)驗(yàn)線將于2026年在臺積電子公司采鈺設(shè)立,為技術(shù)成熟度驗(yàn)證和工藝優(yōu)化奠定基礎(chǔ)。

量產(chǎn)階段則將落地嘉義AP7廠的P4、P5廠區(qū),同時(shí)美國亞利桑那州的兩座先進(jìn)封裝廠也將同步布局,其中一座將以CoPoS技術(shù)為主。預(yù)計(jì)最快到2028年底至2029年上半年,CoPoS技術(shù)將實(shí)現(xiàn)大規(guī)模量產(chǎn),為半導(dǎo)體產(chǎn)業(yè)注入新的活力。

隨著相關(guān)設(shè)備規(guī)格與訂單量確定,全球供應(yīng)鏈企業(yè)紛紛加入競標(biāo)行列,首波供應(yīng)鏈名單囊括 KLA、TEL、Screen、Applied Materials、Disco 等國際大廠,以及印能、辛耘、弘塑、均華、致茂、志圣等 13 家臺廠。

從CoWoS到CoPoS,臺積電在先進(jìn)封裝技術(shù)領(lǐng)域的持續(xù)創(chuàng)新,不僅推動了自身技術(shù)壁壘的提升,更深刻影響著全球半導(dǎo)體產(chǎn)業(yè)的發(fā)展格局。在AI技術(shù)加速滲透的當(dāng)下,CoPoS技術(shù)的出現(xiàn)將以更大的尺寸、更高的效率、更低的成本,為大尺寸芯片封裝提供全新解決方案,助力全球半導(dǎo)體產(chǎn)業(yè)邁向更高的集成度與性能水平,為數(shù)字經(jīng)濟(jì)的發(fā)展注入源源不斷的動力。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

臺積電

+關(guān)注

關(guān)注

44文章

5804瀏覽量

176825 -

封裝

+關(guān)注

關(guān)注

128文章

9297瀏覽量

148891

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

臺積電計(jì)劃建設(shè)4座先進(jìn)封裝廠,應(yīng)對AI芯片需求

電子發(fā)燒友網(wǎng)報(bào)道 近日消息,臺積電計(jì)劃在嘉義科學(xué)園區(qū)先進(jìn)封裝二期和南部科學(xué)園區(qū)三期各建設(shè)兩座先進(jìn)

1.4nm制程工藝!臺積電公布量產(chǎn)時(shí)間表

電子發(fā)燒友網(wǎng)綜合報(bào)道 近日,全球半導(dǎo)體代工龍頭臺積電在先進(jìn)制程領(lǐng)域持續(xù)展現(xiàn)強(qiáng)勁發(fā)展勢頭。據(jù)行業(yè)信源確認(rèn),

臺積電CoWoS平臺微通道芯片封裝液冷技術(shù)的演進(jìn)路線

臺積電在先進(jìn)封裝技術(shù),特別是CoWoS(Chip on Wafer on Substrate)平臺上的微通道芯片液冷技術(shù)路線,是其應(yīng)對高性能

BW-4022A半導(dǎo)體分立器件綜合測試平臺---精準(zhǔn)洞察,卓越測量

參數(shù),以篩選出在制造過程中就已經(jīng)出現(xiàn)缺陷的芯片。這可以避免對有明顯缺陷的芯片進(jìn)行后續(xù)的封裝等昂貴的工序,從而降低成本。對于像英特爾、臺積電這樣的大型芯片制造商,在

發(fā)表于 10-10 10:35

臺積電日月光主導(dǎo),3DIC先進(jìn)封裝聯(lián)盟正式成立

9月9日,半導(dǎo)體行業(yè)迎來重磅消息,3DIC 先進(jìn)封裝制造聯(lián)盟(3DIC Advanced Manufacturing Alliance,簡稱 3DIC AMA)正式宣告成立,該聯(lián)盟由行業(yè)巨頭臺

臺積電引領(lǐng)全球半導(dǎo)體制程創(chuàng)新,2納米制程備受關(guān)注

在全球半導(dǎo)體行業(yè)中,先進(jìn)制程技術(shù)的競爭愈演愈烈。目前,只有臺積電、三星和英特爾三家公司能夠進(jìn)入3納米以下的

臺積電Q2凈利潤3982.7億新臺幣 暴增60% 創(chuàng)歷史新高

電在第二季度毛利率達(dá)到58.6%;營業(yè)利潤率為49.6%,凈利率為42.7%。 在2025年第二季度,臺積

看點(diǎn):臺積電在美建兩座先進(jìn)封裝廠 博通十億美元半導(dǎo)體工廠談判破裂

兩座先進(jìn)的封裝工廠將分別用于導(dǎo)入?3D 垂直集成的SoIC工藝和 CoPoS?面板級大規(guī)模 2.5D 集成技術(shù)。 據(jù)悉臺積

臺積電宣布逐步退出氮化鎵晶圓代工業(yè)務(wù),力積電接手相關(guān)訂單

近日,全球半導(dǎo)體制造巨頭臺積電(TSMC)宣布將逐步退出氮化鎵(GaN)晶圓代工業(yè)務(wù),預(yù)計(jì)在未來兩年內(nèi)完成這一過渡。這一決定引起了行業(yè)的廣泛

破局前行!聯(lián)電擬于臺灣擴(kuò)產(chǎn),全力布局先進(jìn)封裝技術(shù)

近日,半導(dǎo)體行業(yè)傳出重磅消息,聯(lián)電作為全球知名的晶圓代工廠商,正積極考慮在臺灣地區(qū)進(jìn)行大規(guī)模擴(kuò)產(chǎn),并同步布局先進(jìn)封裝技術(shù),這一戰(zhàn)略決策在業(yè)界

臺積電先進(jìn)制程漲價(jià),最高或達(dá)30%!

據(jù)知情人士透露,臺積電2nm工藝晶圓的價(jià)格將較此前上漲10%,去年300mm晶圓的預(yù)估價(jià)格為3萬

發(fā)表于 05-22 01:09

?1316次閱讀

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

刻蝕 第17章 離子注入 第18章 化學(xué)機(jī)械平坦化 第19章 硅片測試 第20章 裝配與封裝 本書詳細(xì)追述了半導(dǎo)體發(fā)展的歷史并吸收了當(dāng)今最新技術(shù)資料,學(xué)術(shù)界和工業(yè)界對《半導(dǎo)體制造技術(shù)

發(fā)表于 04-15 13:52

臺積電最大先進(jìn)封裝廠AP8進(jìn)機(jī)

。改造完成后AP8 廠將是臺積電目前最大的先進(jìn)封裝廠,面積約是此前 AP5 廠的四倍,無塵室面積達(dá) 10 萬平

化圓為方,臺積電整合推出最先進(jìn)CoPoS半導(dǎo)體封裝

化圓為方,臺積電整合推出最先進(jìn)CoPoS半導(dǎo)體封裝

評論