的全部內容。同時它又是一種技術,用以實現從確定系統功能開始,到軟/硬件劃分,并完成設計的整個過程。 System on Chip,簡稱Soc,也即片上系統。從狹義角度講,它是信息系統核心的芯片集成,是將系統關鍵部件集成在一塊芯片上;從廣義角度講, SoC是

2017-12-26 11:46:49 20757

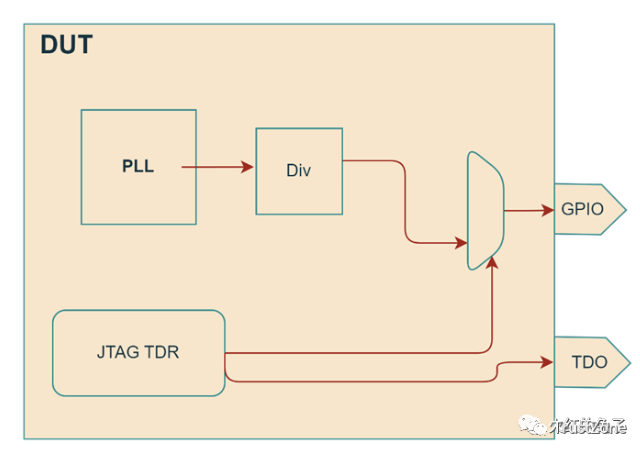

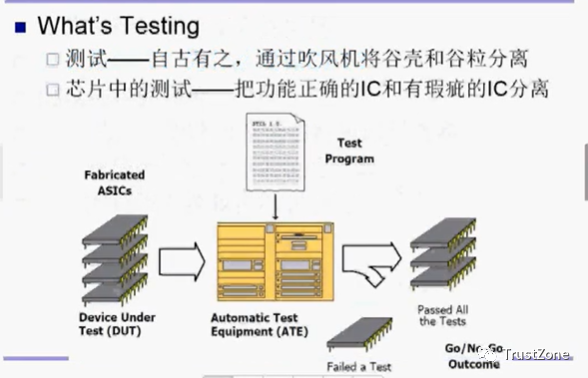

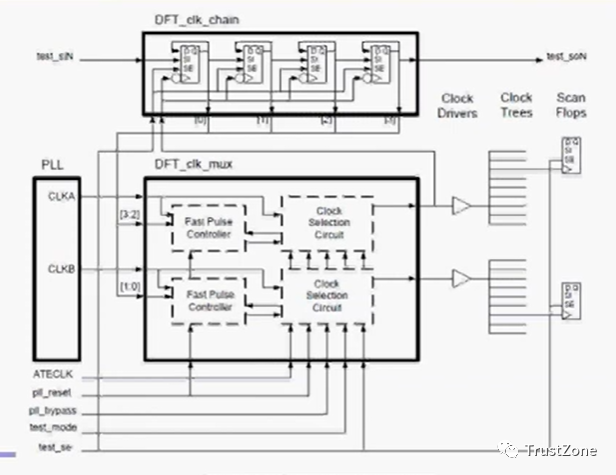

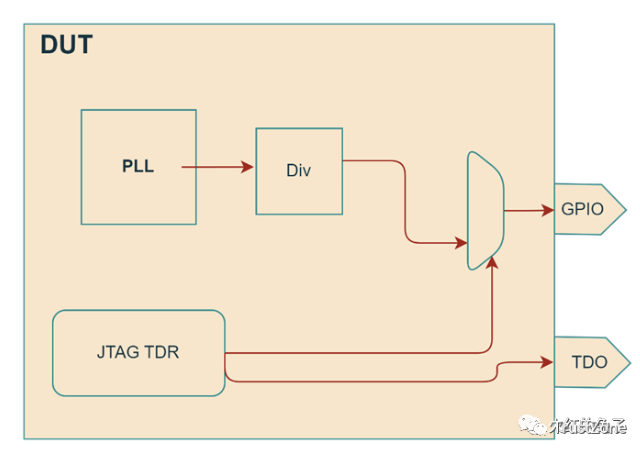

20757 自動測試設備 (ATE)對PLL(鎖相環)進行測試時,我們首先要明白PLL在系統級芯片(SoC)中的重要性。

2023-11-01 15:43:10 4648

4648

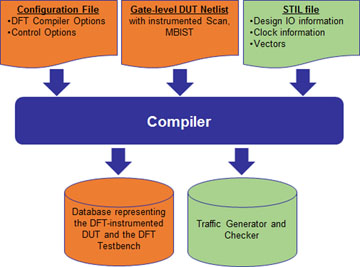

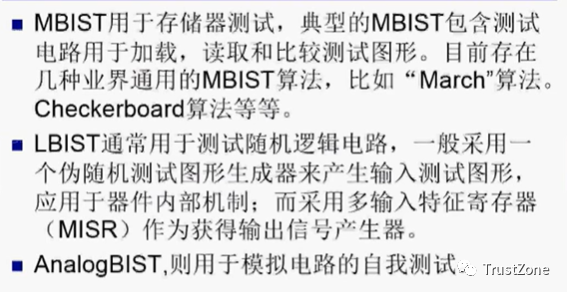

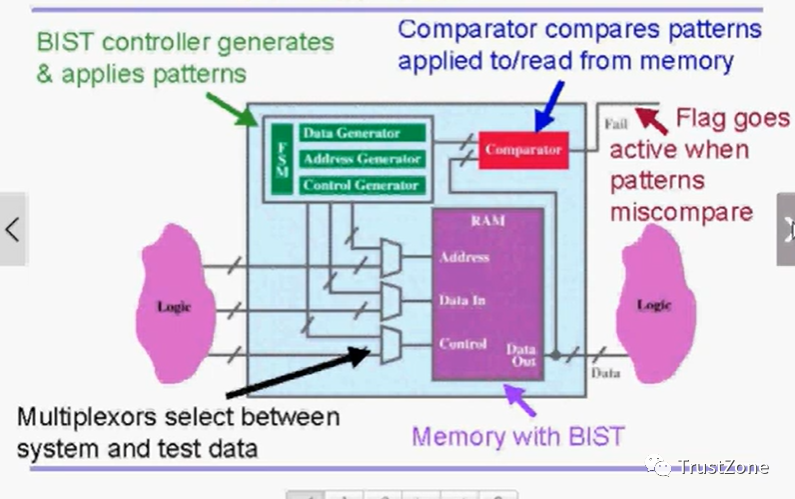

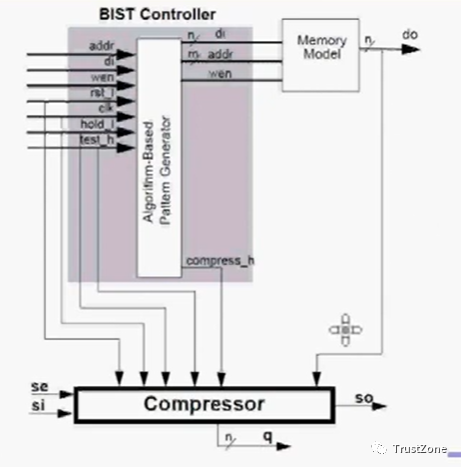

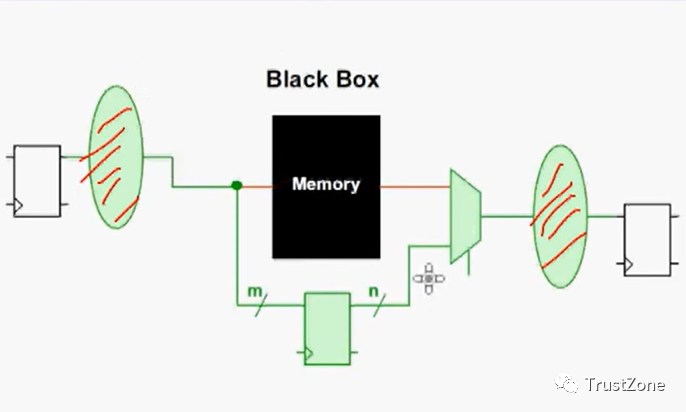

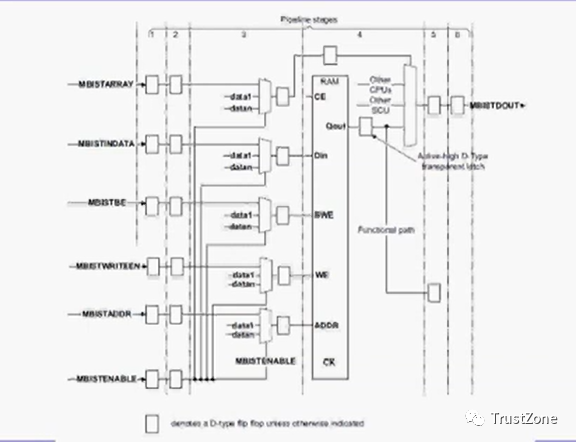

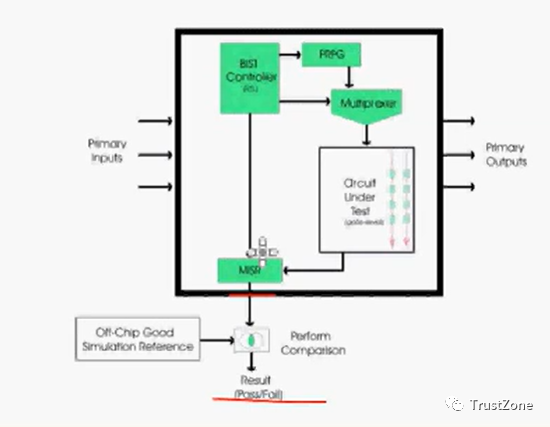

當SoC上有超過80%的芯片面積被各種形式的存儲器占用之時,存儲器的DFT測試已經變得非常重要。

2023-12-09 09:56:55 8370

8370

一、SOC芯片是什么?SOC的定義多種多樣,由于其內涵豐富、應用范圍廣,很難給出準確定義。一般說來,SOC系統級芯片,也有稱片上系統,意指它是一個產品,是一個有專用目標的集成電路,其中包含完整系

2023-12-16 08:28:02 4792

4792

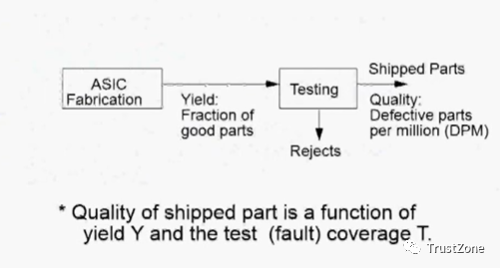

,貫穿設計、制造、封裝以及應用的全過程,在保證芯片性能、提高產業鏈運轉效率方面具有重要作用。IC測試貫穿整個集成電路產業鏈資料來源:基業常青IC測試是確保產品良率和

2024-08-06 08:28:14 2321

2321

片上芯片SoC挑戰傳統測試方案,SoC生產技術的成功,依靠的是廠商以最低的生產成本實現大量的生產能力

2012-01-28 17:14:43 8721

8721

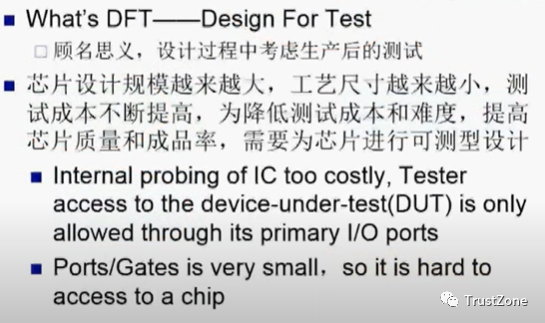

DFT:全稱是 Design for Test,可測性設計,通過在芯片原始設計中插入各種用于提高芯片可測試性(包括可控制性和可觀測性)的硬件邏輯,從而使芯片變得容易測試,大幅度節省芯片測試的成本

2021-07-23 07:28:32

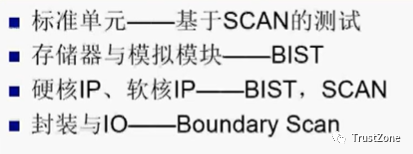

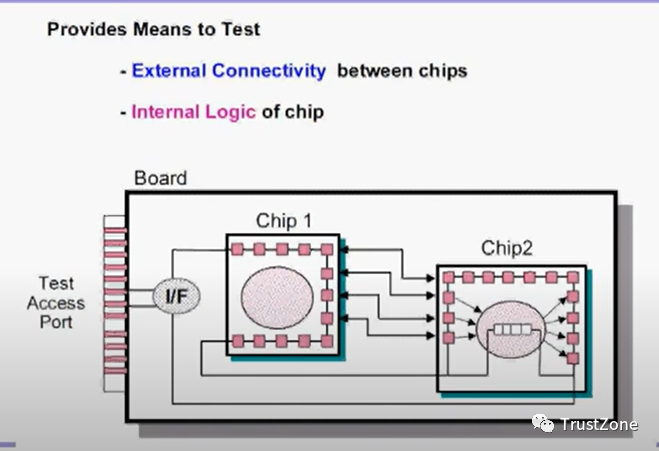

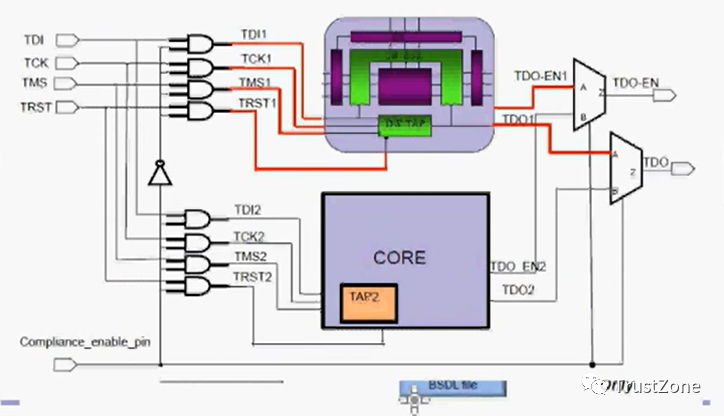

。但是對質量沒有把握的芯片能夠交付使用嗎?這些問題的答案對產品的成功非常重要。 為了確保一定的測試覆蓋率以及盡可能縮短產品測試時間, 圖3:DFT分析、BIST掃描和邊界掃描應該與新的SoC集成電路

2011-12-15 09:53:14

DFT是什么?DFT在芯片設計領域的含義,即可測性設計(Design for Test), 可測試性設計(Design for Test,簡稱DFT)是電路和芯片設計的重要環節,它通過在芯片原始

2012-01-11 14:33:22

DFT是什么?DFT在芯片設計領域的含義,即可測性設計(Design for Test), 可測試性設計(Design for Test,簡稱DFT)是電路和芯片設計的重要環節,它通過在芯片原始

2012-01-11 14:28:06

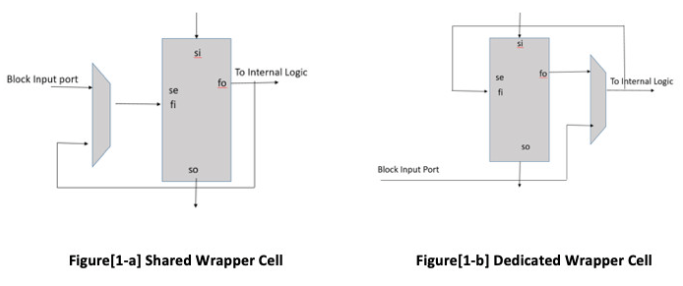

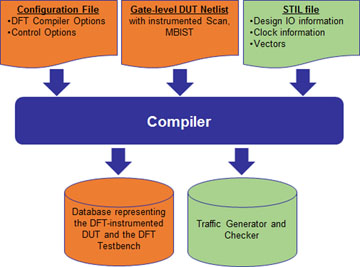

全面測試。SoC 設備的測試已經成為一個越來越具有挑戰性的任務,因為這些設備已經變得非常復雜。SoC 芯片是逐塊構造的,因此當它也是逐塊進行測試時,測試是有效的。設計者可以安裝一個專門的,可配

2022-04-01 11:18:18

請問為什么SoC的發展能夠將測試與測量設備帶入芯片領域?

2021-04-15 06:02:34

SoC,系統級芯片,片上系統,是一個有專用目標的集成電路,其中包含完整系統并有嵌入軟件的全部內容。同時它又是一種技術,用以實現從確定系統功能開始,到軟/硬件劃分,并完成設計的整個過程。從狹義角度講

2016-05-24 19:18:54

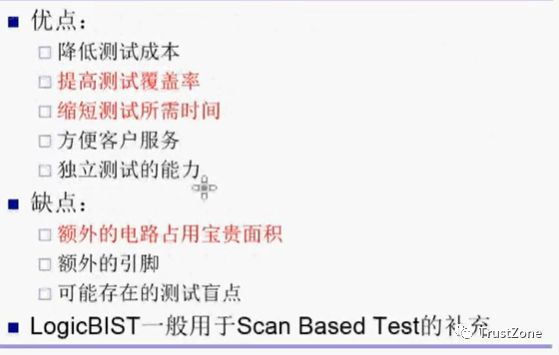

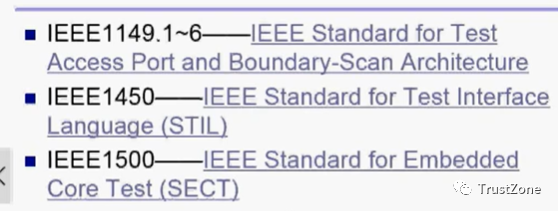

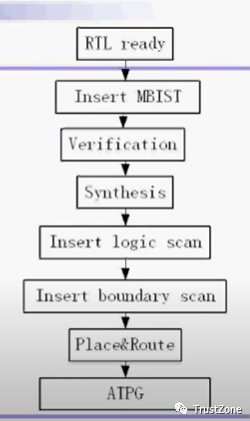

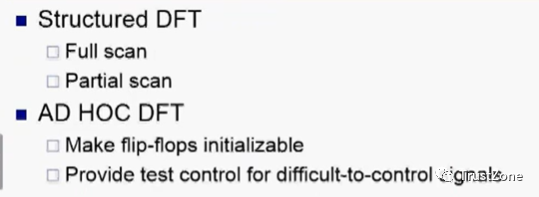

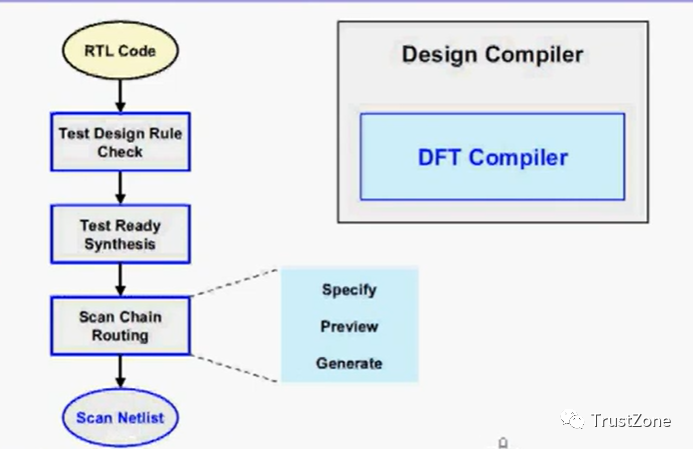

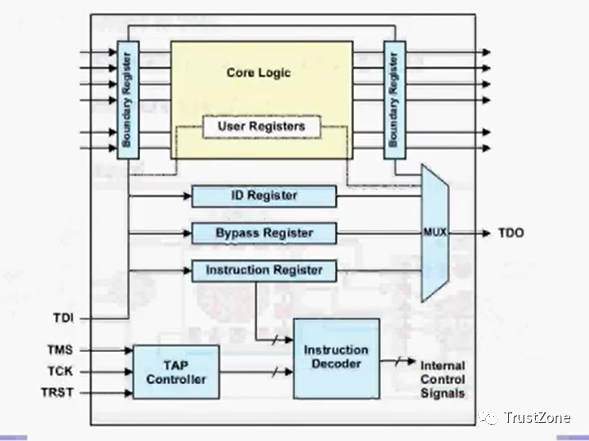

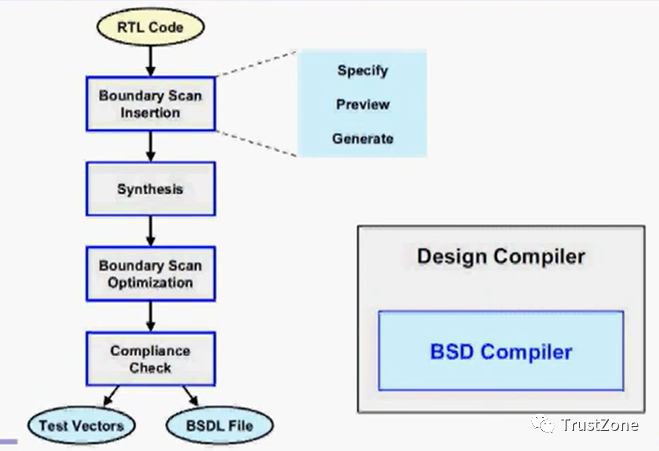

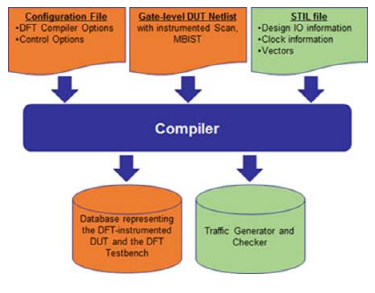

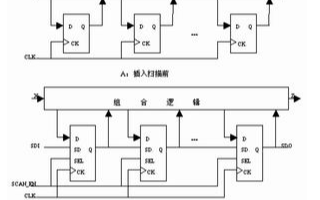

dft可測試性設計,前言可測試性設計方法之一:掃描設計方法可測試性設計方法之二:標準IEEE測試訪問方法可測試性設計方法之三:邏輯內建自測試可測試性設計方法之四:通過MBIST測試寄存器總結...

2021-07-22 09:10:42

soc芯片即System-on-a-Chip,簡單解釋就是系統級芯片。它是一個產品,是一個有專用目標的集成電路,其中包含完整系統并有嵌入軟件的全部內容。同時它又是一種技術,用以實現從確定系統功能

2022-01-25 07:42:31

“本文大部分內容來自LVGL官方文檔,手翻版,如有錯誤歡迎指正。”系列文章目錄一、LVGL系列(一)一文了解LVGL的學習路線輕松了解LVGL的全部二、LVGL系列(二)之一 LVGL必讀介紹

2021-12-07 12:55:03

一文了解透傳云基礎知識講透傳云,我們先了解它的定義,首先了解下****透傳透傳: 透明傳輸。即在傳輸過程中,不管所傳輸的內容、數據協議形式,不對數據做任何處理,只是把需要傳輸的內容數據傳輸到目的。透

2023-02-25 10:32:23

一文帶你了解步進電機的相關知識:相、線、極性和步進方式2017-09-07 16:45這里不說步進電機的 “細分” 實驗,只說一下有關步進電機的基礎概念以及步進電機的三種工作方式——單拍、雙拍、單雙

2021-07-08 06:48:29

導讀:UPS是系統集成項目中常用到的設備,也是機房必備的設備。本文簡單介紹了UPS的種類、功能、原理,品質選擇與配置選擇方式,基礎維護等相關的內容。一文搞懂UPS本文主要內容:UPS種類、功能

2021-09-15 07:49:53

控制原因,除了純粹的測試數據外,收集診斷信息也是一種良好的汽車行業實踐。設計師和技術專家必須從故障設備中得到準確的診斷結果,以便通過在源頭上識別和糾正相關問題來得出正確的維修策略結論,對錯誤行為作出反應

2022-09-07 15:08:41

全基因組CNV分析的策略是什么?

2021-10-27 06:43:48

TD-HSDPA準入策略的外場測試的目的是什么?TD-HSDPA準入策略的外場測試有哪些步驟?TD-HSDPA準入策略的外場測試的結論和部署建議是什么?

2021-05-26 06:49:15

, RISC-V操作系統,YoC基礎軟件平臺,軟件站,嵌入式操作系統一基礎介紹YoC (Yun on Chip)基礎軟件平臺,以AliOS Things為基礎,為芯片開發者提供統一的底層抽象CSI接口,同時也為業務

2021-09-01 15:05:44

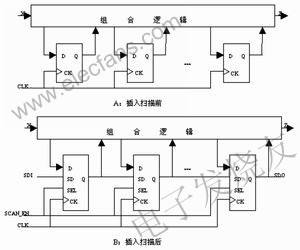

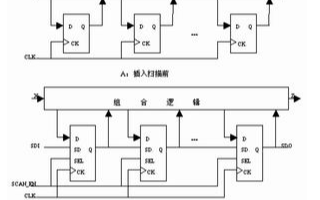

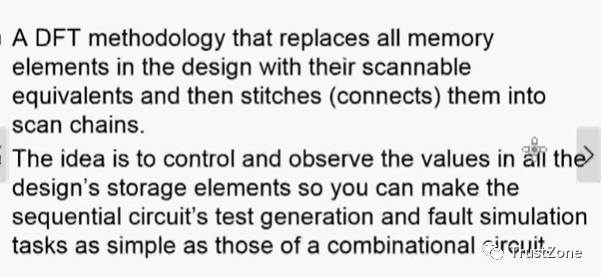

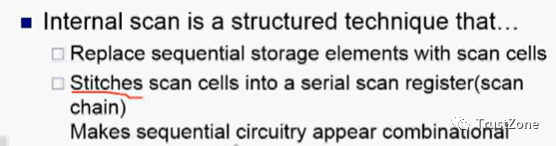

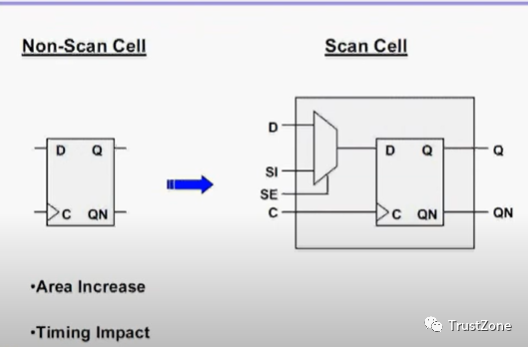

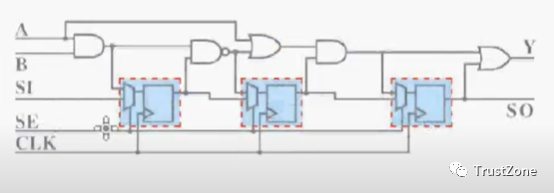

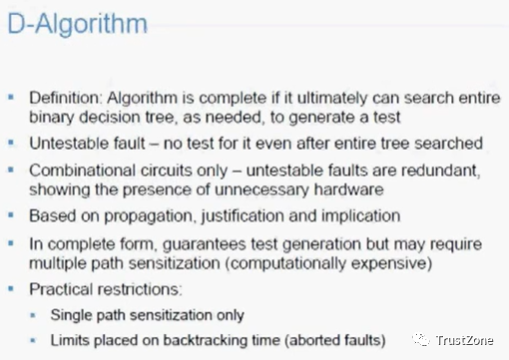

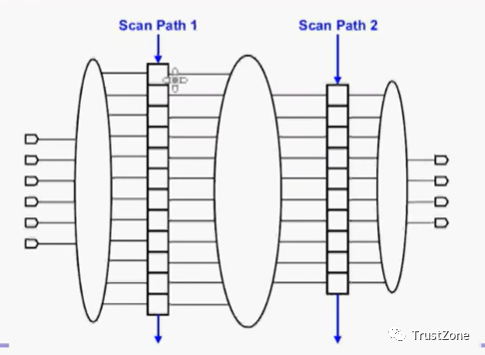

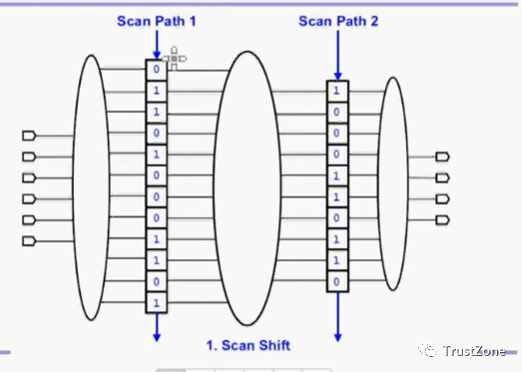

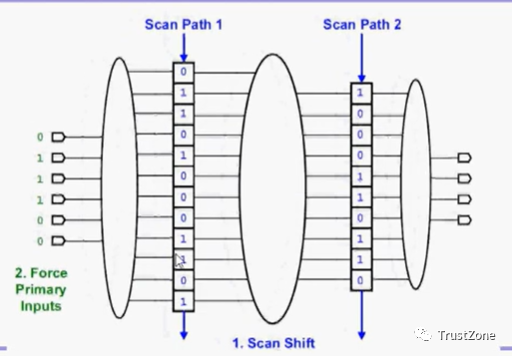

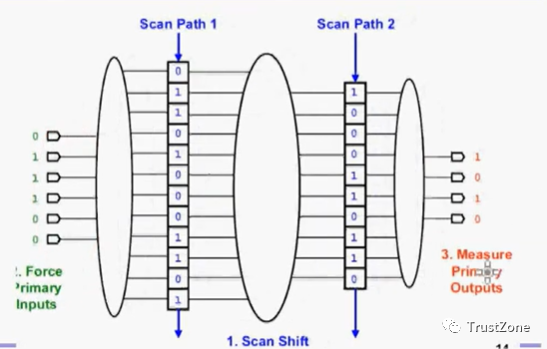

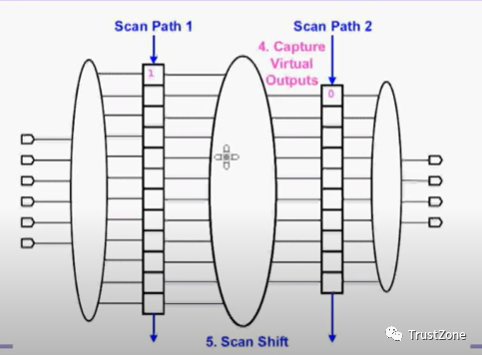

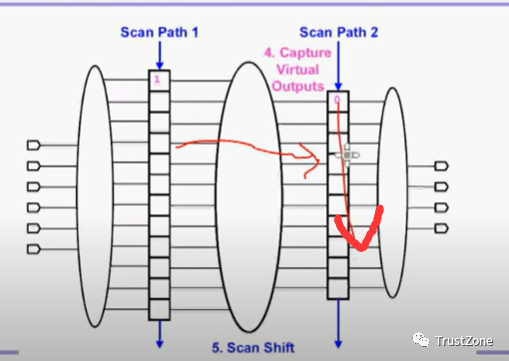

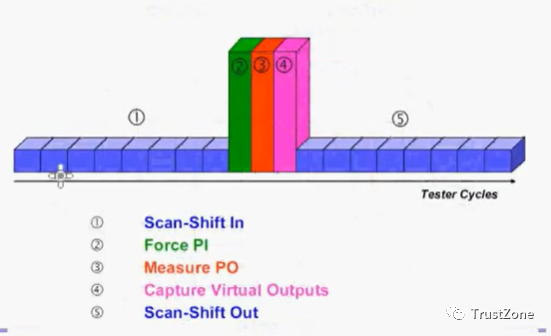

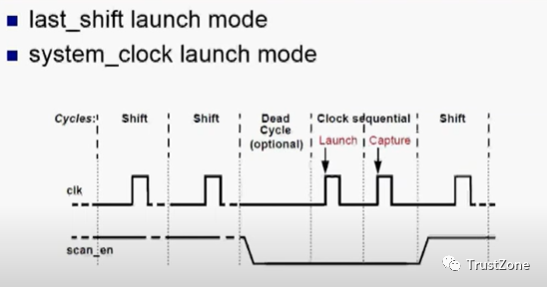

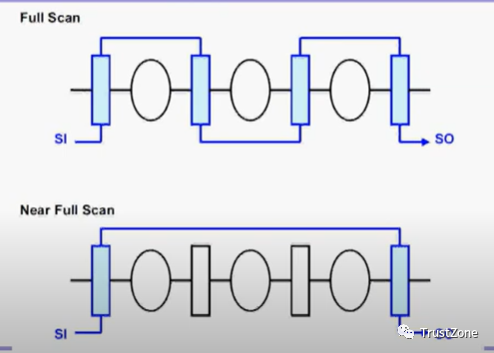

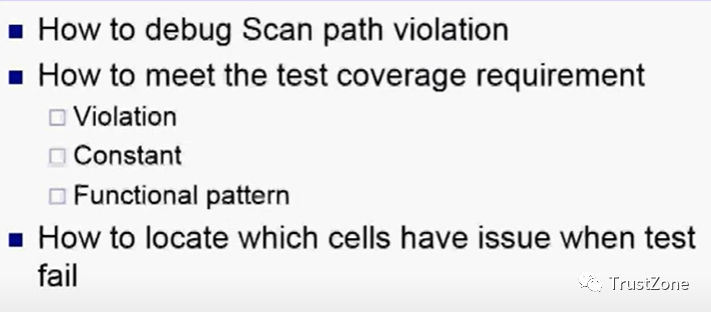

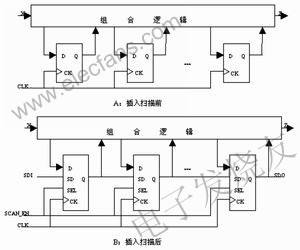

基于掃描的DFT方法掃描設計的基本原理是什么?掃描設計測試的實現過程是怎樣的?基于掃描的DFT對芯片測試的影響有哪些?

2021-05-06 09:56:36

你好。我需要幫助和想法如何使用ML505測試我的AES全定制芯片。我想用它來給我的芯片提供測試向量,clk,復位信號,然后在LCD中顯示數據輸出。我想用VHDL來設計這個測試電路。謝謝

2019-08-29 10:24:35

SoC芯片結構及物理實現流程介紹SoC芯片時序約束設計的關鍵在于功耗管理控制模塊的時序約束時鐘樹設計的內容有哪些?

2021-04-13 06:45:17

正在學習Real-Time DSP和圖像處理的內容,遇到一個問題,如何能在Labview中實現二維DFT?我知道對于一個N*N的矩陣,進行二維DFT時,實際上是先對該矩陣的每個列向量進行DFT運算

2012-06-27 05:23:25

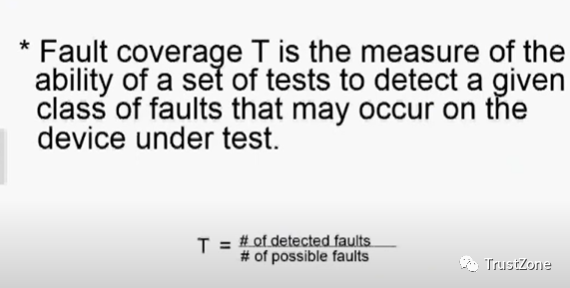

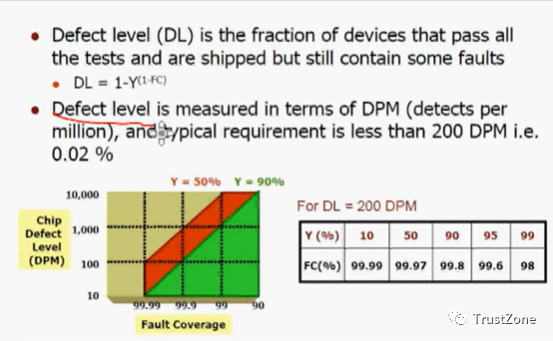

提高DFT設計測試覆蓋率的有效方法是什么

2021-05-07 06:37:41

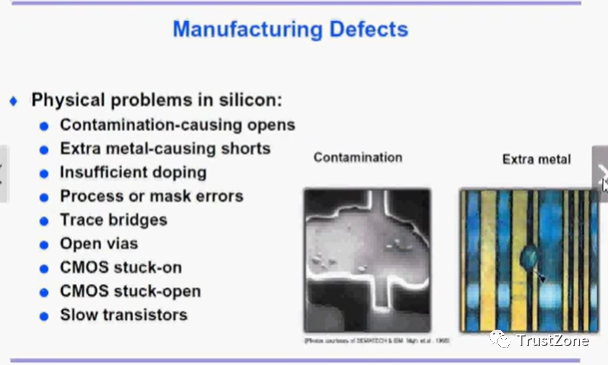

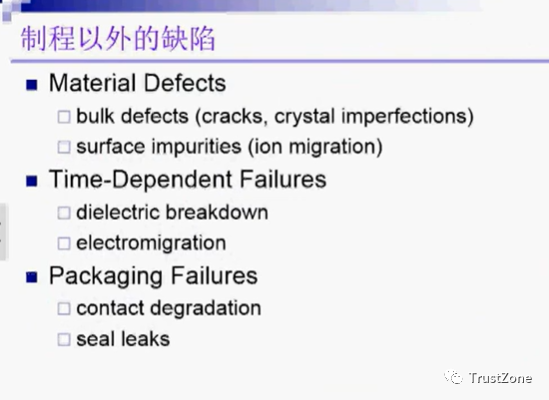

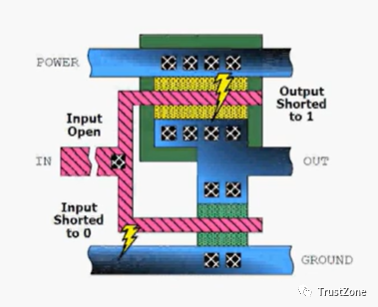

就是此類輔助性設計之一。本期的公眾號文章就來幫助大家了解Scan技術的具體內容。在深入了解scan技術之前,我們先來比較下分別針對組合電路和時序電路的測試過程。很顯然,在芯片制造出來后,我們只能通過其

2016-06-14 14:20:20

急招DFT工程師,職位JD如下,有興趣簡歷請投遞1736253011@qq.comDFT工程師Responsibilities: 1. Participate in SoC level

2017-04-14 14:11:16

請問一下,如何利用AMSVF來進行混合信號SoC的全芯片驗證?

2021-05-06 07:56:08

汽車電子的測試挑戰和策略是什么

2021-05-12 06:55:18

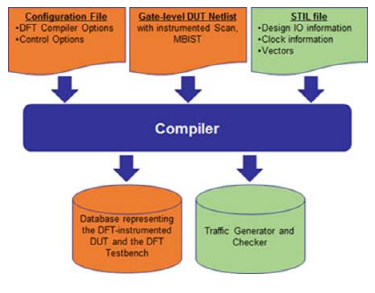

現代PCB測試的策略 隨著自動測試設備成為電子裝配過程整體的一部分,DFT必須不僅僅包括傳統的硬件使用問題,而且也包括測試設備診斷能力的知識。 為測試著想的設計(DFT, design

2018-08-23 10:15:10

netlist功能一致,實現了特定的設計功能。 需要注意的是DFT的方法并不能百分百檢測出功能正確的芯片(因為沒有覆蓋百分百的電路結構),我們需要通過疊加板(board)級系統測試等方法來達到接近

2016-05-25 15:32:58

DFT是什么原理?

2021-06-17 08:54:06

`其中的分辨率f△代進去以后DFT表達式就變成了x[n]exp(-j2pi*n*k*fs/N),和DSP課本上的DFT公式不一樣啊,為什么和fs有關呢?`

2013-05-30 01:02:42

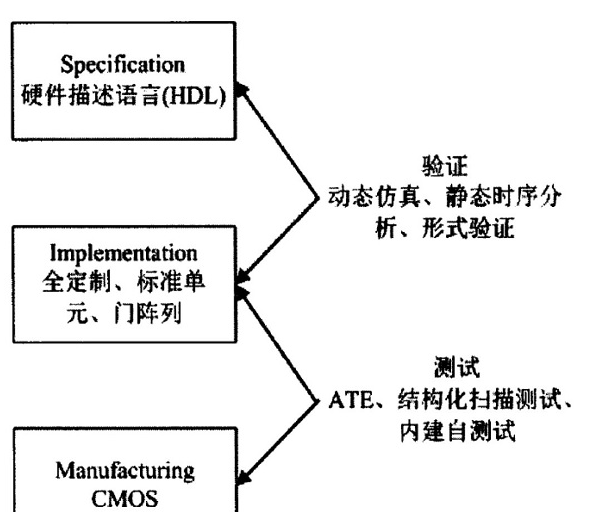

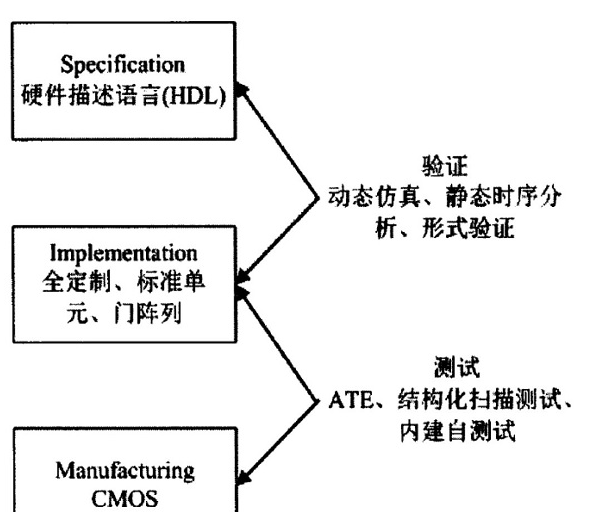

(Integrated Circuit,簡稱IC)進入超大規模集成電路時代,可測試性設計(Design for Test,簡稱DFT)是電路和芯片設計的重要環節,它通過在芯片原始設計中插入各種用于提高芯片可測試

2011-12-15 09:32:30

隨著自動測試設備成為電子裝配過程整體的一部分,DFT必須不僅

2006-04-16 22:05:43 505

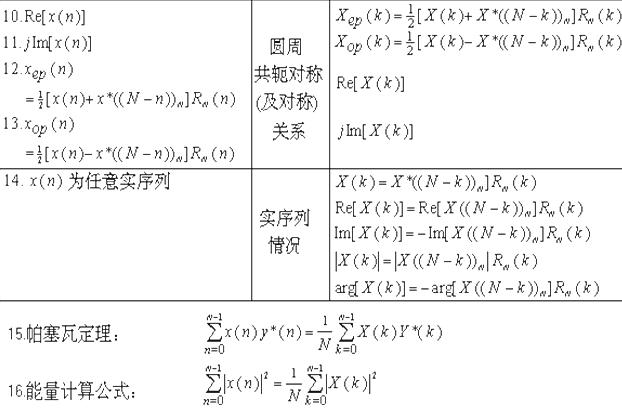

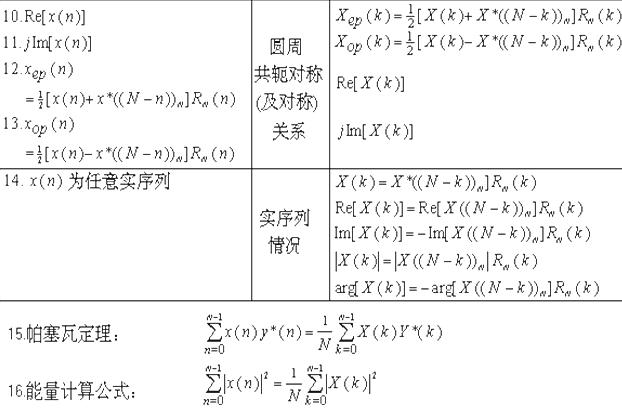

505 DFT性質一覽表

2009-07-25 11:41:03 4349

4349

DFT:數字電路(fpga/asic)設計入門之可測試設計與可測性分析,離散傅里葉變換,(DFT)Direct Fouriet Transformer

可測試性技術(Design For Testability-

2010-06-07 11:00:48 31567

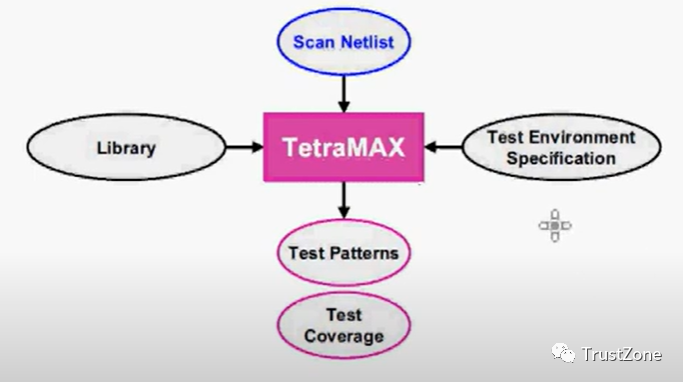

31567 本文通過對一種控制芯片的測試,證明通過采用插入掃描鏈和自動測試向量生成(ATPG)技術,可有效地簡化電路的測試,提高芯片的測試覆蓋率,大大減少測試向量的數量,縮

2010-09-02 10:22:52 3043

3043

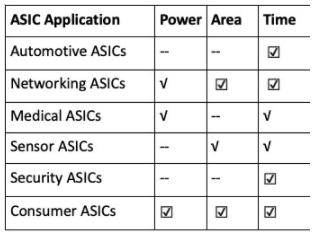

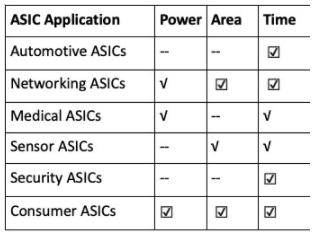

ASIC設計的平均門數不斷增加,這迫使設計團隊將20%到50%的開發工作花費在與測試相關的問題上,以達到良好的測試覆蓋率。盡管遵循可測試設計(DFT)規則被認為是好做法,但對嵌入式R

2011-05-28 11:56:59 1796

1796

DFT在數字信號處理中有很重要的作用,如頻譜分析、FIR DF的實現、線性卷積等。一個重要的原因是DFT有高效算法。 為了了解高效算法的重要以及實現高效算法的思路,先介紹DFT的運算特

2011-09-07 23:59:55 58

58 首先給大家提供DFT和FFT的運算量的教程,內容有直接用DFT計算運算量與用FFT計算的運算量比較和多種DFT算法(時間抽取算法DIT算法,頻率抽取算法DIF算法等.

2011-09-08 00:01:48 71

71 現今流行的可測試性設計(DFT:Design For Testability)為保證芯片的良品率擔任著越來越重要的角色。

2012-04-20 09:39:05 8141

8141

可測試設計(DFT)是適應集成電路的發展要求所出現的一種技術,主要任務是對電路的結構進行調整,提高電路的可測性,即可控制性和可觀察性。

2012-04-27 11:11:59 3787

3787

本內容介紹了DFT可測試性設計的相關知識,并列舉了3中常見的可測性技術供大家學習

2012-05-30 16:42:27 9461

9461 本節內容主要是為了讓用戶快速了解服務器測試策略與方法,能夠用于選型測試中。在此僅僅以最重要的性能、內存緩存性能、數據庫網絡應用輔以基本對比測試來考察不同服務器間的

2012-06-14 17:34:41 1618

1618 本專題為你簡述片上系統SoC相關知識及設計測試。包括SoC定義,SoC設計流程,SoC設計的關鍵技術,SoC設計范例,SoC設計測試及驗證方法,最新SoC芯片解決方案。

2012-10-12 17:57:20

電池SOC估算策略研究,又需要的下來看看。

2017-01-13 13:26:03 13

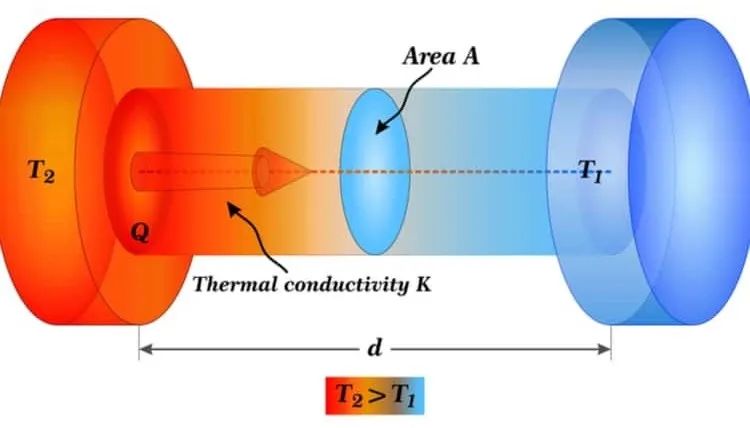

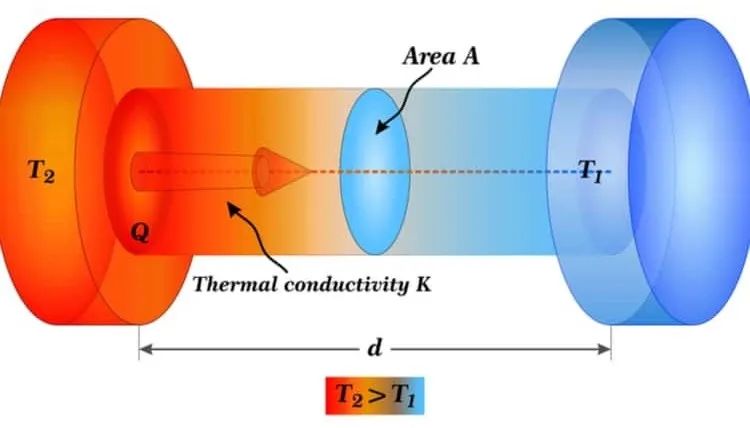

13 隨著芯片規模的增大,低功耗不僅是在功能與性能方面對設計者的挑戰越來越大,同時對于測試而言,隨著SCAN CELL的增多,在SCAN測試時,芯片的功耗也會增大。功耗越大,則芯片的溫度升高,導致芯片內部

2017-11-11 16:20:38 9

9 可測試性設計 (DFT) 在市場上所有的電子設計自動化 (EDA) 工具中是最不被重視的,縱然在設計階段提高芯片的可測試性將會大幅縮減高昂的測試成本,也是如此。最近的分析數據表明,在制造完成后測試

2017-11-28 11:28:38 0

0 通過此視頻可快速瀏覽 PADS DFT 審核的一些主要功能、優點和易用性。在設計流程的早期使用 PADS DFT 審核可大幅降低 PCB 的批量投產時間,確保 100% 的測試點覆蓋和制造前所有網絡的可測試性。

2019-05-21 08:06:00 3979

3979 PADS 可測試性設計 (DFT) 審核可以縮短上市時間。了解如何盡早在設計流程中利用 PCB 測試點和 DFT 審核優化設計。

2019-05-14 06:26:00 4768

4768

DFT 可以降低通過問題器件的風險,如果最終在實際應用中才發現器件有缺陷,所產生的成本將遠遠高于在制造階段發現的成本。它還能避免剔除無缺陷器件,從而提高良率。插入 DFT 亦能縮短與測試開發相關的時間,并減少測試裝配好的芯片所需的時間。

2019-09-16 14:31:51 2663

2663

測性設計(DFT)給整個測試領域開拓了一條切實可行的途徑,目前國際上大中型IC設計公司基本上都采用了可測性設計的設計流程,DFT已經成為芯片設計的關鍵環節。

2020-07-06 11:38:47 10625

10625

隨著ASIC電路結構和功能的日趨復雜,與其相關的測試問題也日益突出。在芯片測試方法和測試向量生成的研究過程中,如何降低芯片的測試成本已經成為非常重要的問題。DFT(可測性設計)通過在芯片原始設計中插入各種用于提高芯片可測性的邏輯,從而使芯片變得容易測試,大大降低了芯片的測試成本。

2020-08-18 14:57:13 4068

4068

用元素和測試點補充您的操作設計以促進電路板的功能測試被稱為可測試性( DFT )設計。 DFT 與制造設計( DFM )不應混淆,盡管兩者都是基于 CM 設備和過程能力的設計人員活動。 DFM

2020-10-12 20:42:17 5283

5283 本文檔的主要內容詳細介紹的是Memory芯片的測試資料詳細說明包括了:Memory芯片的重要性,Memory類型和結構特點, Memory失效機制, Memory測試標識縮寫, Memory故障模型

2020-11-30 08:00:00 0

0 多數 NDMANET緩存策略研究未考慮內容的優先級,從而降低了重要內容在節點移動環境下的可用性。針對該問題,提出一種基于內容優先級的緩存替換策略PFC。根據節點內容對可用性的不同需求劃分內容優先級

2021-03-24 14:48:43 9

9 下面以我所做過的一款SOC芯片來說明SOC芯片集成一個DCDC, 該DCDC具有動態電壓調節,可以通過配置寄存器調節輸出電壓大小,另外DCDC輸出的電壓可能有偏差,通過TRIM值可以調節精度。SOC

2021-11-08 12:36:06 20

20 全可編程SoC設計導論

2021-11-25 19:51:06 9

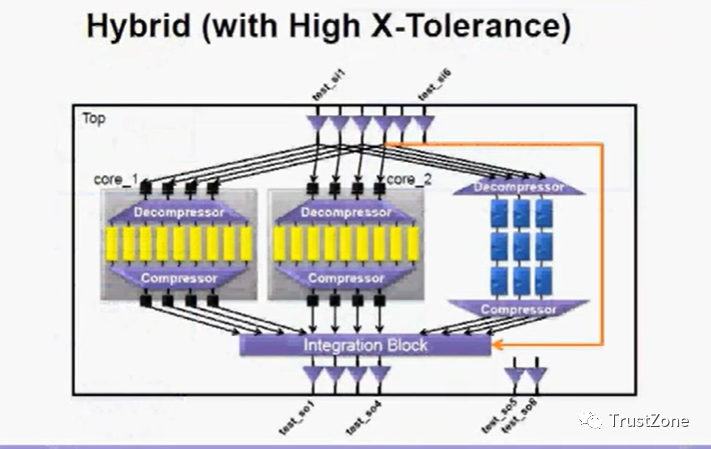

9 在本文中,我們檢查了掃描壓縮確實有助于減少 ASIC 設計中的測試時間 (DFT),但掃描通道減少也是一種有助于頂層測試時間的方法。

2022-06-02 14:25:09 2784

2784

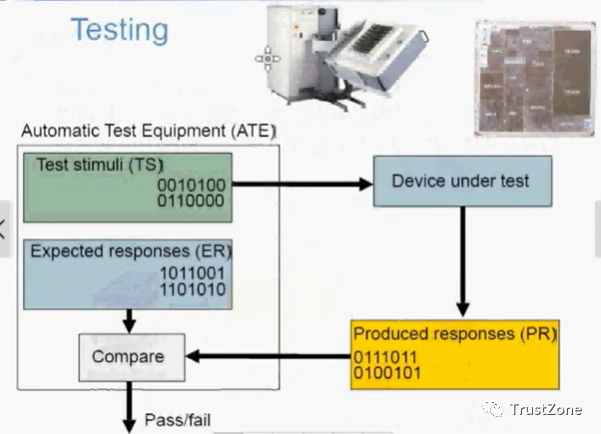

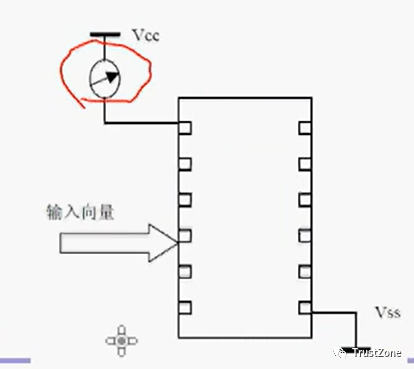

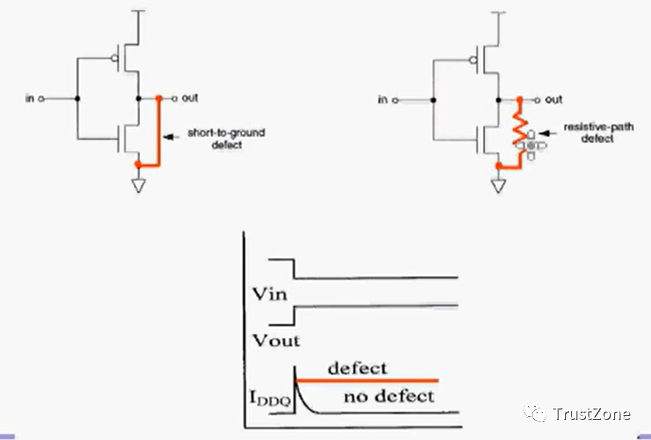

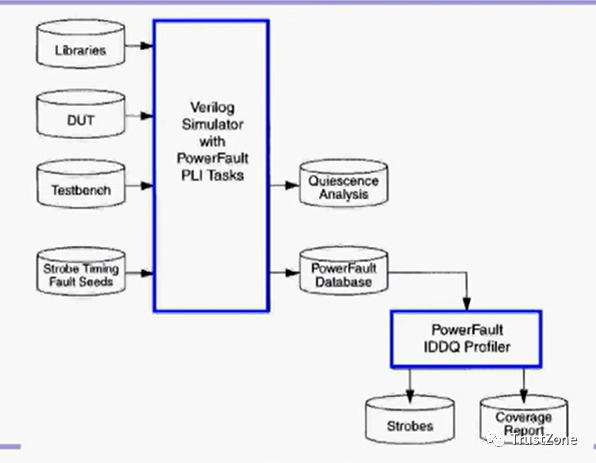

在芯片的DFT驗證過程中,一般會利用ATE向待測芯片的輸入管腳發送測試用的Pattern,然后在芯片的輸出管腳比對輸出時序,由此判斷待測芯片是否存在制造缺陷、符合其功能定義,就像是通過測試的pattern驗證芯片的真值表。

2022-06-16 17:20:07 3822

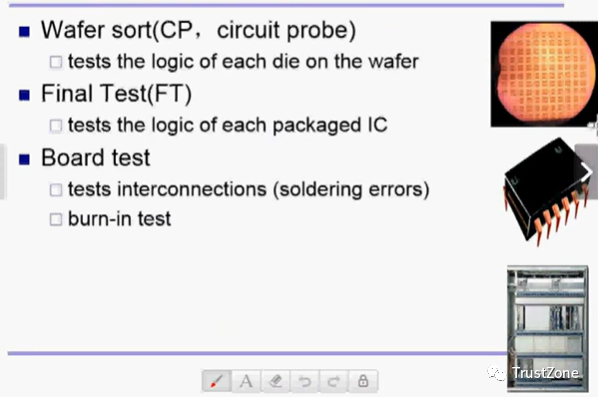

3822 昨天我們了解到芯片的CP測試是什么,以及相關的測試內容和方法,那我們今天趁熱打鐵,來了解一下CP測試的流程。

2022-07-13 17:49:14 11189

11189 在市場上所有的電子設計自動化 (EDA) 工具中,可測試設計 (DFT) 可能是最不被重視的。即使在設計階段將可測試性構建到芯片中也會顯著降低高昂的測試成本。根據最近的分析,在制造后測試一批芯片以確定哪些部件沒有制造缺陷的成本已達到制造芯片成本的 40% 的驚人閾值。

2022-08-22 14:26:30 2034

2034

高級測試設計 (DFT) 技術通過提高順序翻牌的可控性和可觀察性,提供高效的測試解決方案,以應對更高測試成本、更高功耗、測試面積和較低幾何尺寸下的引腳數。這反過來又提高了SoC的良率,可靠性和可測試性是當今ASIC世界的重要因素。

2022-11-23 14:53:53 1646

1646

在本篇白皮書中,我們介紹了一個典型設計的 DFT 組件,并提出了多種可大幅改善 DFT 項目進度的智能 DFT 方法。我們展示了如何將結構化 DFT 和即插即用原則用于 DFT 基礎結構,來支持與其他設計開發工作相似的并行 DFT 開發和集成。

2022-11-30 10:15:00 1583

1583 在芯片做功能ECO時,DFT部分的邏輯常常被破壞,這是由于正常工作模式下修改設計的原因。

2023-03-06 09:15:18 2820

2820 相信很多ICer們在Light芯片的過程中無論前后端都聽過DFT設計測試,DFT全稱Design for Test(即可靠性設計),眾所周知,測試的目的是為了保證芯片成品的質量以及功能邏輯的可靠性的必須 措施。

2023-03-06 14:45:10 5288

5288 DFT是確保芯片在制造過程中具有可測試性的一種技術。DFT友好的ECO是指在進行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設計方法。

2023-03-06 14:47:07 3425

3425 SOC是在同一塊芯片中集成了CPU、各種存儲器、總線系統、專用模塊以及多種I/O接口的系統級超大規模集成電路。ASIC是專用于某一方面的芯片,與SOC芯片相比較為簡單。

2023-04-03 16:04:16 9800

9800 測試SoC芯片需要專業的測試設備、軟硬件工具和測試流程,同時需要一定的測試經驗和技能。并且在測試過程中需要注意安全問題,避免對芯片造成損壞。

2023-05-03 08:26:00 7681

7681 在開始芯片測試流程之前應先充分了解芯片的工作原理。要熟悉它的內部電路,主要參數指標,各個引出線的作用及其正常電壓。芯片很敏感,所以測試的時候要注意不要引起引腳之間的短路,任何一瞬間的短路都能被捕

2023-04-25 15:13:12 4000

4000

DFT是確保芯片在制造過程中具有可測試性的一種技術。DFT友好的ECO是指在進行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設計方法。DFT不友好的ECO會對芯片的測試和調試帶來很大的困難,可能導致芯片測試效率降低甚至無法測試。

2023-05-05 15:06:37 2896

2896

將數個功能不同的芯片,整合成“一個”具有完整功能的芯片,再封裝成“一個”集成電路,稱為“系統級芯片(SoC:SystemonaChip)”。例如:將處理器變成“CPU單元”,北橋芯片變成“MCH單元

2023-04-26 15:17:24 5781

5781

隨著半導體技術的飛速發展,系統級芯片(SoC)設計已成為現代電子設備中的主流。在SoC設計中,可測試性設計(DFT)已成為不可或缺的環節。DFT旨在提高芯片測試的效率和準確性,確保產品質量和可靠性。

2023-09-02 09:50:10 4357

4357 DFT PLL向量,ATE怎么用? 自動測試設備(ATE)對PLL(鎖相環)進行測試時,我們首先要明白PLL在系統級芯片(SoC)中的重要性。它是SoC中關鍵的時鐘或信號同步部件,其性能直接影響

2023-10-30 11:44:17 3368

3368

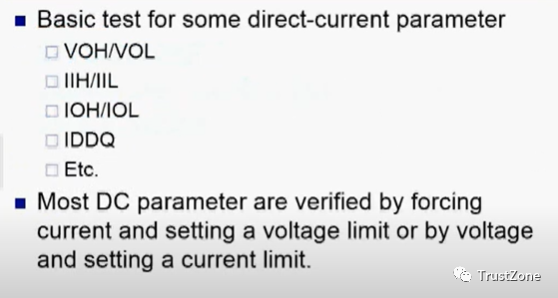

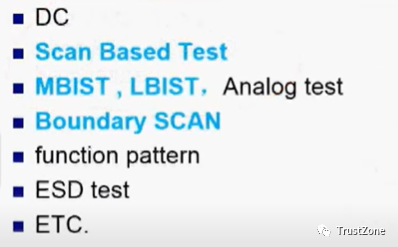

應用中正常工作。 芯片電學測試的內容非常廣泛,涉及到多個方面的測試,以下是一些常見的測試內容: 1. 電性能測試:包括電壓、電流、功耗等參數的測試。通過測試這些電性能指標,可以驗證芯片在正常工作條件下的電氣特性是否達

2023-11-09 09:36:48 2759

2759 芯片檢測是芯片設計、生產、制造成過程中的關鍵環節,檢測芯片的質量、性能、功能等,以滿足設計要求和市場需求,確保芯片可以長期穩定運行。芯片測試內容眾多,檢測方法多樣,今天納米軟件將為您介紹芯片的檢測項目都有哪些,以及檢測方法是什么。

2023-11-13 15:25:10 6789

6789 一文了解 PCB 的有效導熱系數

2023-11-24 15:48:37 3618

3618

一文了解剛柔結合制造過程

2023-12-04 16:22:19 1770

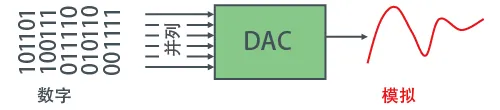

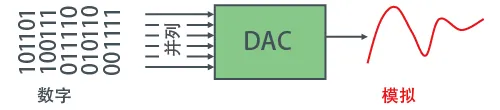

1770 一文了解 DAC

2023-12-07 15:10:36 13512

13512

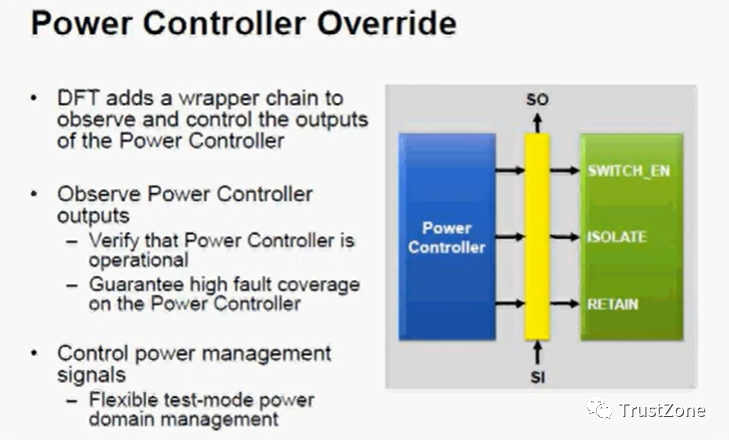

全芯片UPF低功耗設計(含DFT設計)

2023-12-29 11:43:50 1325

1325

在CDN的基礎上,融合CDN策略通過在互聯網邊緣的代理服務器上復制內容來優化內容的傳遞。這有助于減少帶寬消耗并改善用戶感知的延緩。本文討論了用于改善網絡性能的基本技術,包括對內容傳遞網絡的深入了解

2024-01-08 14:40:31 1124

1124 pcb應變測試有多重要?一文了解!

2024-02-24 16:26:35 1789

1789 接口測試是軟件測試的一個重要組成部分,主要用于驗證系統組件之間的交互是否符合預期。接口測試可以確保各個模塊之間的數據傳輸、控制流和錯誤處理等方面能夠正常工作。本文將詳細介紹接口測試的相關內容,包括

2024-05-30 15:11:03 2268

2268 作者介紹 往期推薦 德思特測試測量:一文帶您了解如何進行ADC&DAC精度測試 經過往期文章的介紹,有不少讀者希望深入了解 德思特ATX測試系統具體是如何執行ADC性能測試的 。 本文將詳細闡述

2024-06-14 10:11:11 2050

2050

SOC(System on Chip,芯片上的系統)芯片的測試是一個復雜且全面的過程,涉及多個參數和模塊。以下是對SOC芯片測試的主要參數和模塊的歸納: 一、測試參數 電性能測試 : 電壓 :包括

2024-09-23 10:13:18 4421

4421 是否在新軟件版本上再次出現。 2、測試策略 回歸測試的策略一般由測試經理或測試組長制定,初級軟件測試人員只要按相應的策略執行測試即可。現以XYC郵箱的測試為例,簡要介紹一下回歸測試的基本策略。 (1)回歸測試時執行全部的測試用例 XYC郵箱V1.0版本的第一

2024-11-14 16:44:55 1807

1807 DFT在信號處理中的應用 離散傅里葉變換(Discrete Fourier Transform,DFT)是信號處理中一個非常重要的工具。它允許我們將信號從時域轉換到頻域,從而分析信號的頻率成分。以下

2024-12-20 09:13:11 4305

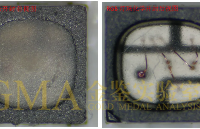

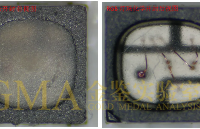

4305 芯片開封的定義芯片開封,即Decap,是一種對完整封裝的集成電路(IC)芯片進行局部處理的工藝。其目的是去除芯片的封裝外殼,暴露出芯片內部結構,同時確保芯片功能不受損。芯片開封是芯片故障分析實驗

2025-04-07 16:01:12 1120

1120

通過改進和優化設計與制造的各個方面,半導體行業已經能夠實現 IC 能力的巨大進步。可測試性設計 (DFT)——涵蓋從在 RTL 中插入測試邏輯,到對現場退回產品進行失效分析等全流程,是半導體企業獲得

2025-05-22 15:16:34 832

832

電子發燒友App

電子發燒友App

評論