現代設計規模龐大,而且非常復雜。事實上,許多 SOC比幾年前的完整子系統都要復雜。設計團隊面臨一個艱巨的挑戰,如何在緊張的設計進度內開發完整的設計。半導體開發團隊采用全面的并行設計方法來分割和并行開展大規模的開發工作。就半導體測試而言,傳統的DFT 策略考慮的是整體器件。而現在,這種可能已經不復存在了。現代 SoC 的 DFT 需要有方法能夠借助即插即用原則和自動化來解決設計規模擴大的問題。

DFT 團隊越來越頻繁地發現,由于經常需要等待部分設計的完成,自己會處在流片階段的關鍵路徑中。這些額外的流片進度風險源于管理數百個模塊內的 DFT 邏輯所需的大量(多達上千個)DFT 集成步驟。要想獲得任何成功的機會,采用完善定義的基礎結構和自動化的 DFT方法是至關重要的。要增強這些步驟的可靠性并消除修正 DFT 集成步驟所需的難以逾越的迭代數量,自動化極其重要,否則這些集成步驟可能讓項目進度完全失控。

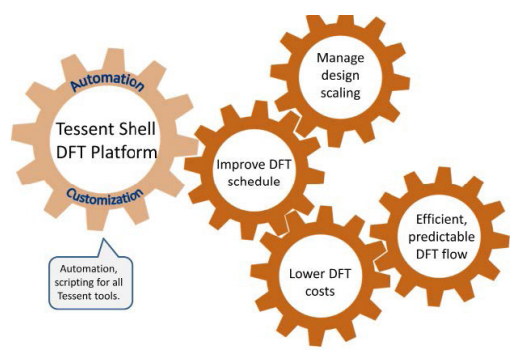

在本篇白皮書中,我們介紹了一個典型設計的 DFT 組件,并提出了多種可大幅改善 DFT 項目進度的智能 DFT 方法。我們展示了如何將結構化 DFT 和即插即用原則用于 DFT 基礎結構,來支持與其他設計開發工作相似的并行 DFT 開發和集成。自動化用于連接和管理 DFT 基礎結構,以大幅降低風險,使許多必要的流程步驟都能成功運行。設計規模的持續擴大,給設計和測試團隊增加了新的挑戰。這里介紹的 DFT 方法旨在通過即插即用原則和自動化,來解決持續的設計規模擴大問題。

圖1:DFT自動化與Tessent Shell DFT平臺相結合,降低了風險并提高了DFT流程的可預測性。

審核編輯 :李倩

-

半導體

+關注

關注

339文章

30725瀏覽量

264046 -

自動化

+關注

關注

31文章

5930瀏覽量

90222 -

DFT

+關注

關注

2文章

237瀏覽量

24039

原文標題:白皮書下載 | 利用智能的 DFT 基礎結構和自動化管理規模不斷擴大的設計

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片測試覆蓋率99%就夠了嗎?給DFT設計提個醒

TDE1708DFT智能功率開關:特性、應用與設計要點

上傳自己的組件到ESP-IDF組件注冊表

高頻測試電纜組件技術解析與應用指南

無法定位和自定義組件怎么解決?

?面向VITA應用的射頻電纜組件技術解析與實踐指南

DFT算法與FFT算法的優劣分析

如何監聽組件再次顯示的事件?

如何實現組件截圖 -- componentSnapshot

借助DFT技術實現競爭力最大化

Web Components實踐:如何搭建一個框架無關的AI組件庫

背接觸(BC)太陽能電池組件封裝損失研究:從材料選擇到工藝優化

一個典型設計的DFT組件

一個典型設計的DFT組件

評論