DFT PLL向量,ATE怎么用?

自動(dòng)測(cè)試設(shè)備 (ATE)對(duì)PLL(鎖相環(huán))進(jìn)行測(cè)試時(shí),我們首先要明白PLL在系統(tǒng)級(jí)芯片(SoC)中的重要性。它是SoC中關(guān)鍵的時(shí)鐘或信號(hào)同步部件,其性能直接影響到芯片邏輯的正確運(yùn)行。

在測(cè)試PLL IP時(shí),通常會(huì)有多個(gè)測(cè)試項(xiàng)目,如頻率測(cè)試、相位噪聲、鎖定時(shí)間、穩(wěn)定性、誤差和漂移等。

但在SoC的ATE測(cè)試中,CP階段通常只進(jìn)行PLL頻率和鎖定測(cè)試。

那么DFT如何產(chǎn)生PLL 測(cè)試pattern,以及ATE如何根據(jù)這些pattern進(jìn)行PLL測(cè)試?

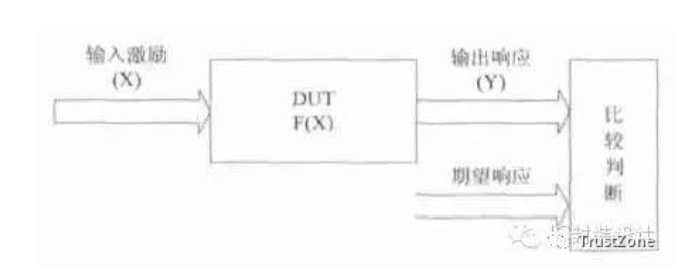

DFT(Design For Test)是用于生成測(cè)試pattern以檢測(cè)芯片功能和性能的技術(shù)。在生成PLL(Phase-Locked Loop)測(cè)試pattern的過(guò)程中,DFT通過(guò)使用特定的算法和測(cè)試向量來(lái)生成測(cè)試pattern。這些測(cè)試pattern旨在模擬PLL在不同條件下的行為,以確保芯片的PLL功能正常。

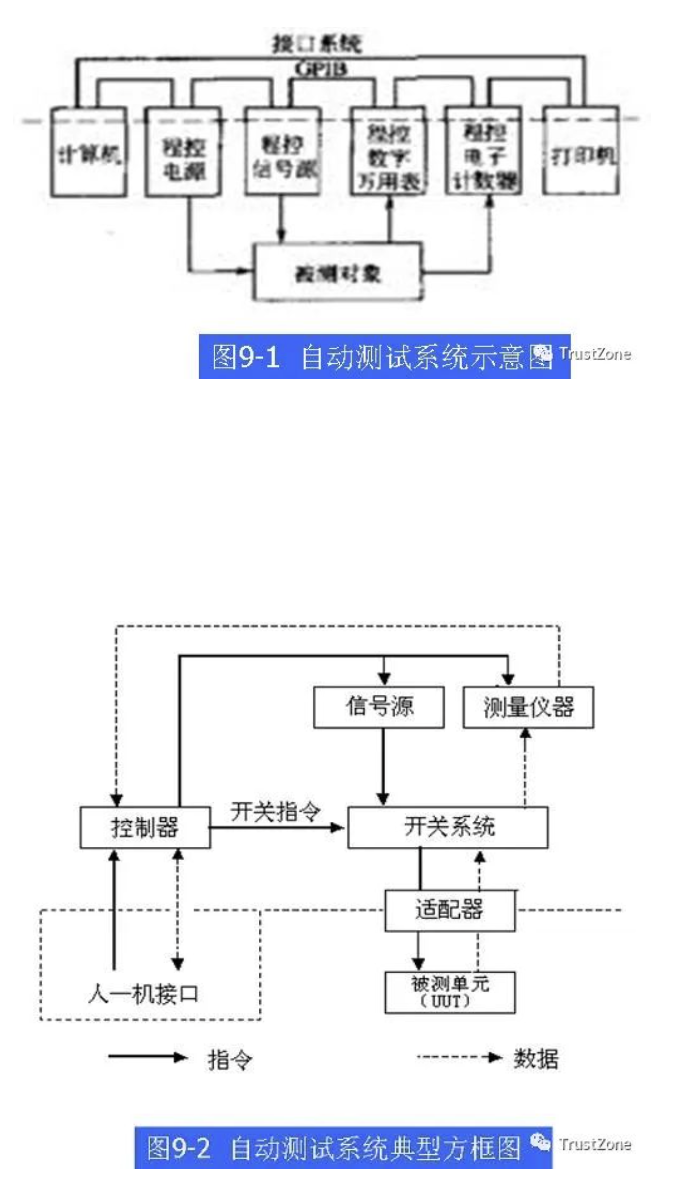

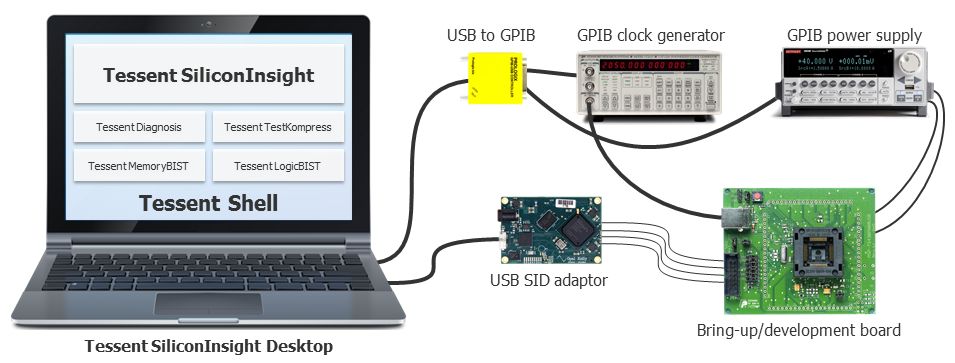

ATE(Automated Test Equipment)是一種用于自動(dòng)測(cè)試芯片性能和功能的設(shè)備。在測(cè)試PLL時(shí),ATE會(huì)使用由DFT生成的測(cè)試pattern來(lái)模擬芯片的輸入,并監(jiān)控芯片的輸出以檢查其功能是否正常。

這里的pattern指的是用于測(cè)試PLL的特定數(shù)據(jù)序列。這些數(shù)據(jù)序列在測(cè)試過(guò)程中被發(fā)送到芯片的輸入管腳,并在芯片的輸出管腳比較相應(yīng)的輸出數(shù)據(jù)序列。通過(guò)比較預(yù)期輸出和模擬輸出,ATE可以判斷PLL是否正常工作。

總之,DFT通過(guò)生成測(cè)試pattern來(lái)模擬PLL的行為,ATE使用這些測(cè)試pattern來(lái)測(cè)試芯片的功能,并比較預(yù)期輸出和模擬輸出以判斷芯片是否正常工作。

PART01 : DFT 產(chǎn)生 PLL 向量

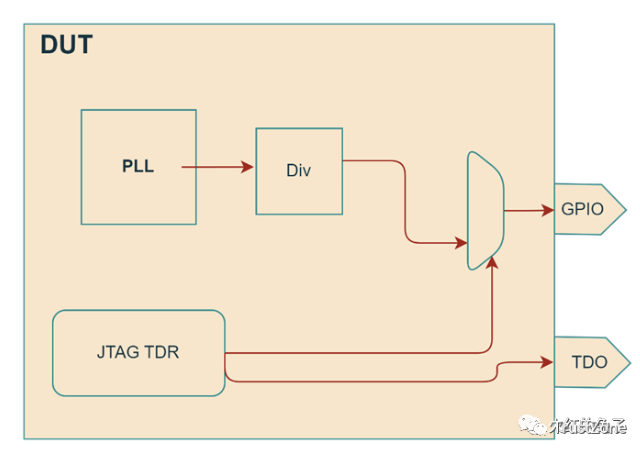

DFTer 每條PLL向量配置要求:(參考下圖)

a) JTAG配置多個(gè)PLL為對(duì)應(yīng)的待測(cè)頻點(diǎn).

b) 配置Div系數(shù)為最大,盡可能降低輸出時(shí)鐘的頻率。

c) LOCK信號(hào)在TDO串行移出觀測(cè)或者復(fù)用到IO上。

d) 切換IO復(fù)用后,PLL div 信號(hào)將會(huì)輸出到對(duì)應(yīng)GPIO上。

PLL輸出頻率的要求:10M~50M之間。 WHY?

1.上限受限于GPIO,在高于50M時(shí),GPIO的輸出特性隨頻率升高而減弱,最好低于50M。(機(jī)臺(tái)PS1600最高1.6G采樣頻率,不需要考慮奈奎斯特頻率的限制。)

2.下限需要考慮到不同測(cè)試方法的測(cè)試時(shí)間的影響,比如給一個(gè)32K的鐘,機(jī)臺(tái)需要構(gòu)造更長(zhǎng)的采樣向量。

PART02 : ATE如何測(cè)試PLL

兩種方法: 時(shí)域和頻域測(cè)試,如下:

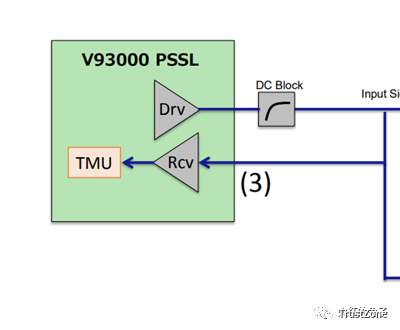

- 方法1. ATE time measurement unit ( TMU)測(cè)試。(時(shí)域,需要額外的TMU license,因此常不采用。)

實(shí)施步驟:ATE 構(gòu)造TMU TASK。TMU可以非常高精度地根據(jù)task設(shè)置trigger到上升沿的時(shí)刻,因此可以通過(guò)兩個(gè)上升沿的差值計(jì)算出頻率,支持多次采樣,如下圖所示:

- 方法2. 構(gòu)造采樣向量,離散傅里葉公式計(jì)算頻譜,頻譜的最大和第2大頻率轉(zhuǎn)換即為待測(cè)信號(hào)頻率。(頻域)

- a). 預(yù)先構(gòu)造一條全L的向量,假設(shè)叫做PLL_sample.

- b). 運(yùn)行DFT PLL向量的測(cè)試項(xiàng).運(yùn)行后, 不復(fù)位的情況下DUT此時(shí)穩(wěn)定輸出時(shí)鐘信號(hào)。

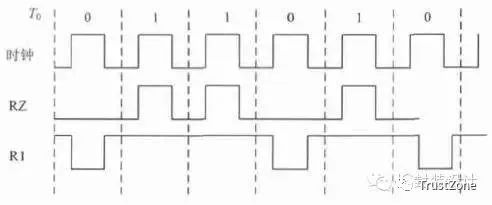

- c). 運(yùn)行預(yù)先構(gòu)造好的向量PLL_sample,收集fail cycle,也就是ATE的error map。獲得一串0/1組成的一維序列,如下圖(點(diǎn)擊可放大):

- d). 對(duì)獲得一維序列進(jìn)行漢明窗口卷積后,使用快速離散傅立葉變換獲得頻譜。通過(guò)頻譜可以相當(dāng)高精度的獲得輸出的頻率,通過(guò)spec進(jìn)行分bin。

實(shí)際步驟:首先應(yīng)用DSP_FFT與漢明窗口。然后搜索頻譜第一大主頻kmax 和第二大頻,(kmax-1 或者 kmax+1)。如圖所示,第1大和第2大頻率成為關(guān)鍵參數(shù)。

核心為兩個(gè)公式:

-

鎖相環(huán)

+關(guān)注

關(guān)注

36文章

635瀏覽量

91255 -

DFT

+關(guān)注

關(guān)注

2文章

237瀏覽量

24093 -

ATE

+關(guān)注

關(guān)注

6文章

178瀏覽量

27976 -

PLL電路

+關(guān)注

關(guān)注

0文章

94瀏覽量

7123 -

離散傅里葉變換

+關(guān)注

關(guān)注

0文章

27瀏覽量

7318

發(fā)布評(píng)論請(qǐng)先 登錄

3nm時(shí)代即將到來(lái),ATE測(cè)試機(jī)有了這些明顯變化

聊聊IC測(cè)試機(jī)(1)ATE/ATS內(nèi)部結(jié)構(gòu)簡(jiǎn)介

聊聊IC測(cè)試機(jī)(2)IC測(cè)試基本原理與ATE測(cè)試向量生成

聊聊IC測(cè)試機(jī)(3)基于ATE的IC測(cè)試原理、方法及故障分析

IC測(cè)試原理與ATE測(cè)試向量的生成

分享ATE-Connect 測(cè)試技術(shù)對(duì)加快芯片調(diào)試的作用分析

磐石測(cè)控:PS-9800S系列鍵盤(pán)模組ATE手感測(cè)試機(jī)的內(nèi)容結(jié)構(gòu)?

測(cè)試向量是什么意思

ATE如何測(cè)試PLL

ATE測(cè)試機(jī)是什么

鍵盤(pán)模組ATE手感測(cè)試機(jī):打造舒適鍵盤(pán)的關(guān)鍵利器

聊聊IC測(cè)試機(jī)(4)DFT PLL向量,ATE怎么用?

聊聊IC測(cè)試機(jī)(4)DFT PLL向量,ATE怎么用?

評(píng)論