PADS 可測(cè)試性設(shè)計(jì) (DFT) 審核可以縮短上市時(shí)間。了解如何盡早在設(shè)計(jì)流程中利用 PCB 測(cè)試點(diǎn)和 DFT 審核優(yōu)化設(shè)計(jì)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424231 -

設(shè)計(jì)

+關(guān)注

關(guān)注

4文章

826瀏覽量

71318 -

PADS

+關(guān)注

關(guān)注

82文章

821瀏覽量

111265

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

技術(shù)資訊 I PCB設(shè)計(jì)的可測(cè)試性:初學(xué)者實(shí)用指南

第一次設(shè)計(jì)PCB電路板時(shí),設(shè)計(jì)者很容易將全部精力投入到功能實(shí)現(xiàn)、布局設(shè)計(jì)和元器件選型中。而可測(cè)試性(Testability,PCB設(shè)計(jì)核心指

芯片測(cè)試覆蓋率99%就夠了嗎?給DFT設(shè)計(jì)提個(gè)醒

充分。必須將硅后驗(yàn)證向量導(dǎo)入ATPG工具進(jìn)行覆蓋率分析,否則會(huì)形成測(cè)試盲區(qū)。

二、從測(cè)試困境到DFT設(shè)計(jì)反饋

測(cè)試工程師的挑戰(zhàn)應(yīng)前置于設(shè)計(jì)階段解決。

發(fā)表于 02-06 11:06

【「龍芯之光 自主可控處理器設(shè)計(jì)解析」閱讀體驗(yàn)】+可測(cè)試性設(shè)計(jì)章節(jié)閱讀與自己的一些感想

,也分享下 自己的一些感想。 先介紹了兩個(gè)術(shù)語(yǔ)DFT可測(cè)試性 設(shè)計(jì),ATE自動(dòng)測(cè)試設(shè)備,DFT目

發(fā)表于 01-15 23:30

嵌入式可測(cè)試性軟件設(shè)計(jì)

什么是可測(cè)試性?就是你這個(gè)軟件模塊/函數(shù)接口寫完之后,可以較為方便、較為全面地進(jìn)行自測(cè) 。

這里舉個(gè)簡(jiǎn)單的例子,認(rèn)識(shí)一下可測(cè)試

發(fā)表于 12-02 06:06

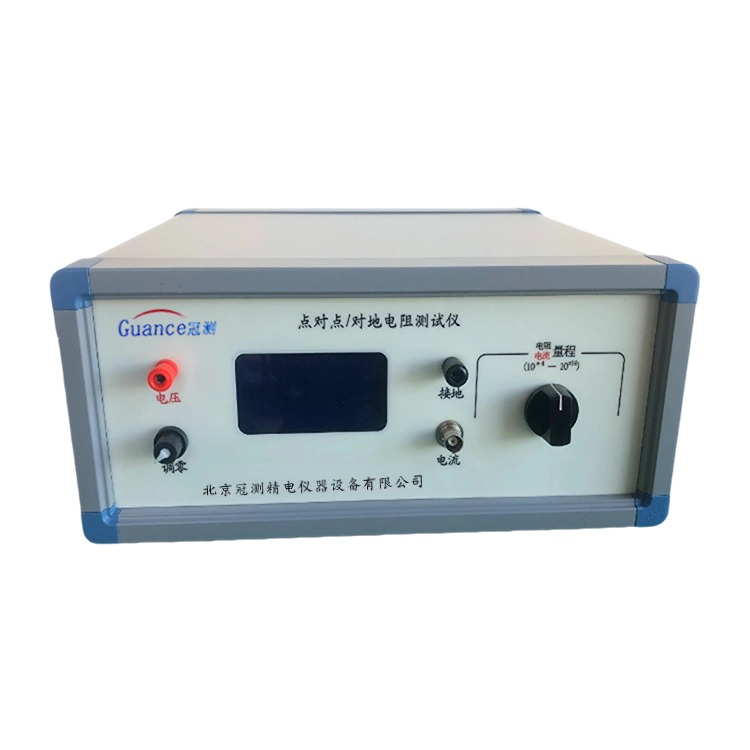

測(cè)試點(diǎn)氧化或污濁時(shí)的應(yīng)急技巧:點(diǎn)對(duì)點(diǎn)對(duì)地電阻測(cè)試如何獲得真實(shí)數(shù)據(jù)

在點(diǎn)對(duì)點(diǎn)對(duì)地電阻測(cè)試中,測(cè)試點(diǎn)的氧化、生銹或附著油污、灰塵等污濁物,會(huì)在接觸表面形成額外電阻層,導(dǎo)致測(cè)試數(shù)據(jù)虛高或波動(dòng)頻繁,難以反映真實(shí)的接地電阻狀態(tài)。面對(duì)這類突發(fā)情況,無(wú)需依賴專業(yè)清潔設(shè)備,通過(guò)

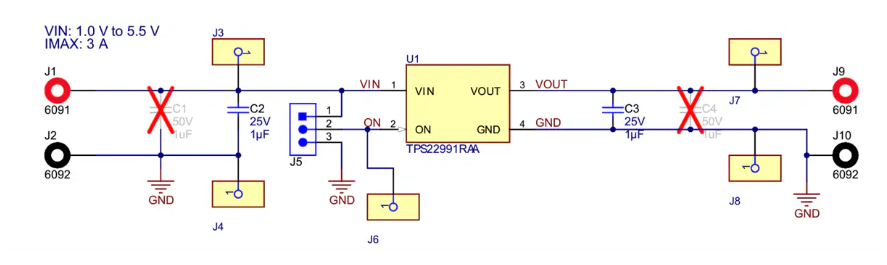

Texas Instruments TPS22991EVM評(píng)估模塊數(shù)據(jù)手冊(cè)

進(jìn)出被測(cè)器件的低電阻路徑。測(cè)試點(diǎn)連接使用戶能夠利用用戶定義的測(cè)試條件控制TI TPS22991EVM和進(jìn)行精確的R~ON~ 測(cè)量。

高壓繼電器如何提升安規(guī)與線纜測(cè)試的效率和安全性?

一過(guò)程中扮演著至關(guān)重要的角色。在多點(diǎn)高壓掃描測(cè)試中,高壓繼電器的快速切換能力能夠?qū)崿F(xiàn)不同測(cè)試點(diǎn)之間的快速切換,提高測(cè)試效率。高壓繼電器在線纜測(cè)試中的應(yīng)用線纜

標(biāo)準(zhǔn)電阻器不接PCB的地,電阻測(cè)量結(jié)果就波動(dòng)大

標(biāo)準(zhǔn)電阻器不接PCB的地,電阻測(cè)量結(jié)果就波動(dòng)大,需要電阻箱上面的接地和PCB接地測(cè)試點(diǎn)連一起,這個(gè)是因?yàn)槭裁矗且驗(yàn)?b class='flag-5'>PCB接地不能用測(cè)試點(diǎn)裸

發(fā)表于 06-17 13:08

借助DFT技術(shù)實(shí)現(xiàn)競(jìng)爭(zhēng)力最大化

通過(guò)改進(jìn)和優(yōu)化設(shè)計(jì)與制造的各個(gè)方面,半導(dǎo)體行業(yè)已經(jīng)能夠?qū)崿F(xiàn) IC 能力的巨大進(jìn)步。可測(cè)試性設(shè)計(jì) (DFT)——涵蓋從在 RTL 中插入

PCB互連應(yīng)力測(cè)試與溫度沖擊測(cè)試的區(qū)別

在當(dāng)今復(fù)雜且精密的PCB實(shí)際應(yīng)用場(chǎng)景中,確保其可靠性至關(guān)重要。互連應(yīng)力測(cè)試(IST)與溫度沖擊測(cè)試(TC)作為可靠性評(píng)估的常用手段,二者在

技術(shù)資訊 | 信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

設(shè)計(jì)和仿真測(cè)試電路板。為確保可靠性并符合行業(yè)標(biāo)準(zhǔn),高速PCB和高頻PCB必須經(jīng)過(guò)一系列測(cè)試。其中許多測(cè)試

?從設(shè)計(jì)到測(cè)試:捷多邦如何優(yōu)化PCB的電氣性能?

確保信號(hào)完整性和低損耗方面的核心技術(shù)與優(yōu)勢(shì)。 1. 信號(hào)完整性測(cè)試:從設(shè)計(jì)到驗(yàn)證 信號(hào)完整性(SI)是高速PCB設(shè)計(jì)中的關(guān)鍵指標(biāo),捷多邦通過(guò)

干簧繼電器:功能PCB測(cè)試的關(guān)鍵部件

可達(dá)數(shù)千個(gè)元件。在較大尺寸的PCB上,通常存在數(shù)千個(gè)測(cè)試點(diǎn),需要對(duì)其功能進(jìn)行檢測(cè),每個(gè)測(cè)試點(diǎn)需要多達(dá)6個(gè)開關(guān),以正確切換不同的電壓和電流,并確定其功能。

半導(dǎo)體開關(guān)存在漏電過(guò)大、缺乏隔離以及可能與實(shí)際

發(fā)表于 03-11 16:16

利用PADS可測(cè)試性設(shè)計(jì)優(yōu)化PCB測(cè)試點(diǎn)和DFT審核

利用PADS可測(cè)試性設(shè)計(jì)優(yōu)化PCB測(cè)試點(diǎn)和DFT審核

評(píng)論