內(nèi)存廣泛應用于各類電子產(chǎn)品中,內(nèi)存測試也是產(chǎn)品測試中的熱點和難點。內(nèi)存測試中最為關(guān)鍵的測試項目為DQ/DQS/CLK之間的時序關(guān)系。##Jitter Sim是力科示波器中的一個通過軟件仿真的方法實現(xiàn)信號源的功能,該功能可以實現(xiàn)時鐘信號,正弦信號,NRZ,RZ等種類多樣的碼型。

2014-01-06 14:31:02 3441

3441

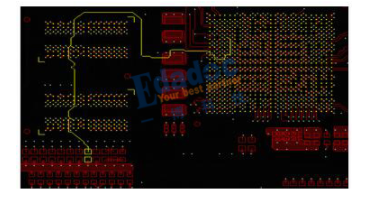

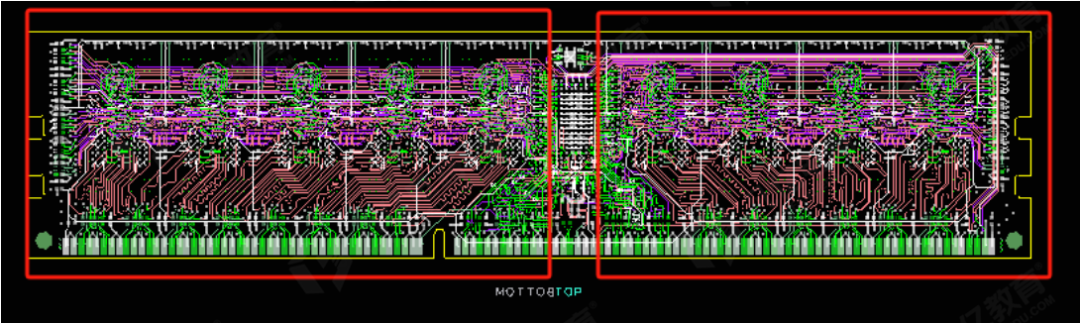

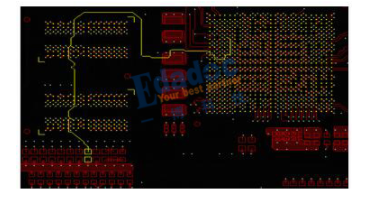

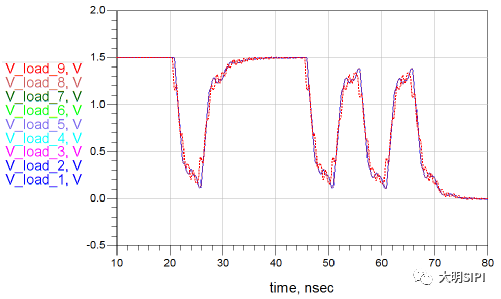

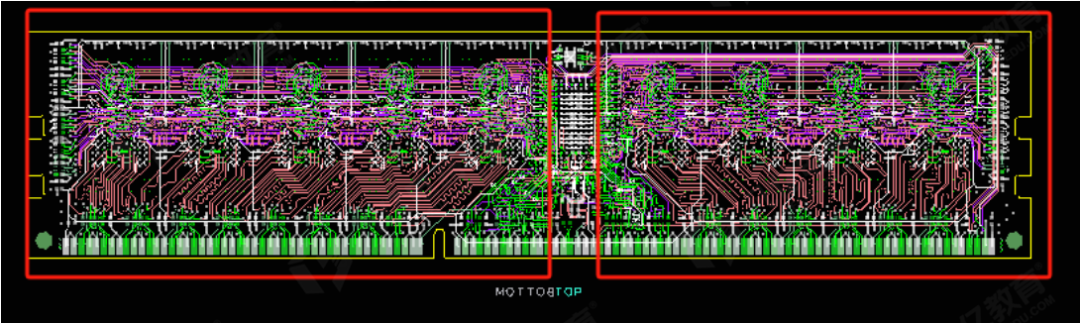

本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結(jié)果進行改進及優(yōu)化設計,提升信號質(zhì)量使其可靠性和安全性大大提高。##時序分析。##PCB設計。

2014-07-24 11:11:21 6350

6350

靜態(tài)時序分析是檢查IC系統(tǒng)時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關(guān),有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產(chǎn)品的開發(fā)周期

2020-11-25 11:03:09 11232

11232

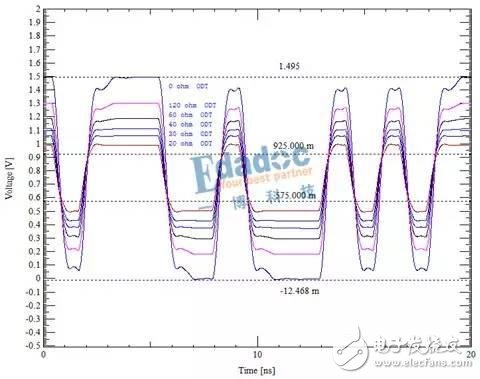

設計的信號質(zhì)量和時序裕量越來越小。因此,對高速并行總線互連設計中能夠影響信號質(zhì)量的因素進行仿真分析,盡可能提高系統(tǒng)的噪聲容限與時序裕量,對于提升系統(tǒng)的性能及可靠性,縮短研發(fā)周期,節(jié)約設計成本,具有非常重要的意義。

2022-08-30 09:55:18 972

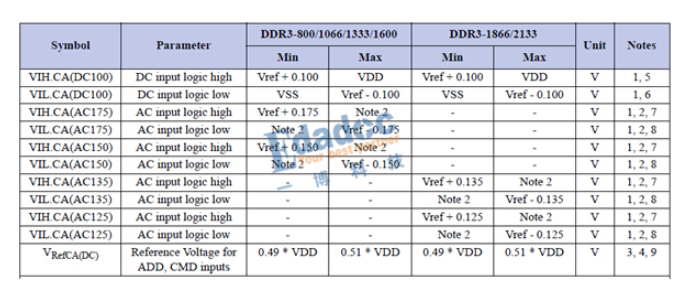

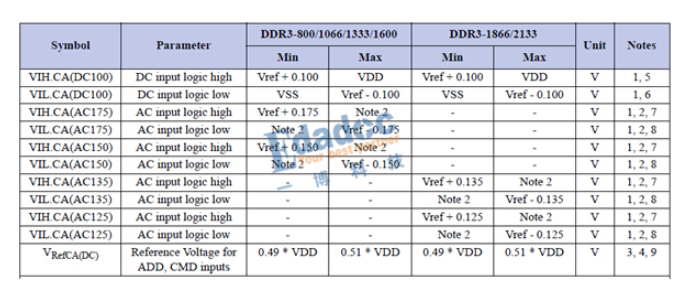

972 導讀:DDR5協(xié)議發(fā)布已經(jīng)有一段時間了,其中的變化還是比較大的,地址信號采取了ODT的端接形式,本篇文章為大家仿真一下DDR5地址信號。同時,我也推薦大家關(guān)注我在仿真秀原創(chuàng)的精品課《DDR3/4/5系列信號完整性仿真24講》,讓你清楚掌握DDR協(xié)議和仿真關(guān)鍵技術(shù)要點。

2022-12-01 10:24:03 2805

2805 信號完整性仿真重點分析有關(guān)高速信號的3個主要問題:信號質(zhì)量、串擾和時序。對于信號質(zhì)量,目標是獲取具有明確的邊緣,且沒有過度過沖和下沖的信號。

2023-04-03 10:40:07 2527

2527 DDR5已經(jīng)開始商用,但是有的產(chǎn)品還才開始使用DDR4。本文分享一些DDR4的測試內(nèi)容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達到 3200Mb/s,這樣高速的信號,對信號完整性的要求就更加嚴格,JESD79‐4 規(guī)范也對 DDR4 信號的測量提出了一些要求。

2024-01-08 09:18:24 4649

4649

mask

Enabled

Input clock period

100MHz

Chip Select pin

Enabled

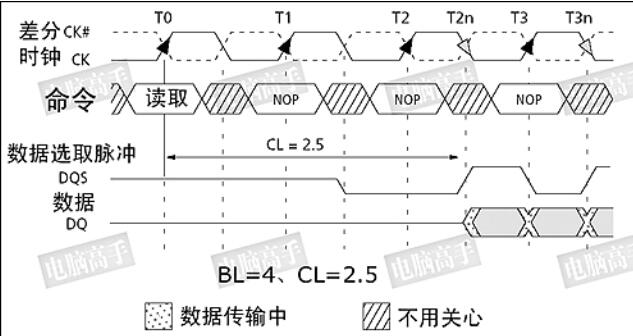

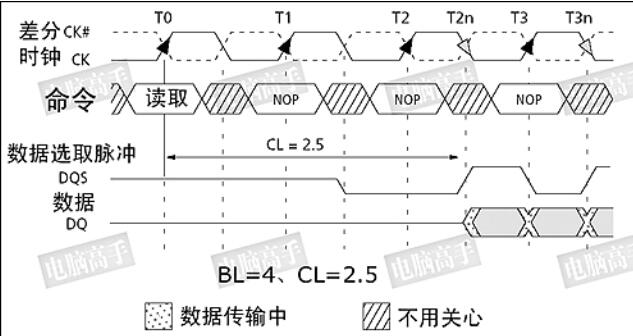

DDR讀時序介紹

DDR3讀時序如下圖,由于傳遞地址到取出數(shù)據(jù)

2025-10-28 07:24:01

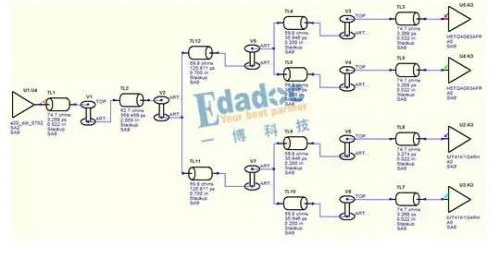

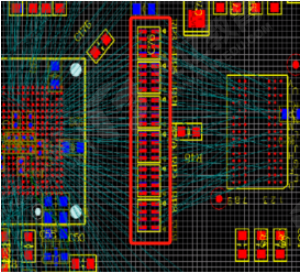

】設置仿真庫;【2】設置信號和電源的歸類,電源要賦予電壓;【3】設置層疊;【4】設置三種原件模型;【5】設置XNET網(wǎng)絡;【6】設置差分對;【7】檢查仿真的網(wǎng)絡相關(guān)設置是否正確。4、IBIS模型到

2020-07-06 16:09:27

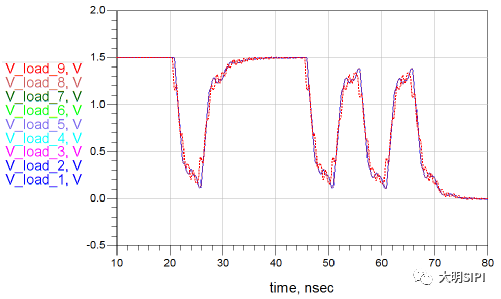

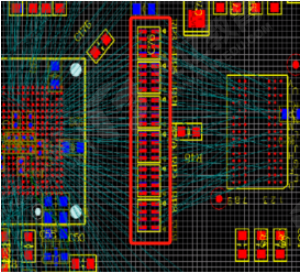

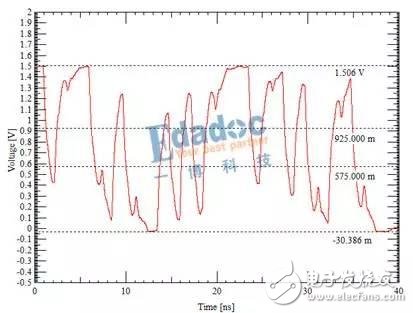

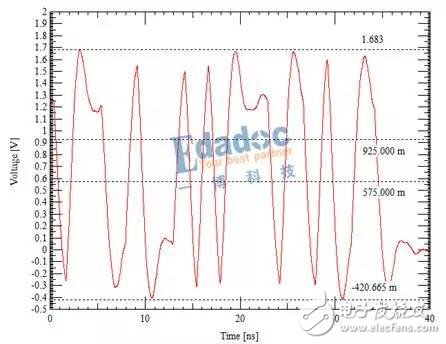

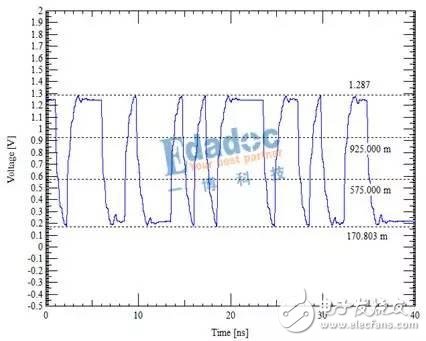

孤立銅的存在。 5 PCB板后仿驗證 DDR3的PCB設計結(jié)束后進行后仿分析,用以對前面的仿真分析進行驗證。PCB板后仿主要是對DDR3信號質(zhì)量和時序關(guān)系進行分析。 5.1 DDR3的差分時鐘驗證

2014-12-15 14:17:46

作者:黃剛DDR仿真作為一個非常普遍的仿真模塊,基本上入門SI行業(yè)的人都會首先接觸到。記得本人剛接觸這個行業(yè)的時候,也是先接觸DDR模塊的仿真。從DDR2到DDR4,可能很多同行都一直使用同一

2019-07-24 06:56:33

DDR布線在pcb設計中占有舉足輕重的地位,設計成功的關(guān)鍵就是要保證系統(tǒng)有充足的裕量。要保證系統(tǒng)的時序,線長又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號

2018-09-20 10:29:55

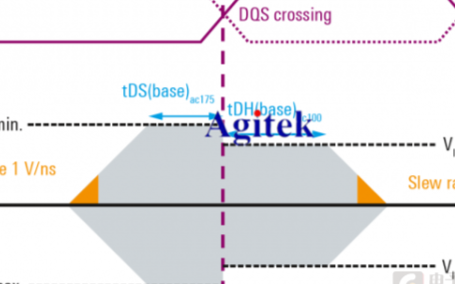

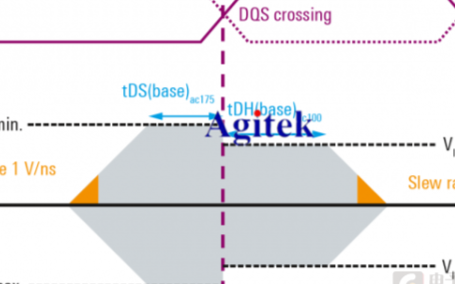

上篇文章我們用仿真實例向大家展示了DDR中地址相對于時鐘的建立時間與保持時間。那么數(shù)據(jù)信號相對于DQS又是什么樣的關(guān)系呢?我們知道,DDR和普通的SDRAM相比起來,讀取速率為普通SDRAM的兩倍

2016-11-08 16:59:51

時間的時序裕量不足,我們知道,時序裕量問題的確也是可以通過降頻來彌補的,因此我們對仿真的精度有了更大的信心!好!最后再試一種組合,一定要成功!就是地址控制信號和CLK時鐘都選用MEDIUM模式,我們先來

2023-02-02 13:45:09

本帖最后由 一只耳朵怪 于 2018-5-25 14:46 編輯

TI工程師: 您好,我在官網(wǎng)上下載了DM368的IBIS模型,仿真DDR2時,DM368的DDR2地址信號和其它控制信號,以及

2018-05-25 07:24:50

時序分析-- 信號完整性問題(SI)

2014-05-16 10:44:11

Altium Designer的混合電路信號仿真工具,在電路原理圖設計階段實現(xiàn)對數(shù)模混合信號電路的功能設計仿真,配合簡單易用的參數(shù)配置窗口,完成基于時序、離散度、信噪比等多種數(shù)據(jù)的分析。Altium

2019-07-19 07:52:07

地傳送到接收端,就必須進行精確的時序計算和分析。同時,時序和信號完整性也是密不可分的,良好的信號質(zhì)量是確保穩(wěn)定的時序的關(guān)鍵,由于反射,串擾造成的信號質(zhì)量問題都很可能帶來時序的偏移和紊亂。因此,對于一個信號

2012-08-11 17:55:55

ORCAD16.3 仿真的 VSIN信號 相位沒有設置的嗎?

2017-07-25 13:31:33

,兩者相差12.78ps,與仿真結(jié)果的12.5ps相吻合。上述,我們通過理論和仿真的驗證分析,知道了在線長相等的情況下微帶線和帶狀線會存在時延差異以及導致差異的原因,那在布線設計中,對于一些速率較高,時序要求嚴格的信號,如DDR的數(shù)據(jù)信號,建議采用同組同層進行布線的原因之一正是如此。

2022-12-01 09:48:01

一下具體波形。 建立如下通道,分別模擬3的地址信號與時鐘信號。 圖1 地址/時鐘仿真示意圖 為方便計算,我們假設DDR的時鐘頻率為500MHz,這樣對應的地址信號的速率就應該是500Mbps

2018-09-20 10:59:44

自己做了一個工程,靜態(tài)時序分析的結(jié)果CLK信號的SLACK是負值(-7.399ns),書上說該值是負值時說明時序不對,但是我感覺時序仿真的結(jié)果是對的。是不是時序仿真波形正確就不用管靜態(tài)時序分析的結(jié)果了?請高手指點

2010-03-03 23:22:24

本文針對以上問題對本人設計的主板PCB的高速信號基本噪聲,高速內(nèi)存時序和電源分配系統(tǒng)噪聲進行分析和設計;采用軟件仿真的方法對問題進行分析,得出設計解決方案,并將仿真結(jié)果轉(zhuǎn)化為設計約束規(guī)則指導PCB布局布線設計,最后通過物理測試對設計進行了驗證。回復帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:02:40

工程師也知道這種情況下,應該和設計人員普及一下關(guān)于時序方面的知識,不然后續(xù)遇到類似的DDR,不做仿真的話,可能會需要降頻運行。于是將U1的仿真結(jié)果給設計人員看,藍色的是CS,ODT,CKE等信號,綠色

2019-06-20 09:06:44

什么情況,我們需要DDR信號仿真分析呢?

2021-03-17 07:38:51

時就能看到像在功能仿真的工程文件層次結(jié)構(gòu),可以找到定義的內(nèi)部信號。因為在做后仿時,源文件中的信號名稱已經(jīng)沒有了,被映射為軟件綜合后自己生成的信號名,觀察起來很不方便。這個設置與ISE里綜合右鍵屬性

2012-03-01 11:46:29

功能仿真:可以驗證代碼的邏輯性,不加任何的時延信息。仿真工具為modelsim(組合邏輯和時序邏輯都可以功能仿真),modelsim不能綜合。在modelsim中添加相應的激勵信號,調(diào)用

2016-08-23 16:57:06

的選定輸出作為驅(qū)動,并考慮所有已設置的有效終止方式,來進行詳細的信號反射仿真。仿真結(jié)果以圖形方式顯示在波形分析器中。 波形分析器 使用波形分析器可以方便地顯示出反射仿真和串擾仿真的結(jié)果,并可以直接

2018-08-27 16:13:55

引起誤觸發(fā)。Cadence Allegro 17.2反射仿真分析流程中怎么進行信號分析?【1】Cadence Allegro 17.2啟動后選擇Allegro Sigrity SI產(chǎn)品就可以啟動

2020-03-16 11:20:19

線性的均衡基礎上加上了一個額外的判決功能。通過仔細閱讀DDR5協(xié)議,可以看到,DDR5的data信號標準配置是一個4tap的DFE模塊。 好,關(guān)于協(xié)議和理論都太過枯燥,說點仿真的東西吧。我們直接拿到

2021-08-27 16:39:08

時。如果我查看發(fā)送的數(shù)據(jù)和數(shù)據(jù)從內(nèi)存中讀回并存儲在fifo中,chipcope cdc會導致時序約束失敗并且還會改變設計的時序性能,因此我無法捕獲可靠的數(shù)據(jù)。我嘗試將DDR2信號路由到另一組I / O

2019-05-10 14:25:23

數(shù)字信號時序分析裝置畢業(yè)設計,本人來自中國地質(zhì)大學通信工程專業(yè),2020學年大二上的通信與信號處理的實習題目便是參考2018年TI杯G題——數(shù)字信號時序分析裝置,此實習需要自學stm32單片機,具有

2021-08-09 08:33:45

求助一篇關(guān)于信號波形仿真的課程設計利用matlab設計出原理框圖和主要參數(shù)以及程序

2012-12-24 10:47:38

Flyby拓撲和T拓撲的組合,所以既有Flyby拓撲的特點,也就是近端顆粒的信號質(zhì)量特別差;也有T拓撲的特點,近端的DRAM1和DRAM2一樣差。小雷的仿真結(jié)果也驗證了這一點,上一版近端顆粒的眼圖(地址信號

2022-05-11 09:11:48

的stub對信號質(zhì)量的影響分析。 那主要肯定是講過孔stub(殘樁)對DDR4的影響咯。首先呢作者對DDR4的信號質(zhì)量做了一些前提的判定和分析,例如要求通道的插損諧振頻率點要大于5倍的時鐘頻率,按本文

2020-02-28 17:13:27

高速電路信號完整性分析與設計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

高速電路信號完整性分析與設計—時序計算引入:在數(shù)字電路中,從一個芯片發(fā)信息A到另一個芯片變成信息B,那么這個數(shù)字系統(tǒng)失敗;如何保證信息不變?關(guān)鍵點,就是在傳輸過程的任意點都保持時序的正確性。時序概念

2009-09-12 10:28:42

ISA總線信號時序簡介:1.0 ISA概況2.0 ISA文獻2.1 ISA規(guī)范2.2 ISA書籍3.0 ISA結(jié)構(gòu)形式4.0 PC/104結(jié)構(gòu)形式5.0 ISA信號描述6.0 ISA時序圖7.0 ISA信號用法8.0 ISA連接器引腳

2009-05-21 11:06:54 242

242 用ModelSimSE進行功能仿真和時序仿真的方法(ALTERA篇)(ALTERA 篇)軟件準備(1) QuartusII,本文截圖是QuartusII 6.1 界面的。我個人認為,如果是開發(fā)StratixII 或CycloneII 或MAXII

2009-06-19 00:26:41 70

70 高速電路信號完整性分析與設計—時序計算:基本概念引入:在數(shù)字電路中,從一個芯片發(fā)信息A到另一個芯片變成信息B,那么這個數(shù)字系統(tǒng)失敗;如何保證信息不變?關(guān)鍵點,就

2009-10-06 11:08:19 0

0 高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 各種液晶屏信號描述及時序分析:TFT 液晶屏接口(數(shù)字屏)信號說明VSYNC: vertical synchronization [siŋkrənaizeiʃə

2010-03-18 17:47:58 47

47 信號完整性和時序分析的模式變化:簡單的接口分析經(jīng)驗法則在分析現(xiàn)代高速接口(如DDR2、PCI Express和SATA-II)時非常不合適。隨著新興標準(如DDR3 和5-10 Gbps串行接口)逐漸普及,

2010-04-27 08:25:54 70

70 新一代數(shù)字RF信號分析和信號仿真系統(tǒng)測試:• 雷達和寬帶通信系統(tǒng)的測試挑戰(zhàn)

• 將“實時分析”的方法帶入寬帶系統(tǒng)測試

• 為寬帶系統(tǒng)測試提供所需帶

2010-08-05 14:45:10 46

46 定義了時鐘單位階躍信號C(n) 提出了一種利用帶相對時鐘坐標的邏輯方程表示邏輯信號的方法通過對所設計的DDR SDRAM控制器的讀寫時序的分析建立了控制器主要信號的時序表達式并利用

2011-09-26 15:34:12 39

39 介紹引起信號完整性問題的主要因素, 利用。進行信號仿真的步驟, 給出了的信號仿真的時比結(jié)果, 并以該信號作為分析對象, 詳細分析了為判斷信號質(zhì)童的優(yōu)劣, 對仿真波形進行定量分析

2011-11-30 11:09:46 0

0 為了使設計人員對信號完整性與電源完整性有個全面的了解,文中對信號完整性與電源完整性的問題進行了仿真分析與設計,也從系統(tǒng)的角度對其進行了探討。

2011-11-30 11:12:24 0

0 文中主要以Matlab為平臺,對GPS信號的信號結(jié)構(gòu)(數(shù)據(jù)信號,C/A碼)、GPS的多種干擾方式進行仿真,并分析了不同干擾的干信比與誤碼率關(guān)系。

2011-12-14 14:37:11 101

101 通過Cadence軟件建立DDRⅡ信號拓撲結(jié)構(gòu)、仿真信號的串擾、碼間干擾、過沖等與信號質(zhì)量相關(guān)的參數(shù),從仿真波形中可以測量出與信號時序相關(guān)的參數(shù),從而計算出信號的時序裕量,并為DDRⅡ

2012-02-13 15:16:22 52

52 文中以基于FPGA設計的高速信號下載器為例,從LVDS的PCB設計,約束設置和信號完整性仿真等多方面研究LVDS信號的實現(xiàn)。

2012-04-20 10:37:02 59

59 ALTERA公司:用ModelSimSE進行功能仿真和時序仿真的方法(ALTERA篇)之學習筆記

2012-08-15 16:00:59 68

68 ddr2_sdram 操作時序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 21

21 MATLAB環(huán)境下的跳頻信號分析與仿真.

2016-01-15 15:15:57 36

36 24C02中IIC總線的應答信號(ACK)時序圖分析,很好的單片機學習資料。

2016-03-21 17:30:06 94

94 10129@52RD_信號完整性與電源完整性的仿真分析與設計

2016-12-14 21:27:39 0

0 雙頻GPS信號仿真的電離層誤差補償模型研究_謝杰

2017-03-14 08:00:00 1

1 最新版本的李黎明DDR時序PPT

2017-11-02 17:05:17 0

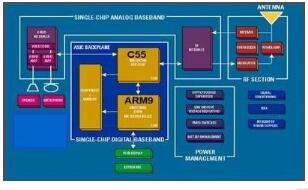

0 。解決了DDR SDRAM的差分時鐘信號的反射問題和視頻信號的串擾問題。本嵌入式系統(tǒng)經(jīng)過實際調(diào)試后的時鐘信號和視頻信號滿足設計要求,系統(tǒng)能夠穩(wěn)定工作。因此,在高速電路設計中,利用信號完整性理論進行仿真分析,對于指導工程實踐具有重要的意義。

2017-12-01 17:16:01 1651

1651

高速 PCB 信號完整性仿真分析.pdf

2018-05-07 14:52:31 52

52 Random Access Memory的縮寫,即同步動態(tài)隨機存取存儲器。本文首先介紹了DDR工作原理及結(jié)構(gòu)圖,其次闡述了DDR DQS信號的處理,具體的跟隨小編一起來了解一下。

2018-05-23 16:07:19 55913

55913

本文主要介紹了基于Multisim仿真的交通信號燈設計.

2018-06-28 08:00:00 80

80 對于Layout人員來說,對于DDR這一塊,可能主要關(guān)注的是信號線之間的等長。下面我們也來復習一下,DDR各組信號需要滿足的時序關(guān)系:地址/命令,控制和時鐘之間等長;DQ與之對應的DQS組內(nèi)等長;DQS與CLK之間有一個相對寬松的等長關(guān)系。

2018-09-15 10:58:00 6845

6845 Altium Designer的混合電路信號仿真工具,在電路原理圖設計階段實現(xiàn)對數(shù)模混合信號電路的功能設計仿真,配合簡單易用的參數(shù)配置窗口,完成基于時序、離散度、信噪比等多種數(shù)據(jù)的分析。Altium

2018-09-12 08:00:00 0

0 針對 DDR2高速電路中存在的信號完整性問題進行了分析,提出了PCB設計要點。并以單個DDR2存儲器與控制器間的 PCB設計為例,對如何在減少仿真工作的情況下成功完成一個可用的設計進行了論述。

2019-03-04 08:00:00 0

0 在普通印制電路板的布線中由于信號是低速信號,所以在3W原則的基本布線規(guī)則下按照信號的流向?qū)⑵溥B接起來,一般都不會出現(xiàn)問題。但是如果信號是100M以上的速度時,布線就很有講究了。由于最近布過速度高達300M的DDR信號,所以仔細說明一下DDR信號的布線原則和技巧。

2019-03-24 10:00:06 8668

8668

信號完整性的問題主要包括傳輸線效應,如反射、時延、振鈴、信號的過程與下沖以及信號之間的串擾等,涉及傳輸線上的信號質(zhì)量及信號定時的準確性。

良好的信號質(zhì)量是確保穩(wěn)定時序的關(guān)鍵。由于反射和串擾造成

2019-06-24 15:27:25 1803

1803

因高速問題產(chǎn)生的信號過沖、下沖、反射、振鈴、串擾等將嚴重影響系統(tǒng)的正常時序,系統(tǒng)時序余量的減少迫使人們關(guān)注影響數(shù)字波形時序和質(zhì)量的各種現(xiàn)象。由于速度的提高使時序變得苛刻時,無論事先對系統(tǒng)原理理解得多么透徹,任何忽略和簡化都可能給系統(tǒng)帶來嚴重的后果。

2019-06-03 15:18:15 1091

1091 本文檔的主要內(nèi)容詳細介紹的是51單片機按鍵檢測和信號函數(shù)仿真的詳細資料說明,在單片機中會遇到識別按鍵的問題,常用的獨立按鍵電路如下圖:

2019-04-11 18:22:00 4

4 學習如何墊分析工具可以識別你的電路設計仿真的關(guān)鍵區(qū)域。我們將研究如何分析和快速實現(xiàn)信號和電源完整性和突出關(guān)鍵原因墊桌面仿真和驗證是你最好的選擇。

2019-11-01 07:10:00 3780

3780 工程師要快速檢查信號質(zhì)量,眼圖測試有助于在極短時間內(nèi)獲悉信號完整性狀況。 測試 DDR 接口信號質(zhì)量時,數(shù)據(jù)眼圖分析有助于揭示潛在的信號完整性問題。因此,許多信號完整性工程師都使用眼圖功能迅速測定

2020-07-23 15:50:45 8625

8625

通常,DDR設計完成之后 ,對信號質(zhì)量并沒有一個完全確定的概念,需要我們通過仿真和測試的手段去判斷和驗證。而此時,往往我們拿到的就是一個波形,測試波形或者仿真波形,該如何去判斷其信號質(zhì)量,參照的標準

2021-04-09 10:04:19 6961

6961

一般會選擇什么拓撲結(jié)構(gòu)呢?我想,這個應該和個人的設計習慣有關(guān),或者選擇T拓撲,或者選擇Fly-by,沒有標準答案。但是作者最近遇到的一個項目,一個主控拖動兩個DDR顆粒,采用Fly-by結(jié)構(gòu),信號質(zhì)量就不穩(wěn)定,小批量量產(chǎn)總有幾塊板子DDR不能正常工

2021-04-08 12:06:48 4025

4025

今天要給大家分享的文章如下,這次的題目很容易讀懂,就叫DDR4通道里,過孔的stub對信號質(zhì)量的影響分析。 那主要肯定是講過孔stub(殘樁)對DDR4的影響咯。首先呢作者對DDR4的信號質(zhì)量做了

2021-03-23 11:46:59 7894

7894 一些設計方法在以前已經(jīng)成熟的使用過。 1 介紹 目前,比較普遍使用中的DDR2的速度已經(jīng)高達800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已經(jīng)高達1600 Mbps。 對于如此高的速度,從PCB的設計角度來幫大家分析,要做到嚴格的時序匹配,以滿足信號的完整性,

2021-03-25 14:26:01 5336

5336

電子發(fā)燒友網(wǎng)為你提供什么情況,我們需要DDR信號仿真分析呢?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-30 08:44:49 14

14 Hyperlynx信號完整性仿真性分析。

2021-04-07 13:59:10 144

144 高速電路信號完整性分析與設計—時序計算

2022-02-10 17:16:41 0

0 高速電路信號完整性分析與設計—信號完整性仿真

2022-02-10 17:29:52 0

0 華為硬件信號質(zhì)量與時序測試指導書

硬件信號測試用例

建立保持時間

信號質(zhì)量等測量方法

2022-10-21 16:18:29 38

38 定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質(zhì)量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續(xù)時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現(xiàn)了信號完整性問題。

2022-11-16 14:56:00 6200

6200 隨著信號速率的不斷提高,對信號時序的要求也越來越嚴格。在PCB設計中,我們等長的最終目的都是為了等時,以滿足信號的時序要求。因此,需要我們對信號在傳輸線上的時延有一定的了解,下面小編將會通過理論分析和利用SIGRITY軟件進行仿真驗證跟大家一起深入的了解信號在傳輸線上的時延情況。

2022-12-01 09:46:17 1286

1286 信號的時序要求就是數(shù)據(jù)信號與其對應的時鐘信號保持某種同步關(guān)系。數(shù)據(jù)的采樣同樣依賴于某特定的時鐘,由于信號邊沿頻譜高最容易受干擾,因此在采樣時鐘對數(shù)據(jù)信號進行采樣時,應盡可能遠離信號變化的邊沿。

2023-03-08 15:38:00 2740

2740 目前對于DDR4、DDR5等并行信號,信號速率越來越高,電源性能要求也越來越高,今天我們就來看看電源噪聲對信號質(zhì)量的影響;

2023-04-21 09:47:46 3328

3328 這里介紹兩種方式改善帶有ECC的奇數(shù)負載的DDR2信號質(zhì)量。一種不需要改變拓撲結(jié)構(gòu),另一種需要對拓撲結(jié)構(gòu)進行調(diào)整。

2023-06-15 17:39:34 1458

1458

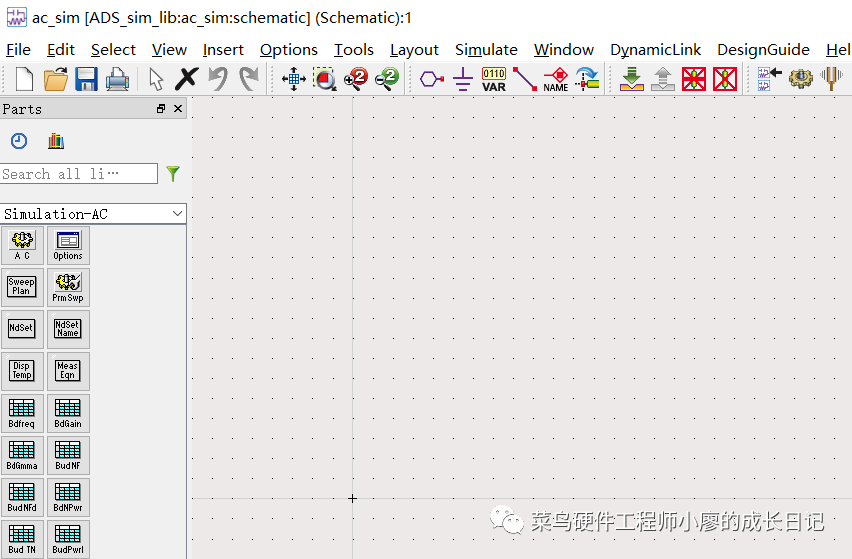

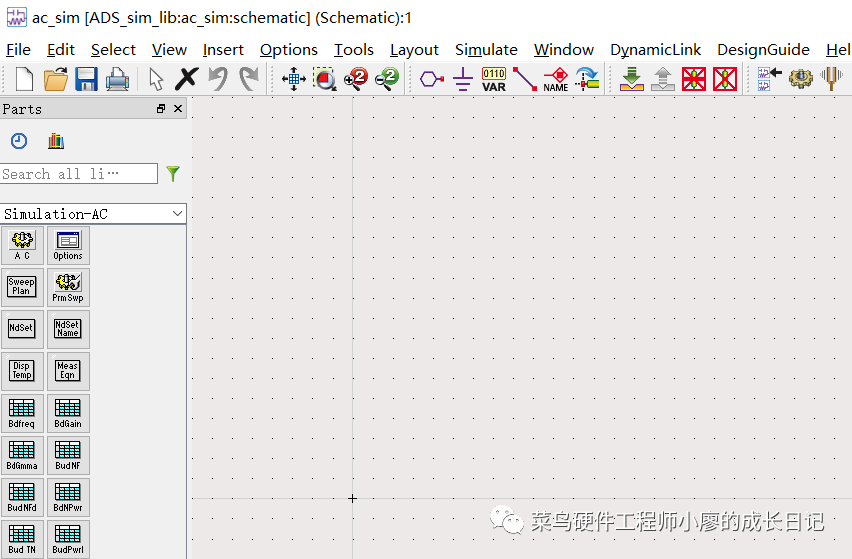

交流仿真的概念:交流放著是射頻電路中最重要的仿真方式之一,主要用于分析電路的小信號特性和噪聲特性。

2023-06-29 11:17:31 19894

19894

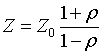

當信號進入射頻后,阻抗匹配變得十分重要,差的匹配造成的反射將嚴重影響信號質(zhì)量,甚至可能造成誤操作,因此必須以傳輸線理論進行分析,即印制電路板上每條連線都有其特性阻抗。

2023-07-03 11:29:24 5549

5549

何為信號完整性的分析信號完整性包含:波形完整性(Waveformintegrity)時序完整性(Timingintegrity)電源完整性(Powerintegrity)信號完整性分析的目的就是用

2023-08-17 09:29:30 8719

8719

時序仿真與功能仿真的區(qū)別在于 時序仿真與功能仿真是電子設計自動化(EDA)中最常見的兩種仿真方式。雖然二者都是仿真技術(shù),但根據(jù)仿真模型和目的的不同,它們之間還是存在一些根本差異。 1.定位 時序仿真

2023-09-08 10:39:40 7141

7141 EDA仿真,它模擬一個數(shù)字電路中時序的行為。時序行為通常包括數(shù)據(jù)信號傳輸?shù)?b class="flag-6" style="color: red">時序,如周期時間或LATCH信號的上升沿下降沿。它通常應用于驗證設計延遲、時序、時序違規(guī)和時序沖突等問題。 時序仿真的主要目的是在設計的任何階段,從RTL級別

2023-09-17 14:15:02 8348

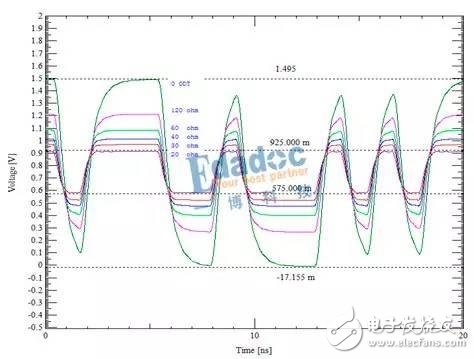

8348 數(shù)據(jù)線都有串聯(lián)一個電阻,其實這個串聯(lián)電阻的作用是進行阻抗匹配的,防止信號發(fā)生反射。 我們接下來用allegro軟件自帶的sigxplorer軟件進行仿真驗證一下, 我們主要分析驗證一下這個電阻他是如何進行阻抗匹配以及電阻阻值應該如何選取! 首先我們需要按

2023-11-06 07:45:02 1491

1491

是指在芯片設計過程中,對電路的功能和性能進行仿真驗證的環(huán)節(jié)。它主要關(guān)注電路的功能性、時序和功耗等方面,以確保設計的正確性和可行性。前仿真通常在物理布局之前進行,因此也稱為靜態(tài)時序分析或網(wǎng)表級仿真。 后仿真:后仿

2023-12-13 15:06:55 11539

11539 DDR采用菊花鏈拓撲結(jié)構(gòu)時,由于信號傳輸線較長通常需要在DDR末端加上終端匹配電阻,端接的方式有很多,但是都是為了解決信號的反射問題,通常為了消除信號的反射可以在信號的源端或者終端進行解決,在源端處

2023-12-25 07:45:01 1424

1424

DDR加終端匹配電阻和不加信號質(zhì)量的區(qū)別? DDR(雙倍數(shù)據(jù)傳輸速率)是一種常用于計算機內(nèi)存的高速數(shù)據(jù)傳輸技術(shù)。在DDR中,終端匹配電阻和信號質(zhì)量是對于數(shù)據(jù)傳輸穩(wěn)定性至關(guān)重要的兩個方面。下面將詳細

2023-12-29 13:54:22 2012

2012 FPGA時序仿真和功能仿真在芯片設計和驗證過程中各自扮演著不可或缺的角色,它們之間存在明顯的區(qū)別。

2024-03-15 15:28:40 3703

3703 扮演著關(guān)鍵角色。本文將詳細闡述頻譜分析儀測量信號失真的原理、方法以及應用,并探討其在實際工作中的重要作用。

2024-05-23 17:37:34 2288

2288 電子發(fā)燒友網(wǎng)站提供《超高速數(shù)據(jù)采集系統(tǒng)的時序設計與信號完整性分析.pdf》資料免費下載

2024-09-20 11:34:36 0

0 在進行DDR(雙倍數(shù)據(jù)速率)信號測試時,普源DHO1072示波器是一款功能強大的工具,能夠幫助用戶準確分析和調(diào)試信號。以下是使用普源DHO1072示波器進行DDR信號測試的幾個關(guān)鍵要點。 一

2025-03-14 12:06:00 942

942

據(jù)統(tǒng)計,超過60%的硬件返修源于信號反射、串擾或時序偏差,而傳統(tǒng)依賴仿真的設計方法往往耗時且成本高昂。本文揭示7種經(jīng)過實測驗證的走線拓撲調(diào)整策略,無需深度仿真即可實現(xiàn)90%的信號質(zhì)量優(yōu)化,尤其適用于

2025-07-15 19:16:13 2094

2094

電子發(fā)燒友App

電子發(fā)燒友App

評論