Altium中的信號完整性分析包括檢查信號上升時間,下降時間,提供終端方案和進行串擾分析的能力。您還可以定義模型并設置規則和約束以及信號完整性分析相關的其它設置。一旦確認了串擾問題,就可以根據需要修改相同層或相鄰層的布線路徑。

2020-08-25 15:50:00 10700

10700

歡迎來到 “掌握 PCB 設計中的 EMI 控制” 系列的第六篇文章。本文將探討串擾如何影響信號完整性和 EMI,并討論在設計中解決這一問題的具體措施。

2025-08-25 11:06:45 9572

9572

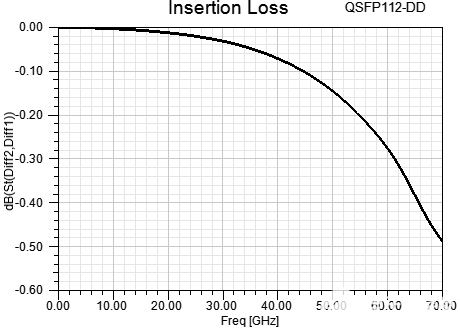

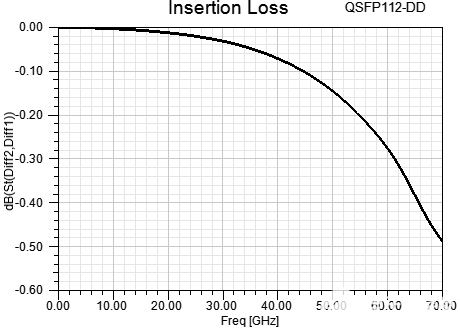

越高的速率傳輸,意味著更快的上升沿和更高的帶寬,這必然會為信號完整性帶來極大的挑戰。要滿足所需的插損、回損、TDR和串擾等,必然要進行高速信號完整性仿真。

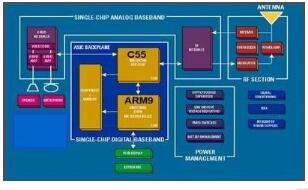

以800G DAC為例,高速信號

2022-07-15 16:01:02 2447

2447

通常說的信號完整性就是指信號無失真的進行傳輸。前面我們討論很多信號完整性問題,包括時序、串擾、衰減、反射、電源完整性、EMC等等。

2022-09-29 17:00:06 1723

1723 在實際的應用場景中,會遇到多種信號完整性問題,典型問題有如下幾種:反射、串擾,電源/地噪,時序等。其中,發射和串擾是引起信號完整性問題的兩大主要原因。

2022-10-09 10:56:55 5453

5453 定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2023-03-02 09:41:06 2281

2281

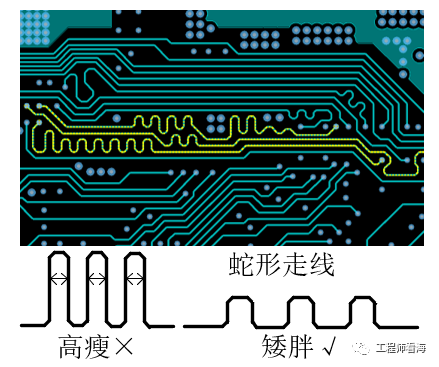

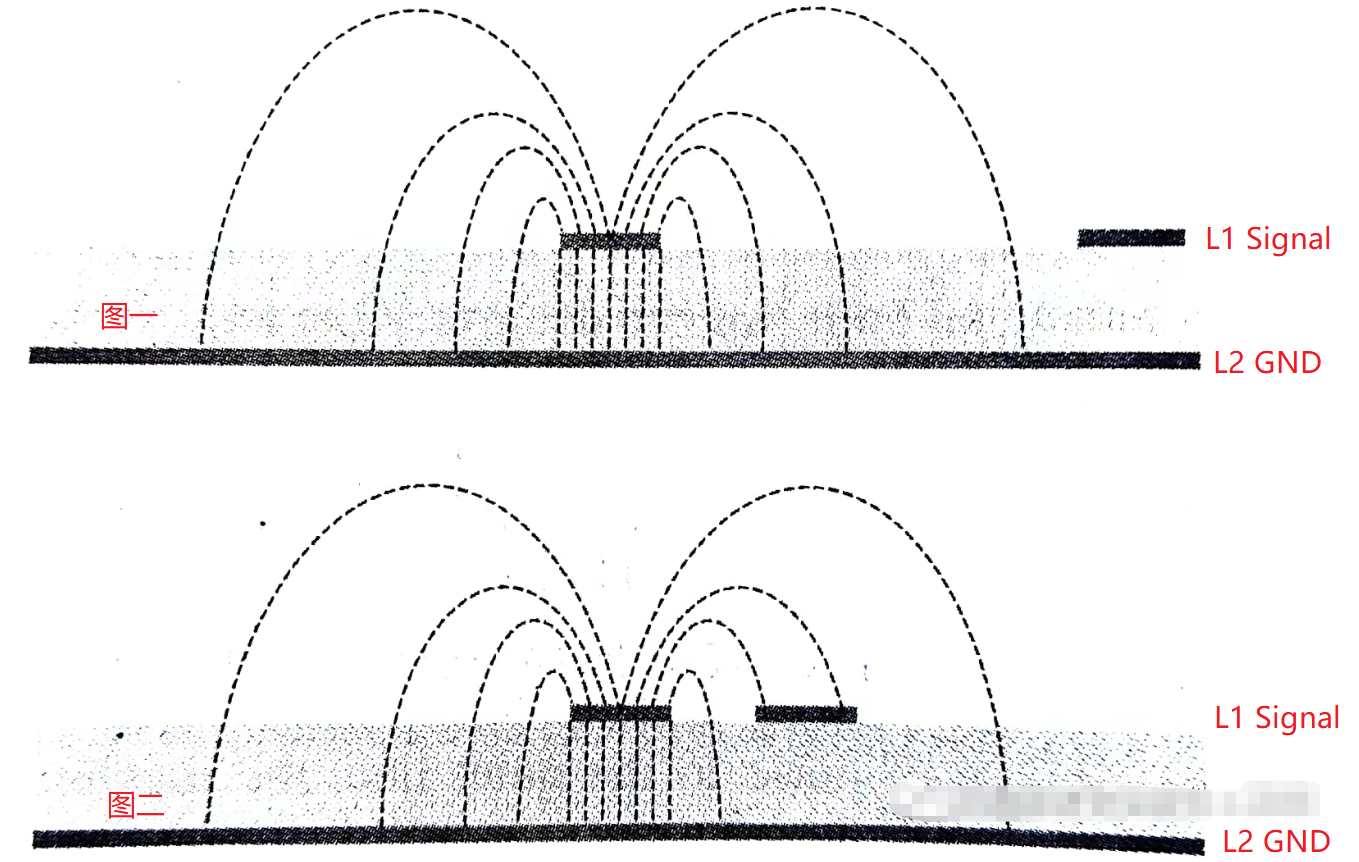

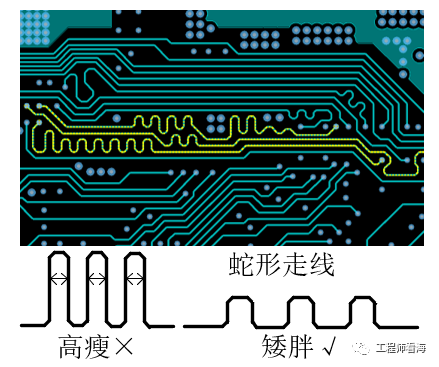

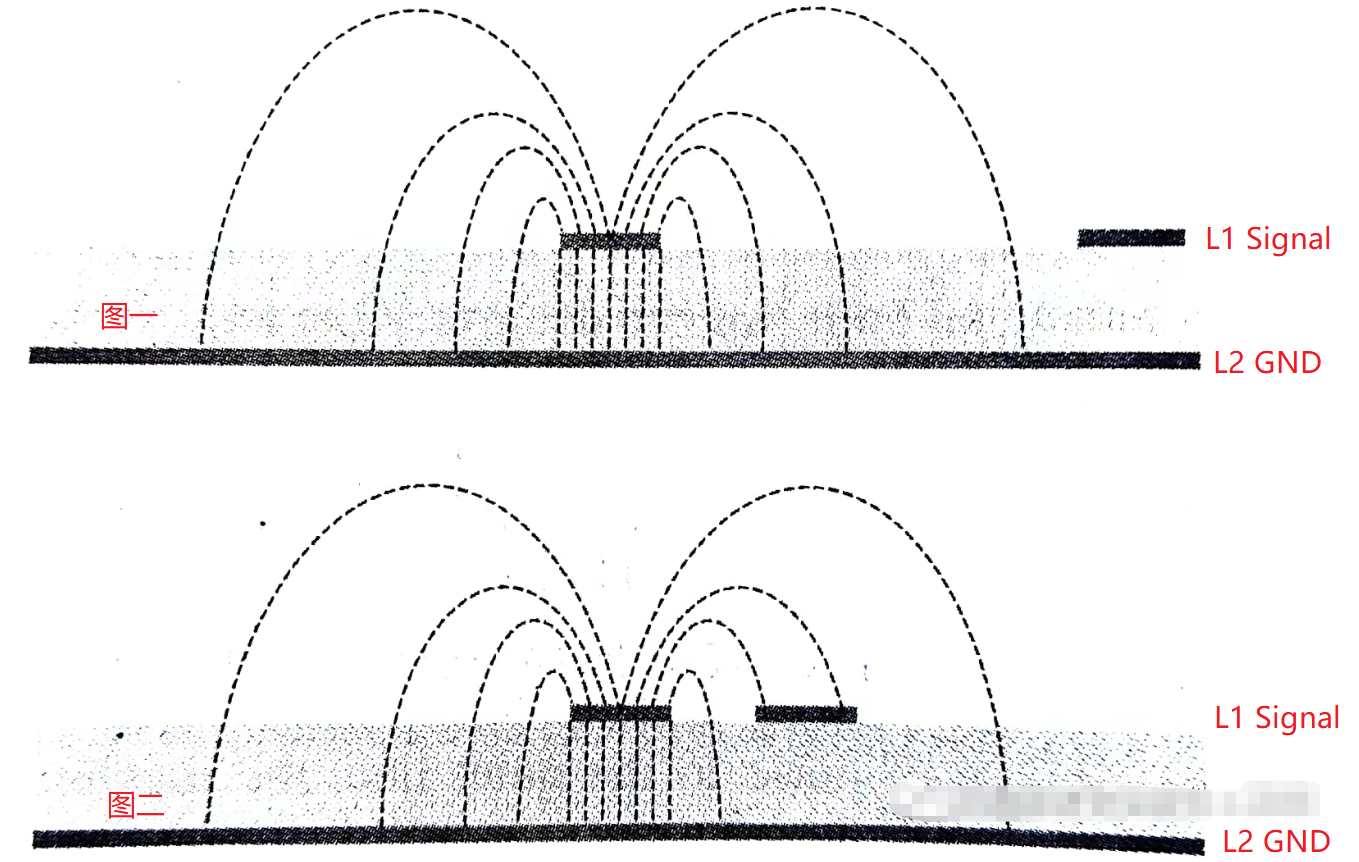

我們經常聽說PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾,這就是3W原則,信號線之間的干擾被稱為串擾,串擾是怎么形成的呢?

2023-04-18 11:06:22 2146

2146

信號完整性分析是一個很復雜的系統工程,它是各種影響信號質量和時序的問題的疊加組合。且隨著信號速率的提高,信號完整性問題變得越來越復雜,需要考慮的因素越來越多。

2023-06-15 15:07:59 2755

2755

串擾是四類信號完整性問題之一,指的是有害信號從一個線網傳遞到相鄰線網。任何一對線網之間都存在串擾。

2023-09-25 11:29:07 3292

3292

信號完整性(Signal Integrity,SI)是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。

2023-09-28 11:27:47 4070

4070

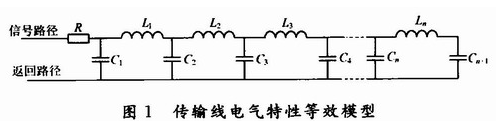

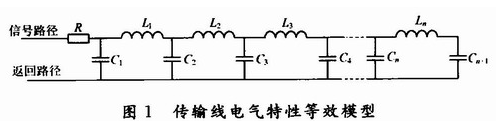

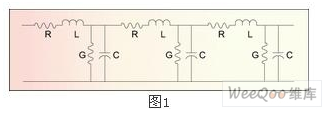

、仿真軟件優劣等概況;概述后面諸講的各種基本概念。同時,簡要介紹相關技術資料、國內外最新科研成果、國內出版的原版譯著情況等。第二講 信號/互連線帶寬與時頻域阻抗 介紹信號完整性的研究對象——上升邊

2010-12-16 10:03:11

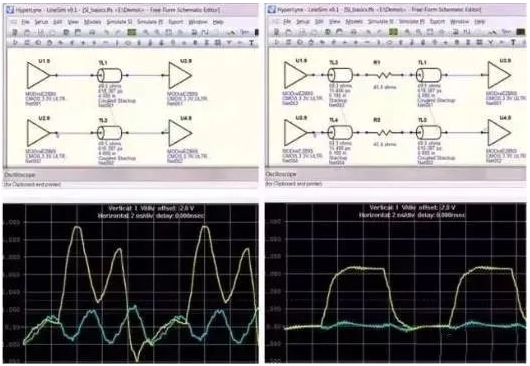

的高性能的信號完整性分析工具,它可以準確地分析復雜的PCB、MCM及多PCB板構成的系統的信號質量和傳輸線時延。XTK是一個串擾分析工具包,其中包含多種分析工具。 6 LineSim與BoardSim

2013-12-05 17:44:44

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

阻抗,因此,需要將端接和拓撲的長度變化相結合來控制反射,使得它們不會對信號質量和時序產生不利影響。圖2:使用信號完整性分析和設計空間探索消除信號質量和串擾問題。可以運行這些相同的仿真,以確定信號經過

2019-06-17 10:23:53

Hyperlynx和ADS的功能1.2用Hyperlynx進行信號完整性原理仿真1.3用Hyperlynx進行信號完整性仿真1.4用ADS進行信號完整性仿真五. 傳輸線的串擾; 六. 差分對

2009-11-25 10:13:20

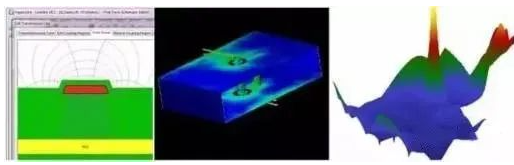

原本放在頂層的走線信號傳輸或串擾性能。 對于電源完整性來說,增加電源與地之間的容性耦合可以濾除電源中的交流波動。在實際應用中,往往采取加解耦電容的方法。電流密度的動態顯示可以幫助設計者直觀了解到電源網

2015-01-07 11:33:53

信號完整性與電源完整性的仿真分析與設計,不看肯定后悔

2021-05-12 06:40:35

的1在接收器中看起來就像 1(對0同樣如此)。在電源完整性中,重點是確保為驅動器和接收器提供足夠的電流以發送和接收1和0。因此,電源完整性可能會被認為是信號完整性的一個組成部分。實際上,它們都是關于數字電...

2021-11-15 07:37:08

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

://pan.baidu.com/s/1jG0JbjK信號完整性小結1、信號完整性問題關心的是用什么樣的物理互連線才能確保芯片輸出信號的原始質量。2、信號完整性問題一般分為四種:單一網絡的信號質量、相鄰網絡間的串

2015-12-12 10:30:56

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

最新的高速電路設計與信號完整性分析技術要點;深入講解信號完整性的四類問題:反射(reflection);串擾(crosstalk);電源軌道塌陷(railcollapse);電磁干擾(EMI)。介紹

2010-05-29 13:29:11

反射和串擾的分析結果。Altium Designer的信號完整性分析采用IC器件的IBIS模型,通過對版圖內信號線路的阻抗計算,得到信號響應和失真等仿真數據來檢查設計信號的可靠性。Altium

2015-12-28 22:25:04

確定該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現了信號完整性問題。 高速PCB的信號完整性問題主要包括信號反射、串擾、信號延遲和時序錯誤。 · 反射:信號在傳輸線上傳輸時,當高速

2018-11-27 15:22:34

、課程提綱:課程大綱依據學員建議開課時會有所調整。一. 信號完整性分析概論:1.1信號完整性的含義1.2單一網絡的信號質量1.3串擾1.4軌道塌陷1.5電磁干擾1.6信號完整性的兩個重要推論1.7電子產品

2009-11-18 17:28:42

電路設計與信號完整性分析,EDA技術及軟件研發。目錄第1章信號完整性分析概論 1.1信號完整性的含義 1.2單一網絡的信號質量 1.3串擾 1.4軌道塌陷噪聲 1.5電磁干擾 1.6信號完整性的兩個

2017-08-08 18:03:31

的含義 1.2單一網絡的信號質量 1.3串擾 1.4軌道塌陷噪聲 1.5電磁干擾 1.6信號完整性的兩個重要推論 1.7電子產品的趨勢 1.8新設計方法學的必要性 1.9一種新的產品設計

2017-09-19 18:21:05

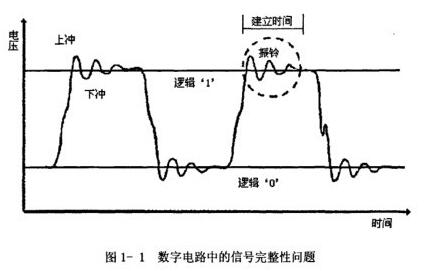

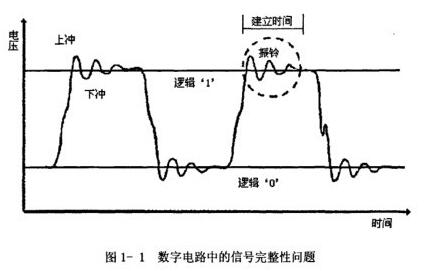

(Overs hoot)是指信號跳變的第一個峰值(或谷值),它是在電源電平之上或參考地電平之下的額外電壓效應;2、 串擾:在PCB中,串擾是指當信號在傳輸線上傳播時,因電磁能量通過互容和互感耦合

2019-09-25 07:30:00

`先來熟悉幾個概念:信號完整性是指信號在信號線上的質量。信號具有良好的信號完整性是指當在需要的時候,具有所必需達到的電壓電平數值。差的信號完整性不是由某一因素導致的,而是由板級設計中多種因素共同

2019-11-19 18:55:31

噪聲3.電磁干擾(EMI)常見的信號完整性的噪聲問題,有振鈴,反射,近端串擾,開關噪聲,非單調性,地彈,電源反彈,衰減,容性負載。以上所有的噪聲問題都與下面的4個噪聲源有關:1:單一網絡的信號完整性

2017-11-22 17:36:01

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

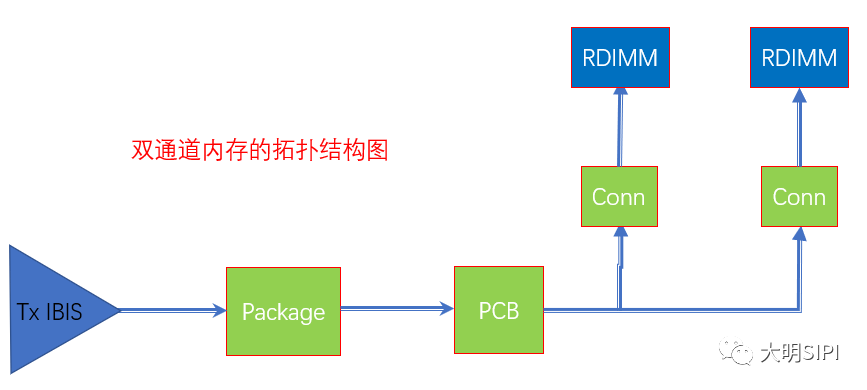

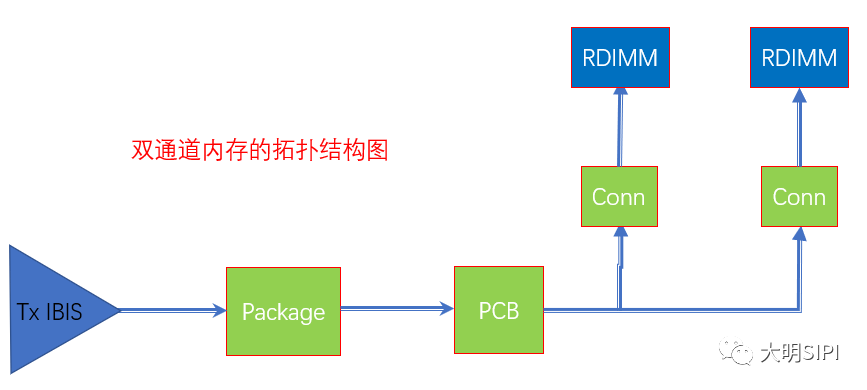

中,采用Cadence軟件的高速仿真工具SPECCTRAQuest,并利用器件的 IBIS模型來分析信號完整性,對阻抗匹配以及拓撲結構進行優化設計,以保證系統正常工作。本文只對信號反射和串擾進行詳細

2015-01-07 11:30:40

摘 要:從信號完整性分析設計規則、完整性分析仿真器、波形分析器等三個方面說明了如何利用Protel 99的信號完整性分析功能進行印刷電路板的設計。 關鍵詞:信號完整性;電磁干擾;波形

2018-08-27 16:13:55

信號完整性是指信號在信號線上的質量,即信號在電路中以正確的時序和電壓作出響應的能力。如果電路中信號能夠以要求的時序、持續時間和電壓幅度到達接收器,則可確定該電路具有較好的信號完整性。反之,當信號不能

2018-07-31 17:12:43

。舉一個最簡單的例子,反射如果處理不好,串擾噪聲也會大幅度惡化。這樣的相互糾纏現象在信號完整性中很多,有時候看起來影響很小的一個因素在其他因素糾纏推動下成了大問題。如果沒有全面系統的去掌控,僅僅優化

2017-06-23 11:52:11

?允許的時滯和噪聲裕量是多少?作為信號完整性設計的通用準則,轉換速度越慢,信號完整性越好。50MHZ時鐘采用500PS上升時間是沒有理由的。一個2-3NS的擺率控制器件速度要足夠快,才能保證SI的品質

2015-01-07 11:44:45

完整性中,重點是確保為驅動器和接收器提供足夠的電流以發送和接收1和0。因此,電源完整性可能會被認為是信號完整性的一個組成部分。實際上,它們都是關于數字電路正確模擬...

2021-11-15 06:31:24

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

最新的高速電路設計與信號完整性分析技術要點;深入講解信號完整性的四類問題:反射(reflection);串擾(crosstalk);電源軌道塌陷(rail collapse);電磁干擾(EMI)。介紹的分析

2010-11-09 14:21:09

高速數字設計領域里,信號完整性已經成了一個關鍵的問題,給設計工程師帶來越來越嚴峻的考驗。信號完整性問題主要為反射、串擾、延遲、振鈴和同步開關噪聲等。本文基于高速電路設計的信號完整性基本理論,通過近端

2010-05-13 09:10:07

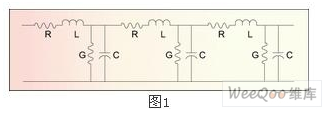

高速電路信號完整性分析與設計—串擾串擾是由電磁耦合引起的,布線距離過近,導致彼此的電磁場相互影響串擾只發生在電磁場變換的情況下(信號的上升沿與下降沿)[此貼子已經被作者于2009-9-12 10:32:03編輯過]

2009-09-12 10:31:08

高速電路信號完整性分析與設計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

摘要! 介紹了高速+,& 設計中的信號完整性概念以及破壞信號完整性的原因!從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因!并介紹了-&-. 仿真"關鍵詞!

2008-10-15 08:15:02 0

0 高速電路信號完整性分析與設計—串擾串擾是由電磁耦合引起的,布線距離過近,導致彼此的電磁場相互影響串擾只發生在電磁場變換的情況下(信號的上升沿與下降沿)

2009-10-06 11:10:15 0

0 高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 高速數字電路信號完整性分析與設計:信號完整性概述 傳輸線理論 PCB阻抗控制 拓撲與端接技術 時序計算 串擾與對策

2009-10-06 11:25:17 0

0 信號完整性原理分析

什么是“信號完整性”?在傳統的定義中“完整性(integrity)”指完整和末受損的意思。因此,具有良好完整性的數字信號應是干凈,

2009-11-04 12:07:06 212

212 信號完整性基礎根據定義, “完整性”是指“完整和無損害的”。 同樣,一個具有良好的完整性的數字信號有干凈、快速的上升沿;穩定和有效的邏輯電平;準確的時間位置和

2010-08-05 15:11:33 242

242 什么是信號完整性

信號完整性(Signal Integrity):就是指電路系統中信號的

2009-06-30 10:23:18 5717

5717

文章介紹了數字電路設計中的信號完整性問題, 探討了振鈴、邊沿畸變、反射、地彈、串擾和抖動等各種信號完整性問題的成因和抑制措施。針對常見的反射和串擾給出了較為詳細的分

2011-09-07 16:14:58 104

104 為了使設計人員對信號完整性與電源完整性有個全面的了解,文中對信號完整性與電源完整性的問題進行了仿真分析與設計,也從系統的角度對其進行了探討。

2011-11-30 11:12:24 0

0 本專題詳細介紹了信號完整性各部分知識,包括信號完整性的基礎概述,信號完整性設計分析及仿真知識,還有具體應用中的一些小經驗分享等等,充分翔實的向大家描述了信號完整性。

2011-11-30 11:44:35

本書全面論述了信號完整性問題。主要講述了信號完整性和物理設計概論,帶寬、電感和特性阻抗的實質含義,電阻、電容、電感和阻抗的相關分析,解決信號完整性問題的四個實用技術手段,物理互連設計對信號完整性

2015-11-10 17:36:24 0

0 信號完整性是指信號在通過一定距離的傳輸路徑后在特定接收端口相對指定發

送端口信號的還原程度。在討論信號完整性設計性能時,如指定不同的收發參考端

口,則對信號還原程度會用不同的指標來描述。

2016-02-19 16:41:51 0

0 介紹信號完整性的四個方面,EMI,串擾,反射,電源等。

2016-08-29 15:02:03 0

0 10129@52RD_信號完整性與電源完整性的仿真分析與設計

2016-12-14 21:27:39 0

0 所謂“萬丈高樓平地起”,說的就是這個道理,想從事信號完整性工作就必須對整個信號完整性的理論基礎有一個很明晰的了解。至少要熟讀幾本信號完整性方面的書籍,了解什么是信號完整性;了解信號完整性研究的對象和內容是什么;信號完整性與哪些因素有關系;信號完整性會影響到產品的哪一個方面;等等。

2017-08-29 15:47:22 21315

21315 信號完整性是指信號在傳輸路徑上的質量,由于路徑的特性對信號造成的失真。數字電路剛出現的時候,由于傳輸信號速率很低,在電路分析時采用低頻和直流的方法就可以。

2017-11-03 15:52:36 88456

88456

信號完整性(Signal Integrity Signal Integrity,簡稱SI SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一 因素導致的,而是板級設計中多種因素共同

2017-11-16 13:24:51 0

0 本文通過介紹信號完整性理論,對串擾和反射的成因進行探討。利用Cadence公司的軟件SpecctraQuest,以基于ARM11架構的S3C6410為主處理器嵌入式系統為載體進行信號完整性仿真分析

2017-12-01 17:16:01 1651

1651

高速 PCB 信號完整性仿真分析.pdf

2018-05-07 14:52:31 52

52 信號完整性是指信號在信號線上的質量,即信號在電路中能以正確的時序和電壓電平作出響應的能力,信號具有良好的信號完整性是指在需要的時候具有所必需達到的電壓電平數值。差的信號完整性不是由某一單一因素導致

2019-06-28 15:24:17 2830

2830

信號完整性的問題主要包括傳輸線效應,如反射、時延、振鈴、信號的過程與下沖以及信號之間的串擾等,涉及傳輸線上的信號質量及信號定時的準確性。

良好的信號質量是確保穩定時序的關鍵。由于反射和串擾造成

2019-06-24 15:27:25 1803

1803

信號完整性(S i gnal Integri ty,SI)是指信號在信號線上傳輸的質量。對于數字電路,就是要信號在電路中能以正確的時序和電壓做出響應。如果電路中信號能夠以要求的時序、持續時間和電壓

2019-05-27 13:58:16 2399

2399

借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。

2019-05-20 15:25:37 1542

1542

技術分享:信號完整性仿真 - 入門

2019-07-02 12:03:07 4676

4676

隨著 IC 芯片時鐘信號頻率的增加、信號邊沿的減小,由此帶來的信號完整性問題已經越來越凸顯。PCB 信號完整性問題主要包括由阻抗不匹配引起的信號過沖、相鄰不同網絡之間由于各種耦合產生的信號串擾、有損

2019-11-04 08:00:00 0

0 信號完整性是指信號在信號線上傳輸的質量,主要問題包括反射、振蕩、時序、地彈和串擾等。信號完整性差不是由某個單一因素導致,而是板級設計中多種因素共同引起。在千兆位設備的PCB板設計中,一個好的信號完整性設計要求工程師全面考慮器件、傳輸線互聯方案、電源分配以及EMC方面的問題。

2020-04-15 15:59:49 1149

1149

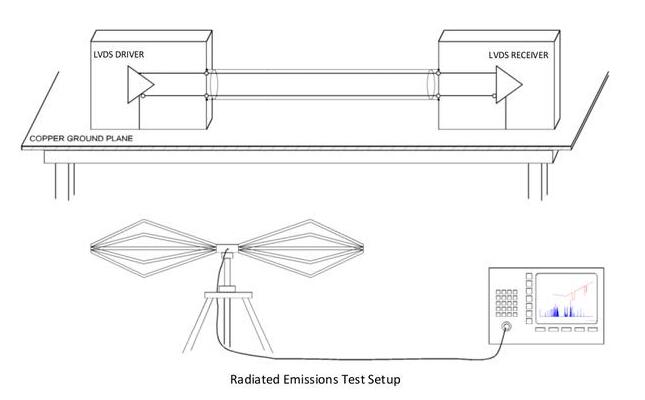

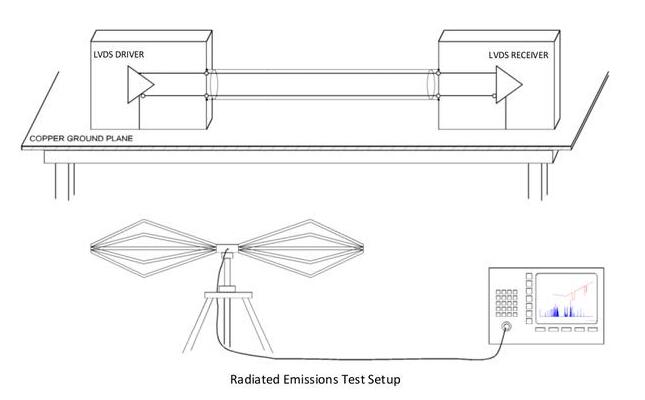

隨著電路速度的增加,信號完整性在電子設計中變得更加重要。更快的數據速率和更短的上升/下降時間使信號完整性更具挑戰性。信號的失真和降級會對電磁兼容性產生不利影響。隨著信號完整性降低,電路輻射和電路抗擾性都可能會增加。

2020-07-09 15:29:48 4237

4237

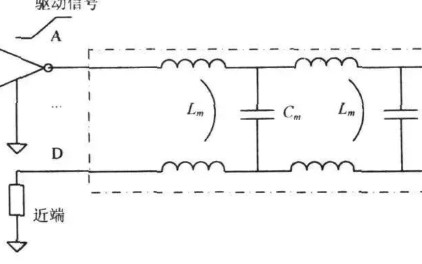

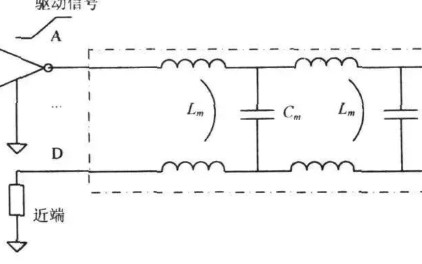

本文主要介紹串擾的概念,及其FEXT、NEXT等,以及串擾的消除措施。 串擾串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲干擾。這種干擾是由于兩條信號線間的耦合,即

2020-10-19 17:54:49 8359

8359

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

信號完整性是指高速產品設計中由互連線引起的所有問題。包括以下幾部分:

時序

噪聲

電磁干擾(EMI

2021-01-26 09:28:30 12

12 電子發燒友網為你提供信號完整性工程師參考:重讀串擾的基本原理資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:53:14 2

2 Hyperlynx信號完整性仿真性分析。

2021-04-07 13:59:10 144

144 信號完整性與電源完整性的仿真(5V40A開關電源技術參數)-信號完整性與電源完整性的仿真分析與設計!!!

2021-09-29 12:11:21 91

91 完整性中,重點是確保為驅動器和接收器提供足夠的電流以發送和接收1和0。因此,電源完整性可能會被認為是信號完整性的一個組成部分。實際上,它們都是關于數字電路正確模擬...

2021-11-08 12:20:59 64

64 介紹了高速PCB設計中的信號完整性概念以及破壞信號完整性的原因,從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因,并介紹了IBIS仿真。

2021-12-17 13:47:07 1

1 何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2022-01-07 15:38:32 0

0 高速電路信號完整性分析與設計—時序計算

2022-02-10 17:16:41 0

0 高速電路信號完整性分析與設計—串擾

2022-02-10 17:23:04 0

0 高速電路信號完整性分析與設計—信號完整性仿真

2022-02-10 17:29:52 0

0 本文首先介紹了傳輸線理論,詳細分析了高速PCB設計中的信號完整性問題,包括反射、串擾、同步開關噪聲等,然后利用Mentor Graphics公司的EDA軟件HyperLynx對給定電路模型進行了反射

2022-07-01 10:53:00 0

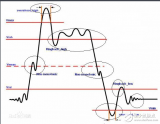

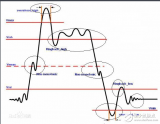

0 我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,看下面這張圖,你就會知道理想的信號,經過:反射、串擾、抖動,最后變成什么鬼。

2022-08-24 11:22:17 986

986 信號完整性 搞硬件還需要懂這些? 工程師成長計劃第十期,認識信號完整性。 ? 信號完整性(Signal Integrity,SI),通俗來講就是信號的質量。包含兩個方面:信號的傳輸與電源的供應

2022-11-03 12:55:15 2013

2013 定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2022-11-16 14:56:00 6200

6200 本章我們接著介紹信號完整性基礎第三章節串擾剩余知識。

2023-01-16 09:58:36 3159

3159 信號完整性分析的目的就是用最小的成本,最快的時間使產品達到波形完 整性、時序完整性、電源完整性的要求。

2023-02-03 11:25:55 2366

2366 串擾是指有害信號從一個網絡轉移到相鄰網絡。任何一對網絡之間都存在串擾。通常把噪聲源所在網絡稱為動態網絡或攻擊網絡。把受影響的網絡稱為靜態網絡或者受害網絡。

2023-05-06 11:48:08 3293

3293

串擾 :即兩條信號線之間的耦合引起的線上噪聲干擾。

2023-07-06 09:15:48 2670

2670

小的成本,快的時間使產品達到波形完整性、時序完整性、電源完整性的要求;我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,

2023-08-17 09:29:30 8719

8719

現一系列問題,如串擾、反射波、時鐘抖動等。為了確保高速信號傳輸的穩定和可靠性,需要進行仿真串擾。本文將詳細介紹高速信號仿真的串擾以及為什么需要進行仿真。 對于高速信號來說,串擾是一種令人頭疼的問題。串擾是指高速信

2023-09-05 15:42:31 1458

1458 pcb信號完整性詳解 隨著電子領域技術日新月異的發展,高速電路已經成為了電路設計的重要領域之一。在高速電路中,信號完整性顯得尤為重要。在設計PCB電路時,信號完整性是一個必須考慮的因素。那么

2023-09-08 11:46:58 2269

2269 對電路的性能和可靠性具有深遠的影響,因此,需要采取各種措施來維護信號的完整性。 電阻是一種普遍的電子元件,常用于電路的調整、分壓、弱化、匹配等功能。電路端接電阻能改善信號完整性的原理在于其具有以下三個重要的

2023-10-24 10:04:52 1854

1854 PCB級的信號完整性仿真

2022-12-30 09:20:36 15

15 串擾和反射影響信號的完整性? 串擾和反射是影響信號傳輸完整性的兩個主要因素。在深入討論之前,首先需要了解信號傳輸的基本原理。 在通信系統中,信號通常被傳輸通過各種類型的傳輸媒介,例如電纜、光纖或

2023-11-30 15:21:55 1146

1146 在現代電子通信和數據處理系統中,信號完整性(Signal Integrity, SI)是一個至關重要的概念。它涉及信號在傳輸過程中的質量保持,對于確保系統性能和穩定性具有決定性的影響。本文將從信號完整性的定義、影響因素、測試方法、以及在實際應用中的重要性等方面,對信號完整性進行詳細的探討。

2024-05-28 14:30:58 2970

2970 電子發燒友網站提供《信號完整性與電源完整性-信號的串擾.pdf》資料免費下載

2024-08-12 14:27:05 2

2 (EMI)和射頻干擾(RFI)。 一、信號完整性的基本概念 信號完整性涉及到信號在電路中的傳輸質量,包括信號的幅度、形狀和時序。理想的信號傳輸應該是無失真的,但在實際應用中,由于多種因素的影響,信號可能會發生退化。這些

2024-11-29 15:17:11 1781

1781 2024年12月20日14:00-16:00中星聯華科技將舉辦“高速信號完整性分析與測試”-“碼”上行動系列線上講堂線上講堂。本期會議我們將為大家介紹高速串行總線傳輸基本框架,什么是信號完整性?高速

2024-12-15 23:33:31 1135

1135

,設計人員必須注意電路板布局并使用適當的導線和連接器,從而最大限度地減少反射、噪聲和串擾。此外,還必須了解傳輸線、阻抗、回波損耗和共振等基本原理。 本文將介紹討論信號完整性時使用的一些術語,以及設計人員需要考慮的問題,然后介紹 [Amphenol] 優異的電纜和

2025-05-25 11:54:00 1060

1060

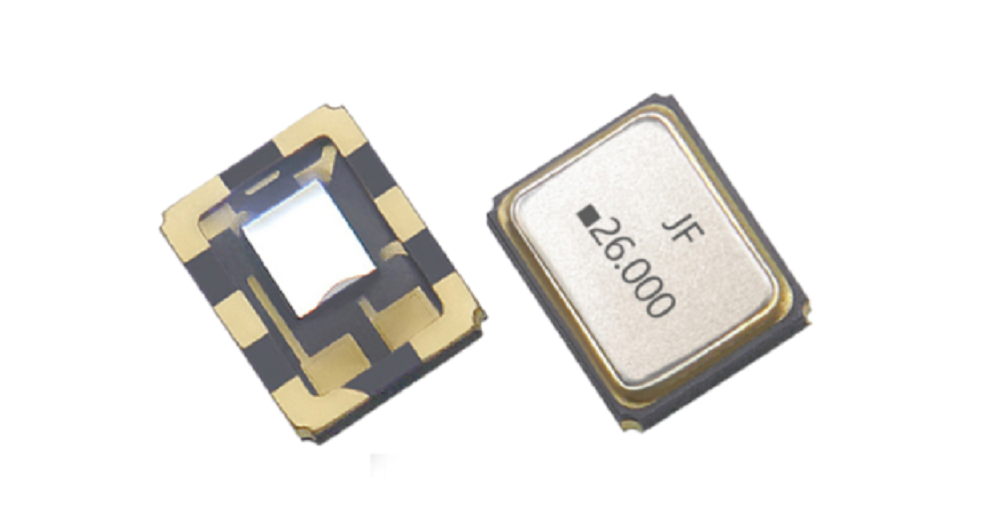

在高速數字電路和射頻系統中,高頻晶振作為關鍵的頻率源,其信號完整性直接影響整個系統的性能。隨著電子技術的飛速發展,晶振的工作頻率不斷提高,電磁干擾(EMI)與串擾問題日益凸顯,成為制約系統可靠性

2025-05-22 15:35:31 782

782

電子發燒友App

電子發燒友App

評論