一般我們在進行PCB設計時可能會留意到有些信號會串聯一個電阻,那么大家是否有想過所串聯的電阻是有什么作用呢?

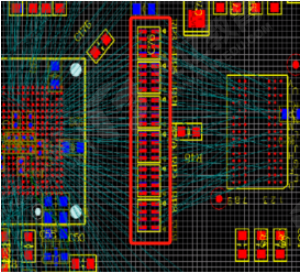

大家可以看一下下面圖示的案例,信號是從CPU處出來再接到DDR顆粒的,每一個DDR數據線都有串聯一個電阻,其實這個串聯電阻的作用是進行阻抗匹配的,防止信號發生反射。

我們接下來用allegro軟件自帶的sigxplorer軟件進行仿真驗證一下,我們主要分析驗證一下這個電阻他是如何進行阻抗匹配以及電阻阻值應該如何選取!

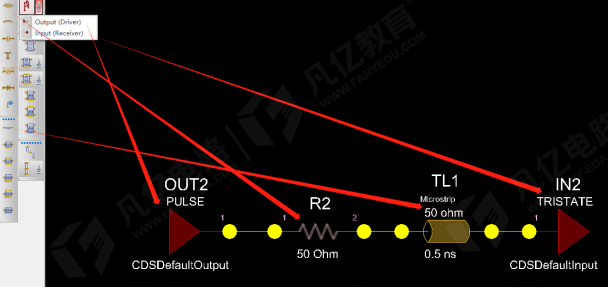

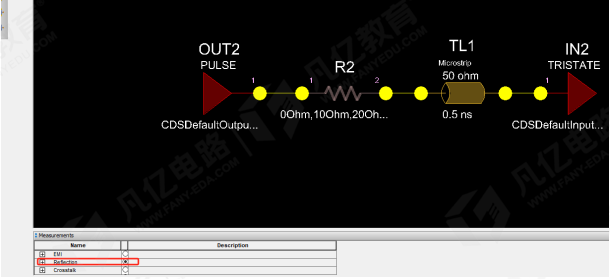

首先我們需要按照下圖先對鏈路進行搭建,并且把傳輸線阻抗改為常規的單端50ohm,

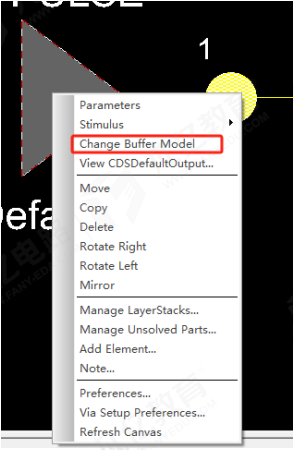

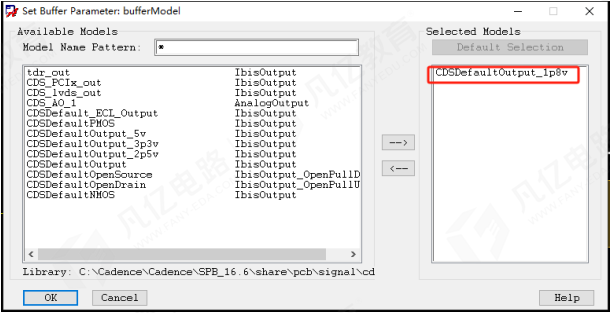

然后再把tx和rx的模型改為1.8v的高速模型

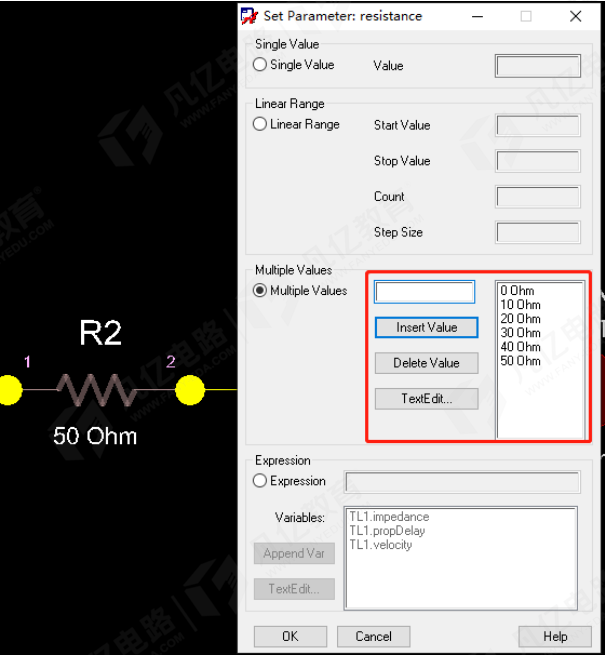

電阻的阻值大小我們分為6種情況進行仿真,如下圖所示,看電阻大小對實際信號反射的改善效果,以及把模式切換成reflection,進行信號反射仿真

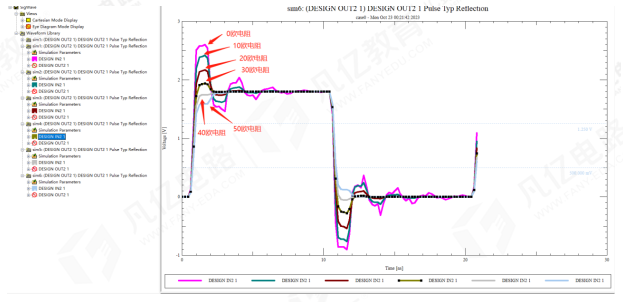

設置好前面的參數之后我們點擊仿真,可以看到我們如下仿真的結果,rx端所接收到的波形,可以看到當我們前面沒有串聯電阻的時候信號會發生嚴重的過沖現象,當我們不斷把電阻加大的時候我們會發現信號的過沖在不斷的減小,但是當電阻為40歐姆和50歐姆的時候,信號的上升沿發生了欠沖的現象(上升沿變緩),當電阻在30歐姆的時候我們會發現信號的質量是最好的!

從上面的仿真結果我們知道電阻的大小會對波形產生不同的影響,而且電阻不是越大越好也不是越小越好,我們只有選擇合適的串聯電阻才能達到改善信號反射的效果。一般我們所選取的電阻大小為22-30歐之間,當然實際要確定這個阻值的具體大小最好是通過仿真驗證決定或者在后期調試階段可以更換電阻的阻值從而達到阻抗匹配的目的。

這其中的原理是因為在tx端有一個內阻(內阻不是一個固定值,他是會變化的),一般是小于50歐姆的,而傳輸線阻抗為50歐姆,兩者阻抗不一致則會導致信號發生反射,我們在信號前面加一個電阻的作用則是為了改善信號的反射,使得信號內阻加上串接電阻的阻值等于或者接近傳輸線的阻抗,從而消除信號的反射。

以DDR為例,現在的DDR基本上都不會有串接電阻了,當然并不是說不需要這個電阻,是因為現在的DDR有了ODT技術,相當于把電阻集成到芯片內部了(而且電阻可調),所以我們外部的數據線是不需要添加串聯的端接電阻了,但是需要注意的是,ODT技術是針對數據線來說的,不包含地址線,控制線,時鐘線,所以地址線,控制線,時鐘線如果不做處理的化也會有信號發生反射,除了串聯端接外我們還有并聯端接可以降低信號的反射,不同的端接方式有不同的應用場景以及有不同效果,這個電阻我們需要盡量靠近tx端進行放置才有效果,如果放置的過遠則不會起到改善信號反射的效果,我們下次也可以驗證一下電阻如果放置的過遠信號的波形會產生什么變化。

聲明: 本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207-

pcb

+關注

關注

4405文章

23878瀏覽量

424327

原文標題:信號上的串聯電阻是如何改善信號質量的

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TUSB211A USB 2.0 高速信號調節器:提升信號質量的利器

信維高頻MLCC電容,助力高速信號傳輸

信維高頻陶瓷電阻,助力高速信號穩定傳輸

時鐘信號對數字音頻質量的影響

串聯諧振的原理及基本性能

如何使用數據異常判斷電能質量在線監測裝置采樣電阻是否損壞?

揭秘高頻PCB設計:體積表面電阻率測試儀如何確保信號完整性

高扇出信號線優化技巧(上)

如何實現DAB高質量信號采集

信號上的串聯電阻是如何改善信號質量的

信號上的串聯電阻是如何改善信號質量的

評論