很多人可能覺得PCB信號速率越高,如25Gbps,56G/112G-PAM4信號等調試上發現的問題會越多,其實不然。我們收到最多的調試問題還是DDR3、DDR4等,不是跑不到額度速率,就是識別不到

2026-01-05 15:46:16

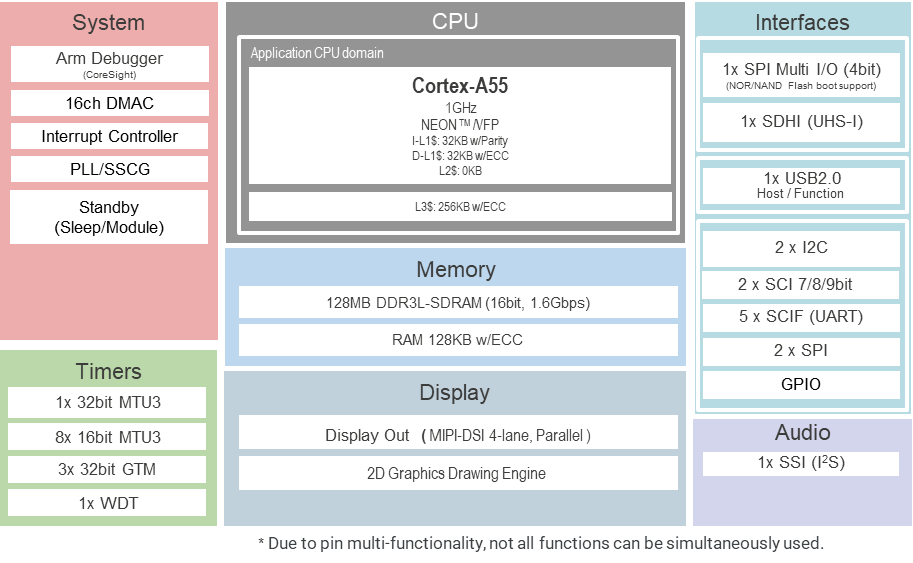

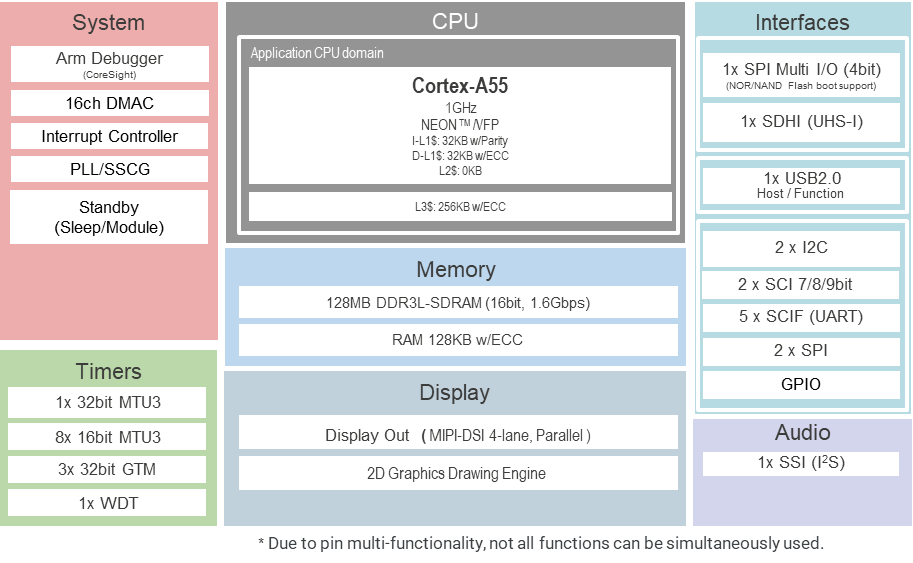

RZ/A3MHMIMPU對于高質量圖形顯示的應用要求,用戶通常采用功能強大及搭載DDR高速接口的MPU來實現更多功能和更流暢的畫面。但在開發過程會遇到DDR高速總線設計的難題,同時Linux系統

2025-12-24 12:06:10 300

300

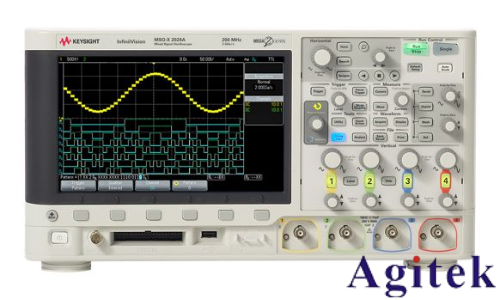

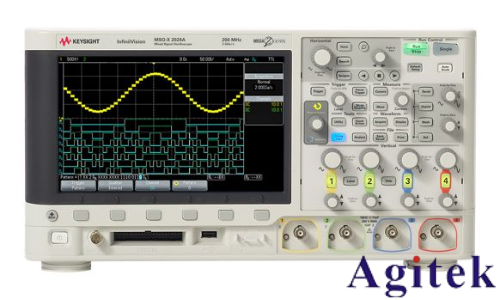

在現代高速數字通信系統中,眼圖分析是評估信號完整性和傳輸質量的核心工具。泰克示波器憑借其高精度和豐富的分析功能,成為工程師進行眼圖測試的首選設備。本文將詳細介紹使用泰克示波器進行眼圖分析的完整流程,涵蓋基礎操作步驟、關鍵參數設置及高級分析技巧,幫助用戶高效獲取信號質量評估結果。

2025-12-10 17:26:53 938

938

Nikon SLM Solutions使用CADENAS解決方案遷移了8600多個零部件并優化了設計工程流程

Nikon SLM Solutions公司依靠3Dfindit企業版實現了高效、高質量

2025-11-25 10:06:10

本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3467

3467

DDR?作為?RK?平臺數據傳輸的?“主動脈”,其穩定性與性能直接決定產品體驗。尤其在內存顆粒迭代快、多場景應用普及的當下,一套通用且精準的?DDR?測試方法,能有效規避兼容性問題、提前發現隱性故障

2025-11-19 07:08:56 291

291

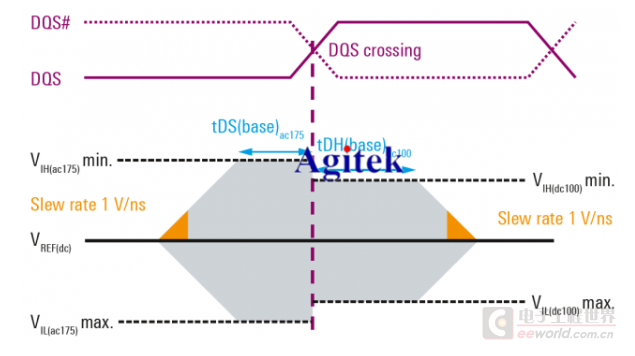

失真,影響數據的正確傳輸。DDR training通過自適應的機制來補償這些信號完整性問題,確保數據鏈路的可靠性。

2025-11-17 10:25:33 3397

3397

下面是HummingBird EV Kit給的版圖,其中DDR3_D0對應的應該是板子上的FPGA的C2引腳:?

不過我在配置MIG的時候,通過讀入ucf文件的方式配置DDR3 SDRAM的引腳

2025-11-06 07:57:09

電子發燒友網站提供《DDR3 SDRAM參考設計手冊.pdf》資料免費下載

2025-11-05 17:04:01 4

4 )

MM2S_LENGTH0x0028DMA寫數據長度(字節為單位)

具體連接圖如下,由于本次使用的總線為50MHz,DMA時鐘為50M;DDR3 ui_clk為100MHz;e203這里使用了10MHz。時鐘的轉換完全

2025-10-29 08:21:10

,如果用ARM處理器或上位機來實現這個過程會十分耗時,利用FPGA的并行處理技術可以輕易實現這個功能,整理后的數據傳輸形式會為之后的設計產生便利。模塊用了20塊片內雙口RAM來實現數據的緩存,同時完成數據

2025-10-29 08:09:01

10MHz,并通過AXI-Inerconnect進行跨時鐘處理,具體連接如下

其中ui_clk連接到M01_ACLK端口,clk_16M連接到S00_ACLK。測試程序如下,

本程序向MIG寫入100個數據,再將其讀出,如果寫入與讀出一致,則打印正確標識。經過測試,DDR3工作正常。

2025-10-29 07:16:34

文件夾內,打開文件夾。閱讀readme說明文檔,我們能夠知道,原作者采用了vivado MIG IP來控制開發板上的DDR3,由于芯來科技的E203平臺系統片內總線是icb總線,所以我們需要做跨時鐘域

2025-10-28 07:25:32

DDR使用

在我們的項目中,我們使用的是芯來科技的DDR200T開發板,我們通過調用板上的DDR3 IP核完成如下表的配置,配置完成后例化該DDR3,然后利用DMA和VDMA作為數據的緩沖模塊,將

2025-10-28 07:24:01

Tektronix提供針對PCIe 6.0 CEM測試的 比特誤碼率測試儀 (BERT) 接收端 (RX) 受限眼圖自動校準。該軟件名為TekRXTest,并支持額外的功能,例如RX表征與裕量測試

2025-10-24 16:16:54 3828

3828

數據的從icb協議轉到axi協議。axi_interconnect實現了數據的跨時鐘域和位寬轉換,并將轉換后的數據傳給mig模塊進而實現對DDR3的控制。

簡單閱讀蜂鳥的代碼發現,蜂鳥本身提供了外部

2025-10-24 08:12:53

的S00_AXI_ACLK、M00_AXI_ACLK,分別接系統頂層時鐘hfextclk、mig產生的用戶時鐘ui_clk,以此來實現跨時鐘域。

(2)例化DDR3模型(仿真的時候需要用,vivado

2025-10-24 07:25:00

環境:Vivado2021.1、NucleiStudio_IDE_202102-win64

內容:簡單講解下利用vivado來調用控制模塊,以實現ov7725攝像頭的視頻數據流傳輸。

首先設計頂層

2025-10-24 06:53:17

] correct : %drn”,i,rd_data);

ddr_offset += 0x00000004;

}

(2)測試效果,讀數正確

vivado綜合:

注意:(1)綜合不需要例化ddr3模型,將

2025-10-23 06:16:44

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現SRAM讀寫測試,包括設計SRAM接口模塊

2025-10-22 17:21:38 4118

4118

DDR控制協議

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源

2025-10-21 14:30:16

IP DDR3控制器 RISC-V

基于DDR200T開發板原理圖,找到所需要使用的DDR引腳,制成DDR.ucf文件方便在添加管腳約束時使用。在使用MIG IP核時,為了方便使用DDR產生的時鐘

2025-10-21 12:43:40

蜂鳥DDR200T中DDR3的ip配置案列,提供DDR3引腳配置。具體參數可更具項目實際更改。

這里選用的axi接口

在賽靈思的IP配置中沒有MT41K28M6JT-125K內存的信息,因此選用

2025-10-21 11:19:08

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源難以實現大量圖像數據

2025-10-21 10:40:28

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源難以實現大量圖像數據

2025-10-21 08:43:39

回收DDR2,回收DDR3,收購DDR2,收購DDR3 DDR4 DDR5長期現金高價回收DDR,回收三星DDR,回收海力士DDR,回收南亞DDR,回收爾必達DDR,回收美光DDR,回收DDR

2025-10-09 14:15:34

速率6400Mbps時數據信號寫眼圖從仿真結果可以看出,速率提升到6400Mbps時,長stub的L14層走線信號眼圖急劇變差,眼高和眼寬都明顯小于短stub的L5層走線,說明DDR5的數據信號還是要

2025-09-28 11:25:04

電能質量在線監測裝置重啟前的安全防護檢查與日常運行時的檢查,核心差異源于 檢查目標、時機、操作場景的本質不同 : 重啟前檢查是 “ 事前預防性檢查 ”,聚焦 “避免重啟操作引發安全事故(如觸電、設備

2025-09-23 14:38:47 339

339

EasyGo DeskSim是一款配置型的實時仿真軟件,它允許用戶將 Simulink 算法程序快速部署到 EasyGo 實時仿真機上。實時仿真機支持選配不同的 FPGA 芯片和 IO 模塊,能夠處理高速信號,并通過 IO 模塊輸出真實的仿真結果,可滿足用戶在科研、教學或工業測試中的多樣化需求。

2025-09-10 17:48:49 740

740

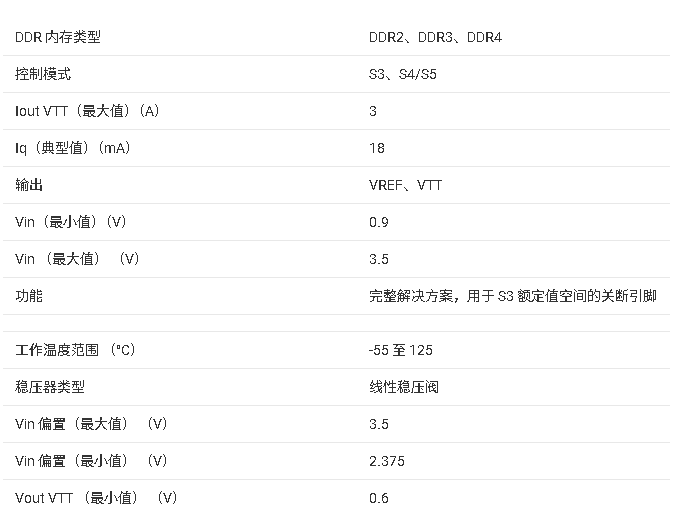

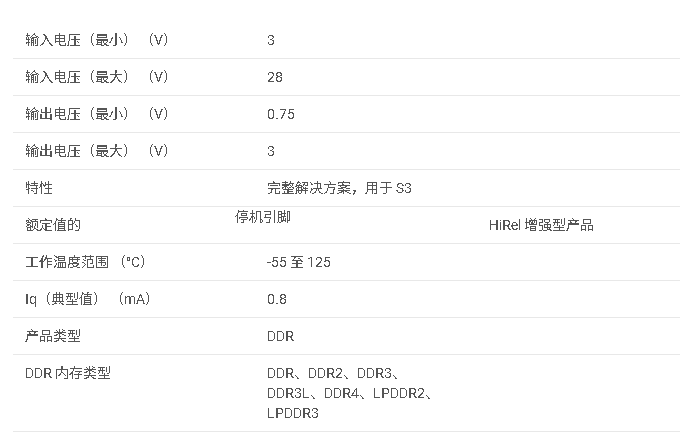

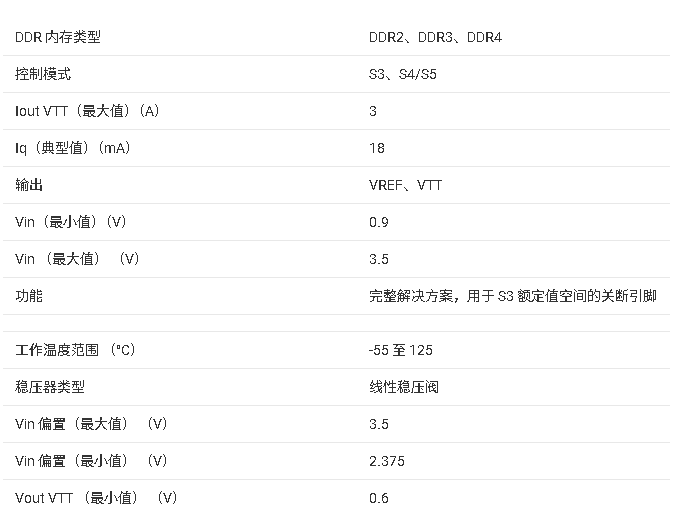

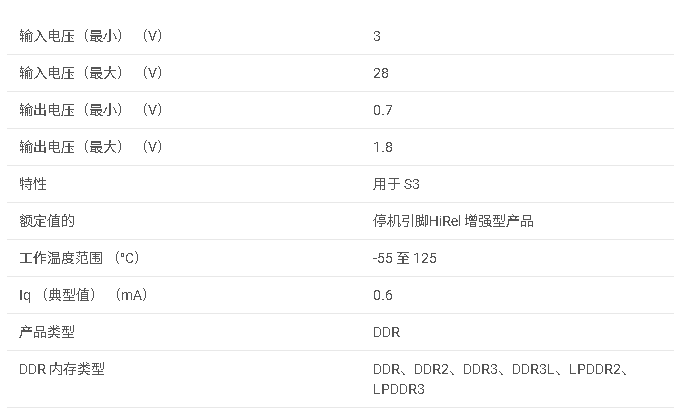

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接應用。TPS7H3301-SP VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源。在

2025-09-09 14:45:15 719

719

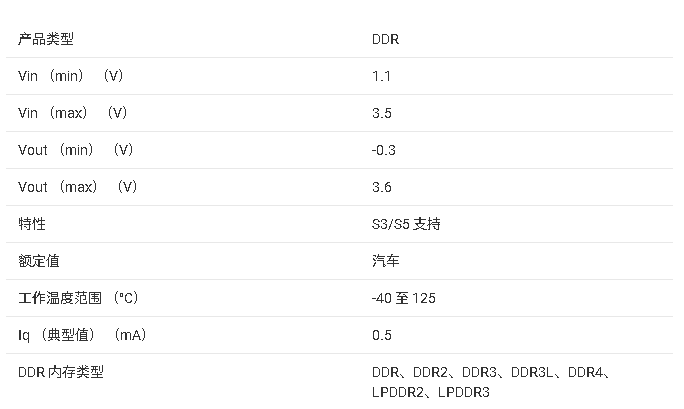

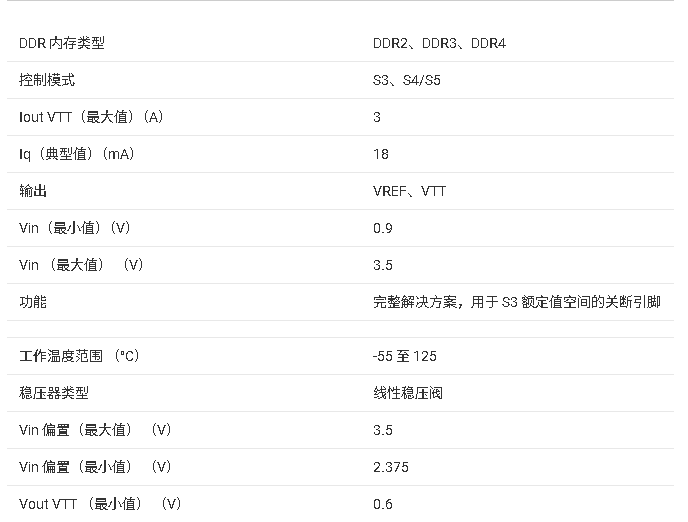

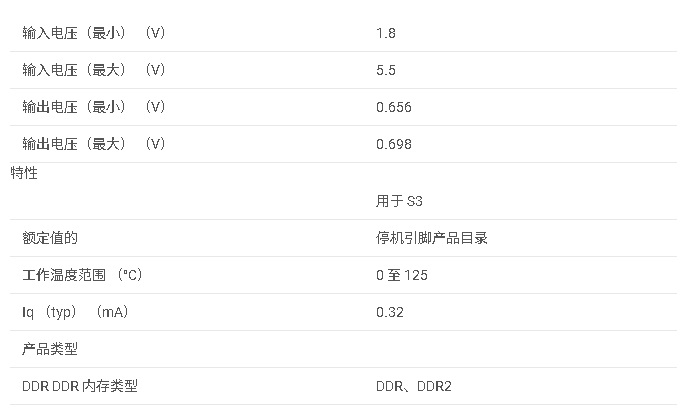

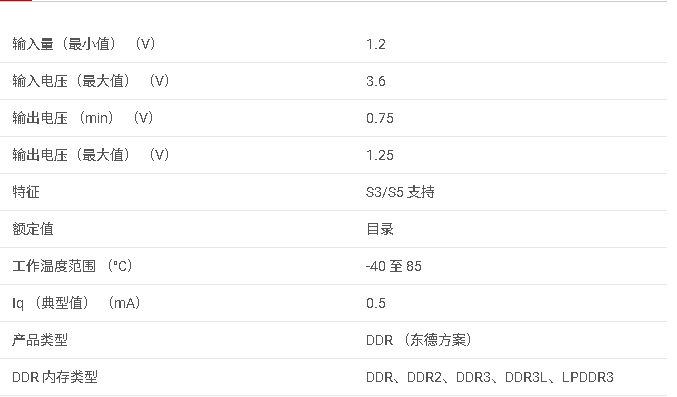

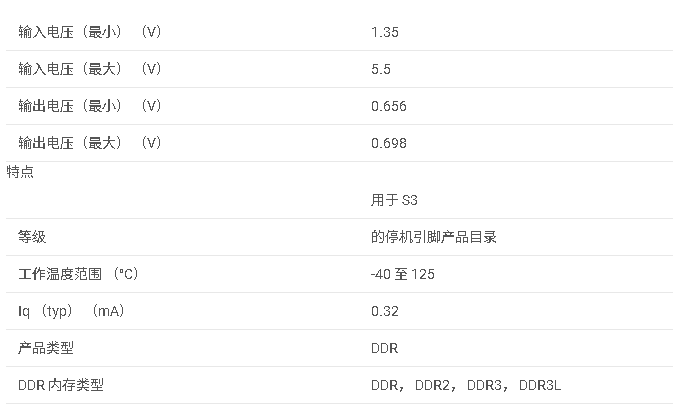

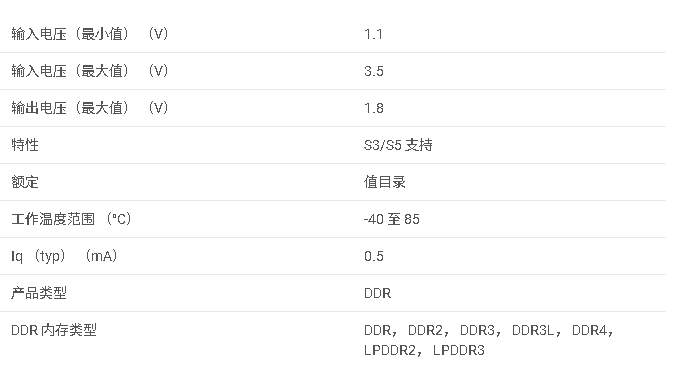

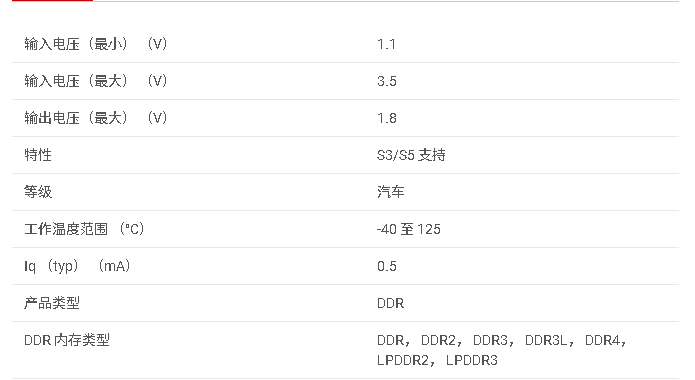

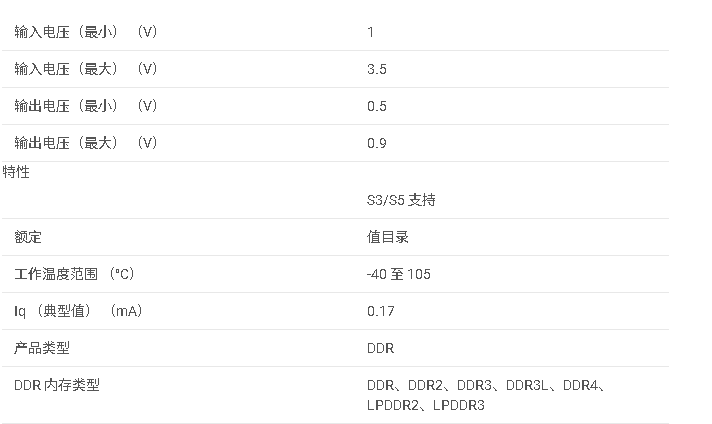

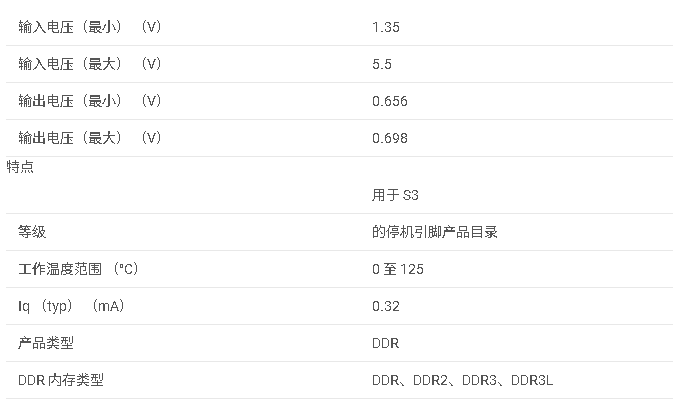

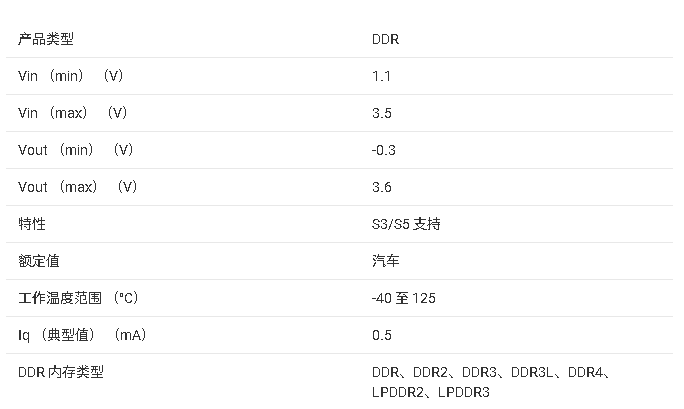

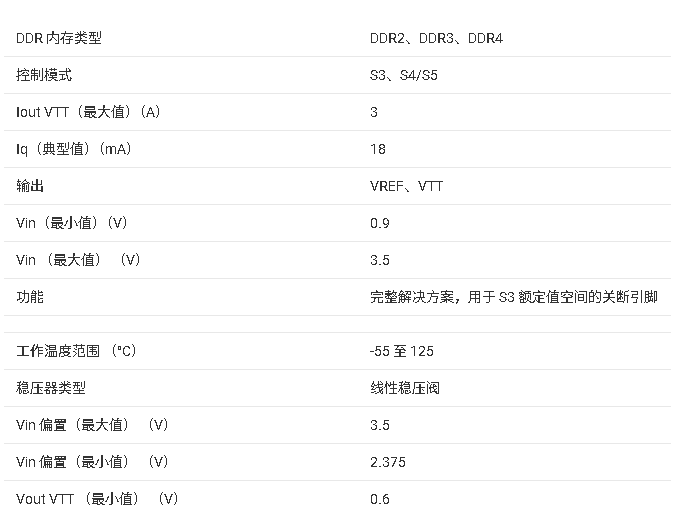

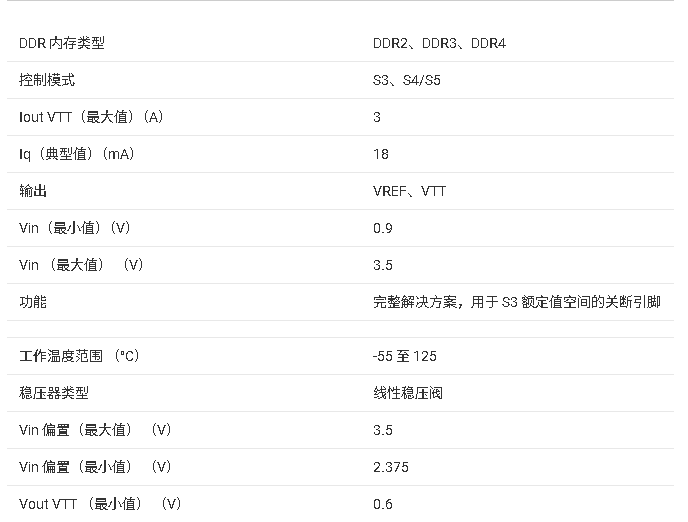

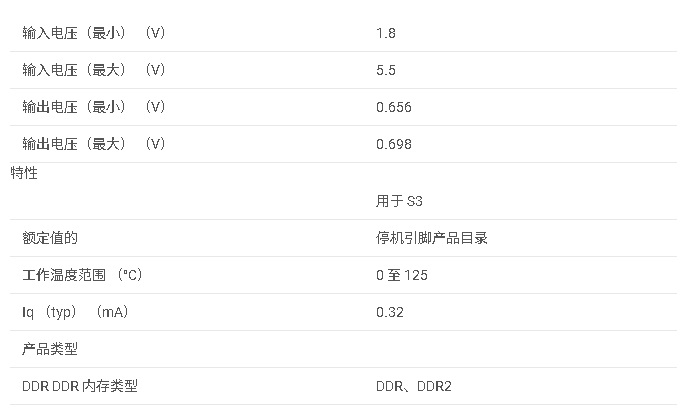

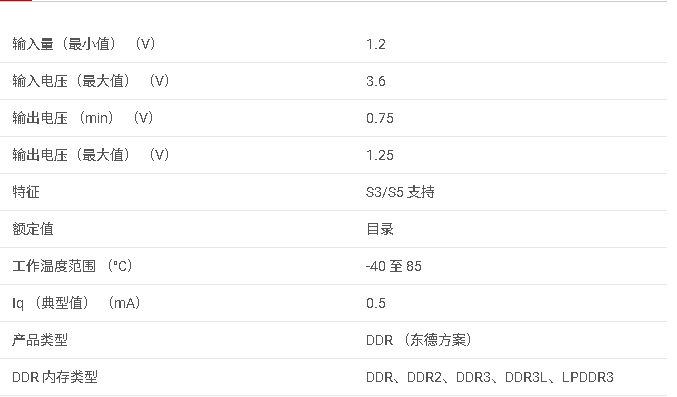

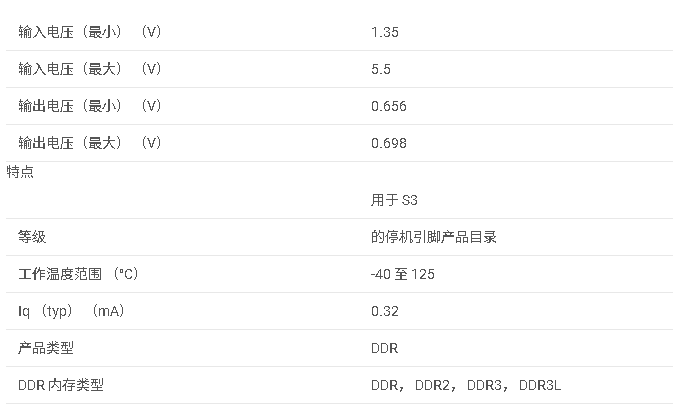

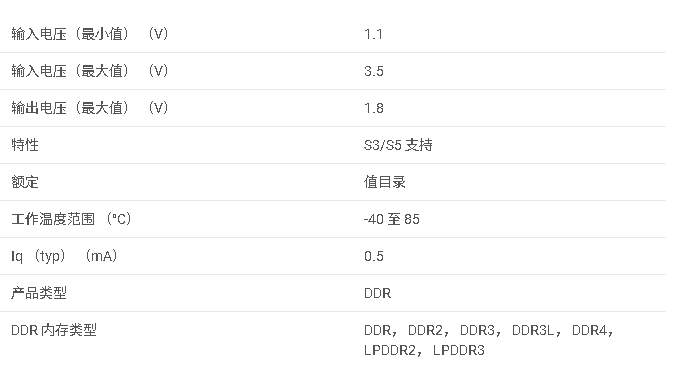

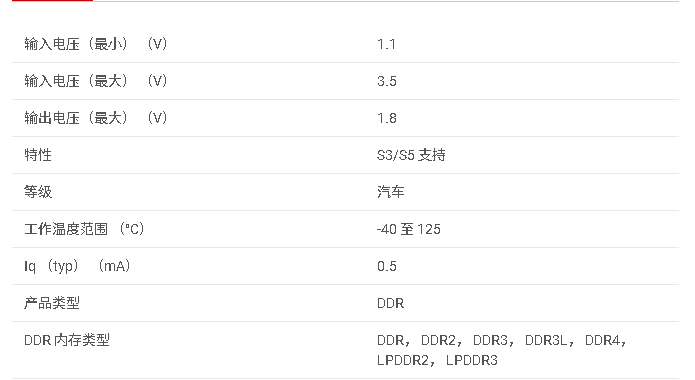

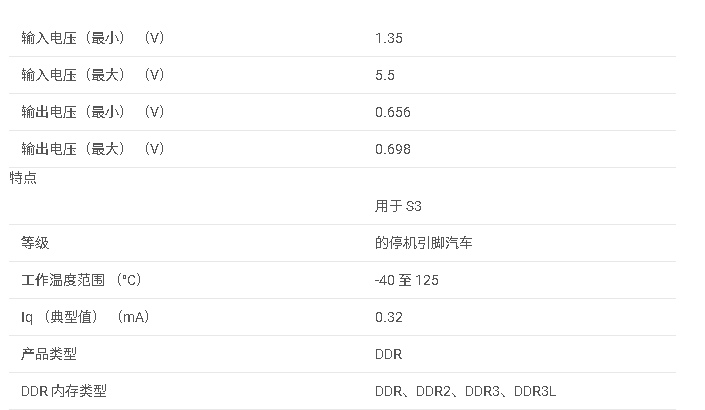

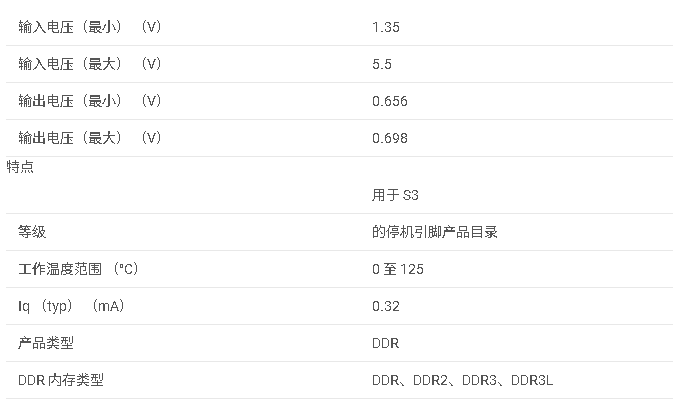

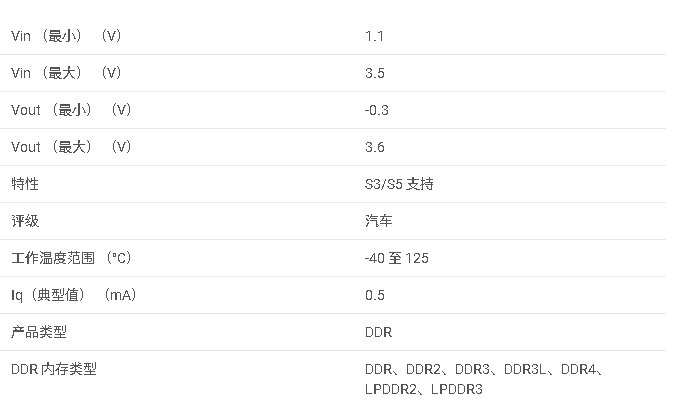

TPS51200A-Q1 器件是一款灌電流和源極雙數據速率 (DDR) 終端穩壓器,專為低輸入電壓、低成本、低噪聲系統而設計,其中空間是關鍵考慮因素。

該器件保持快速瞬態響應,最小輸出電容僅為

2025-09-09 14:28:07 713

713

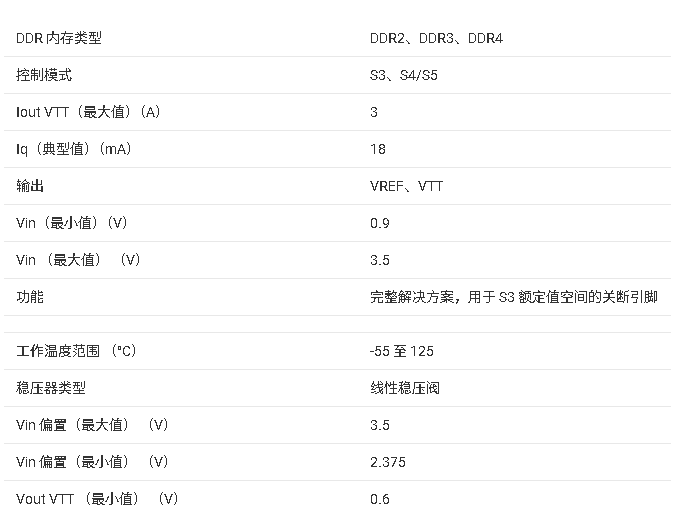

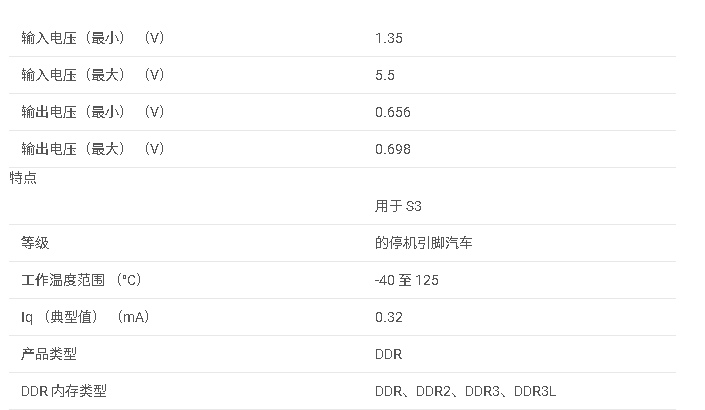

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應用。TPS7H3302 VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源

2025-09-09 13:53:22 688

688

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應用。TPS7H3302 VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源

2025-09-09 13:48:37 756

756

或者會數據出錯,而L14層的走線眼圖就好很多,再優化一下就會有一定的裕量,看起來過孔stub長居然對DDR4的信號質量有一定的改善作用。

這個原理其實在上篇文章中講到過,我們再來重溫一下:過孔stub

2025-09-04 10:50:26

如何利用 DDR 參數文件生成 Linux 映像

2025-09-02 06:39:54

EasyGo DeskSim是一款配置型的實時仿真軟件,它允許用戶將 Simulink 算法程序快速部署到 EasyGo 實時仿真機上。實時仿真機支持選配不同的 FPGA 芯片和 IO 模塊,能夠處理高速信號,并通過 IO 模塊輸出真實的仿真結果,可滿足用戶在科研、教學或工業測試中的多樣化需求。

2025-08-30 09:53:09 801

801

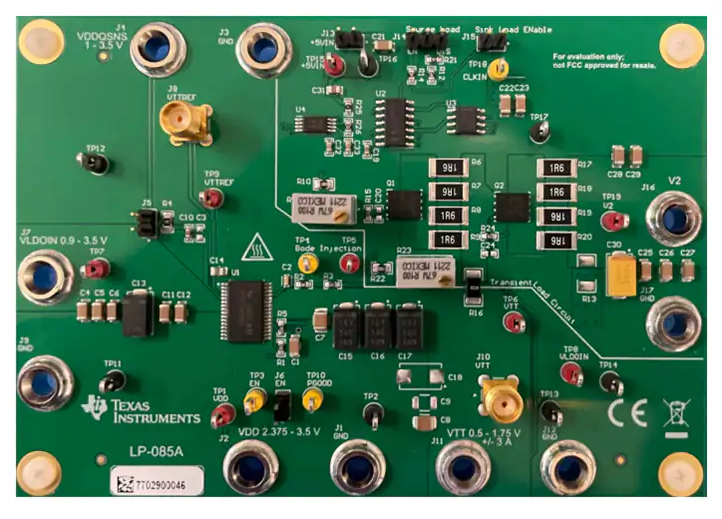

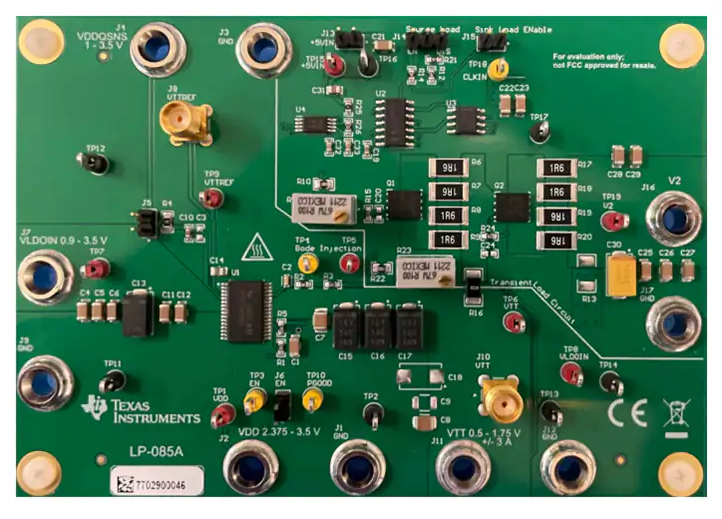

3A,支持測試DDR、DDR2、 DDR3、DDR3L和DDR4。該評估模塊配有方便的測試點和跳線,用于評估TPS7H3302-SEP DDR端子。TPS7H3302EVM評估模塊非常適合用于抗輻射DDR電源應用以及用于DDR、DDR2、DDR3和DDR4的存儲器終端穩壓器。

2025-08-27 16:14:21 831

831

憑借與紫光國芯的緊密合作,貞光科技能夠為客戶提供DDR3、LPDDR4及LPDDR4X全系列車規級存儲產品。在產品覆蓋、技術支持和供應保障等方面的綜合優勢,使貞光科技成為車載電子領域可靠且高效

2025-08-26 16:12:15 1426

1426

ATE測試,即自動化測試設備,是一種高度集成化、自動化的電子測試技術。它通過計算機控制,結合多種測試模塊,對電子元器件、消費電子、電路板等進行功能和性能測試。ATE測試系統能夠自動施加測試信號,采集響應數據,并與預設標準進行比對,快速判斷被測對象是否符合質量要求。

2025-08-19 11:33:44 1646

1646 EasyGo DeskSim是一款配置型的實時仿真軟件,它允許用戶將 Simulink 算法程序快速部署到 EasyGo 實時仿真機上。實時仿真機支持選配不同的 FPGA 芯片和 IO 模塊,能夠處理高速信號,并通過 IO 模塊輸出真實的仿真結果,可滿足用戶在科研、教學或工業測試中的多樣化需求。

2025-08-18 11:32:51 4723

4723

本測試方案旨在利用振動分析技術,結合高精度數采設備,實現對數控機床刀具質量的快速評估。該方法通過監測刀具在敲擊激勵下的振動響應,利用振動信號的特征參數來評估刀具的阻尼效果,進而判斷其質量優劣。

2025-08-07 10:24:36 1249

1249

≤100ps)。

若眼圖閉合,說明信號質量差,需優化物理層(如更換電纜、調整終端電阻)。

3. 協議級過濾與統計

工具:Teledyne LeCroy USB Protocol Suite的“Error

2025-08-01 15:00:38

眼圖是一個統計疊加的概念,是一系列數字信號在示波器上積累而顯示的圖形,通過它可以觀察出碼間串擾和噪聲對系統的影響,從而估計系統優劣。一個完整的眼圖應該包含從“000”到“111”的所有狀態組,且

2025-07-30 17:33:32 4935

4935

本文緊接著前一個文檔《AD設計DDR3時等長設計技巧-數據線等長 》。本文著重講解DDR地址線、控制信號線等長設計,因為地址線、控制信號線有分支,SOC有可能帶有2片DDR或者更多,我們叫做T型分支

2025-07-29 16:14:51 2

2 (如NAK占比>1%表明鏈路不穩定)。

結合眼圖測試功能,分析信號質量(如眼高、眼寬),定位物理層問題(如線纜老化、連接器氧化)。

設備兼容性驗證

場景:新部署的GPU或NVMe

2025-07-29 15:02:27

完整性保障

眼圖分析:通過眼圖評估信號質量,確保眼高、眼寬滿足協議要求。例如,PCIe 5.0要求時鐘抖動<50ps,若眼圖閉合或抖動超標,需檢查硬件連接(如探頭、線纜)或調整信號閾值

2025-07-28 17:28:18

的講解數據線等長設計。? ? ? 在另一個文件《AD設計DDR3時等長設計技巧-地址線T型等長》中著重講解使用AD設計DDR地址線走線T型走線等長處理的方法和技巧。

2025-07-28 16:33:12 4

4 隨著數據量的不斷增加,對信號帶寬的需求也在不斷增長。同時,在長距離傳輸中,數字信號可能會因為傳輸介質的特性而衰減。現有的數字電路/鏈路等已經無法滿足日益增長的帶寬和質量需求,導致傳輸速度變慢及信號質量變差,影響數據的正確、快速傳輸。

2025-07-25 15:40:51 4398

4398

提供的標準語音樣本文件進行測試,也支持上傳真實的業務音頻文件,以更貼近實際應用場景。默認音頻文件便于快速開展基準測試,而真實音頻文件則有助于驗證在具體語音內容和編碼格式下的傳輸質量。 3. 關鍵網絡

2025-07-22 11:15:03

? 本原創文章由深圳市小眼睛科技有限公司創作,版權歸本公司所有,如需轉載,需授權并注明出處(www.meyesemi.com)

1.實驗簡介

實驗目的:

完成 DDR3 的讀寫測試。

實驗環境

2025-07-10 10:46:48

出整個數據流的路徑。這是一個典型的FPGA圖像處理系統架構:

輸入端 (Camera Input) -> ISP (圖像信號處理) -> DDR3 緩存 (Frame

2025-07-06 15:18:53

EasyGo DeskSim是一款配置型的實時仿真軟件,它允許用戶將 Simulink 算法程序快速部署到 EasyGo 實時仿真機上。實時仿真機支持選配不同的 FPGA 芯片和 IO 模塊,能夠處理高速信號,并通過 IO 模塊輸出真實的仿真結果,可滿足用戶在科研、教學或工業測試中的多樣化需求。

2025-06-30 14:11:05 884

884

DDR內存占據主導地位。全球DDR內存市場正經歷一場前所未有的價格風暴。由于原廠加速退出DDR3/DDR4市場,轉向DDR5和HBM(高帶寬內存)生產,DDR3和DDR4市場呈現供不應求、供需失衡、漲勢延續的局面。未來,DDR5滲透率將呈現快速提升,市場份額增長的趨勢。

2025-06-25 11:21:15 2010

2010

,為工程師提供了實時眼圖與頻譜分析的一體化解決方案。本文將深入探討DSOX2004A如何通過其關鍵技術實現精準的眼圖和頻譜測量,助力用戶高效解析復雜信號。 ? 一、DSOX2004A示波器的核心功能概述 DSOX2004A是一款高性能混合信號示波器,具備以下關鍵特性:

2025-06-24 12:06:50 528

528

絡中,數據通過雙絞線上的差分信號傳輸。信號質量直接影響節點正確解讀數據的能力。信號質量差可能表現為:

位錯誤 :由于噪聲或信號失真導致的位誤判。 幀錯誤 :CAN幀結構錯誤,導致接收節點拒絕。 總線

2025-06-07 08:46:40

網絡配線架打線操作的質量檢查是確保網絡布線系統穩定性和可靠性的關鍵環節。以下從外觀檢查、電氣性能測試、功能驗證、標識與文檔檢查四個維度,系統闡述質量檢查的核心措施及具體方法: 一、外觀檢查 1.

2025-06-06 10:30:16 786

786

隨著汽車產業向智能化、網聯化加速轉型,高級駕駛輔助系統(ADAS)和智能駕駛技術已成為現代汽車不可或缺的核心組件。紫光國芯作為國內領先的存儲器芯片制造商,其車規級DDR3存儲產品在智能駕駛和ADAS

2025-06-05 16:50:17 1225

1225

對于高質量圖形顯示的應用要求,用戶通常采用功能強大及搭載DDR高速接口的MPU來實現更多功能和更流暢的畫面。但在開發過程會遇到DDR高速總線設計的難題,同時Linux系統難以實現類似MCU的快速啟動性能。瑞薩新推出的RZ/A3M HMI MPU幫助客戶解決這些問題。

2025-05-27 16:14:30 894

894

,如包起始或同步域。

信號質量參數:

眼圖分析:測量眼高、眼寬、抖動等參數,評估信號質量。

抖動測試:包括隨機抖動(RJ)和確定性抖動(DJ),確保符合USB規范。

上升/下降時間:測量信號邊沿速率

2025-05-16 15:55:16

革命性的眼圖分析功能,為工程師提供了一整套從信號捕獲到故障定位的完整解決方案。本文將深入解析MSO54B眼圖分析的核心技術、應用場景及操作要點,揭示其如何成為高速信號測試領域的標桿產品。 ? 一、技術架構:構建眼圖分析的硬件基石 1. 超高分

2025-05-13 15:57:13 547

547

下面是調用的DDR3模塊的,模塊的倒數第二行是,模塊的時鐘輸入,時鐘源來自PLL產生的系統時鐘的倍頻。

2025-05-03 10:21:00 1339

1339

在現代高速數字通信系統中,眼圖分析是評估信號完整性的核心工具。泰克MDO32系列示波器憑借其強大的混合域分析能力,為工程師提供了經濟高效的眼圖測試方案。本文將結合理論與實際操作,系統講解

2025-04-30 15:14:44 874

874

LP2996-N 和 LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 標準 DDR-SDRAM 終止規范。該器件還支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3

2025-04-29 18:11:05 834

834

終端供電。這 該器件還支持 DDR3 VTT 端接,VDDQ 電壓為 1.5 V(典型值)。此外,TPS51100 包括集成的睡眠狀態控制、在 S3 中將 VTT 置于 Hi-Z(暫停到 RAM)和軟

2025-04-29 17:15:20 774

774

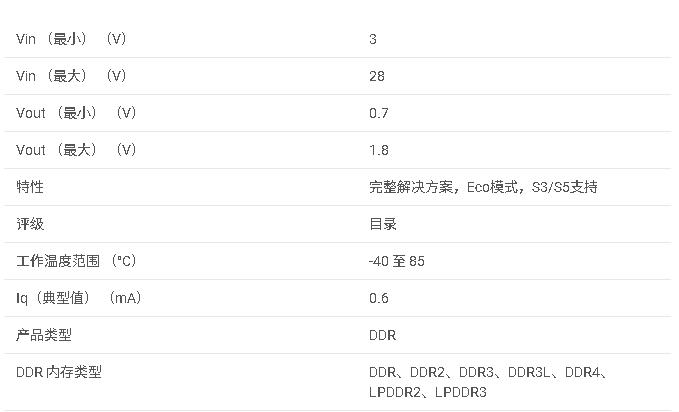

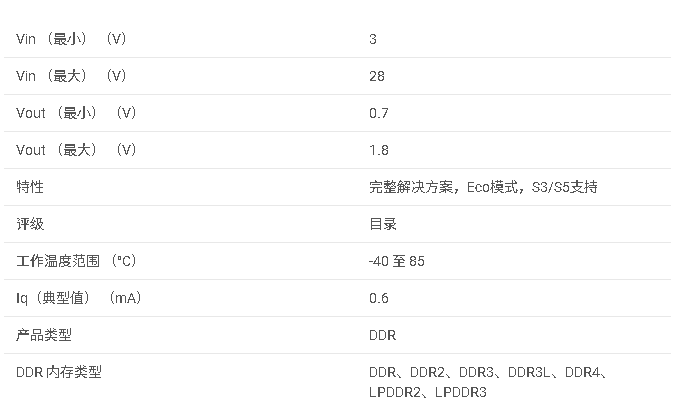

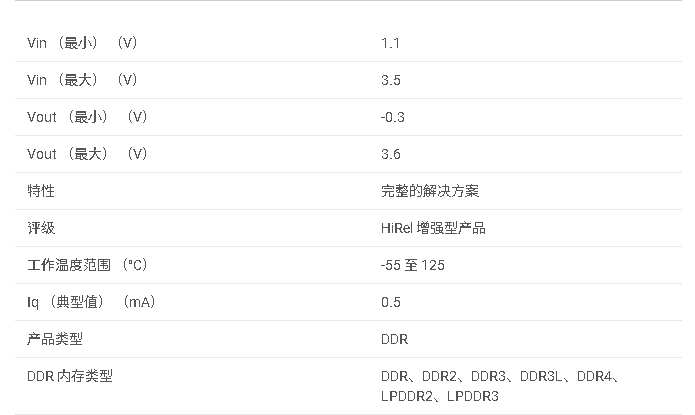

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 內存系統提供完整的電源。它將同步降壓控制器與 3A 灌電流/拉

2025-04-29 16:38:02 1031

1031

在高速PCB設計中,DDR模塊是絕對繞不過去的一關。無論你用的是DDR、DDR2還是DDR3,只要設計不規范,后果就是——信號反射、時序混亂、系統頻繁死機。

2025-04-29 13:51:03 2491

2491

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

TPS51200 器件是一款灌電流和拉電流雙倍數據速率 (DDR) 終端穩壓器,專為空間受限的低輸入電壓、低成本、低噪聲系統而設計。

該TPS51200保持快速瞬態響應,并且需要的最小輸出電容

2025-04-29 09:59:25 1345

1345

TPS51200-Q1 器件是一款灌電流和拉電流雙倍數據速率 (DDR) 終端穩壓器,專為空間受限的低輸入電壓、低成本、低噪聲系統而設計。

TPS51200-Q1 器件保持快速瞬態響應,并且

2025-04-28 16:21:07 852

852

TPS59116 為 DDR/SSTL-2、DDR2/SSTL-18 和 DDR3 內存提供完整的電源 系統。它將同步降壓控制器與 3A 灌電流/拉電流跟蹤線性穩壓器和緩沖低噪聲基準集成在一起

2025-04-28 13:54:45 814

814

TPS51216 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內存系統提供完整的電源。它將同步降壓穩壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-28 11:09:05 663

663

TPS51916 器件以最低的總成本和最小的空間為 DDR2、DDR3、DDR3L 和 DDR4 內存系統提供完整的電源。它集成了同步降壓穩壓控制器 (VDDQ),具有 2A 灌電流和 2A 源跟蹤 LDO (VTT) 和緩沖低噪聲基準 (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬態響應,并且只需要 1 × 10μF 的陶瓷輸出電容。該器件支持遠程感應功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 總線的所有電源要求。VTT 電流

2025-04-28 10:04:48 685

685

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、 和 LPDDR3 內存系統。它將同步降壓控制器與 1A 灌電流/拉電流集成在一起 跟蹤線性穩壓器和緩

2025-04-27 13:35:32 741

741

TPS51716為 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的電源 以最低的總成本和最小空間實現內存系統。它集成了一個同步降壓 具有 2A 灌電流/拉電流跟蹤 LDO

2025-04-27 11:36:05 763

763

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 規范 DDR-SDRAM 終止。該器件還支持 DDR2、DDR3 和 DDR3L VTT 總線端接,帶 V~DDQ~最小為 1.35V

2025-04-26 15:02:50 746

746

TPS51216-EP 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內存系統提供完整的電源。它將同步降壓穩壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-26 11:12:30 681

681

TPS51200-EP 器件是一款灌電流和拉電流雙倍數據速率 (DDR) 終端穩壓器 專為空間受限的低輸入電壓、低成本、低噪聲系統而設計 考慮。

TPS51200-EP 保持快速瞬態響應,并且

2025-04-26 10:26:35 1335

1335

TPS51200A-Q1 器件是一款灌電流和拉電流雙倍數據速率 (DDR) 終端穩壓器,專為空間受限的低輸入電壓、低成本、低噪聲系統而設計。

該器件保持快速瞬態響應,并且只需要 20 μF

2025-04-25 10:07:15 1053

1053

在全球科技競爭加劇、國產替代加速推進的背景下,紫光國芯憑借其在DDR3與RDIMM等高端內存芯片領域的技術積累,不斷實現突破,推動國產存儲芯片向高端市場邁進。作為其核心代理商,貞光科技在市場推廣

2025-04-16 16:39:30 1342

1342

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

燦芯半導體(上海)股份有限公司(燦芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平臺的DDR3/4, LPDDR3/4 Combo IP。該IP具備廣泛的協議兼容性,支持DDR3

2025-03-21 16:20:03 984

984 初次使用XC7A35T-FGG484做設計,用的是25MHZ有源晶振,有源晶振3.3V供電,DDR3的供電1.35V,現在接上晶振后,DDR3的供電變成1.8V

求助怎么解決。

2025-03-21 14:25:05

0xDEADBEEF。

我們嘗試并驗證了一些事情:

硬件:

- 原理圖審查并仔細檢查

- 檢查電壓。GVDD、VREF、VTT 和 VPP

- 輸入和輸出 DDR 時鐘

- DRAM 重置信號正確

- MEM

2025-03-21 07:15:45

在進行DDR(雙倍數據速率)信號測試時,普源DHO1072示波器是一款功能強大的工具,能夠幫助用戶準確分析和調試信號。以下是使用普源DHO1072示波器進行DDR信號測試的幾個關鍵要點。 一

2025-03-14 12:06:00 942

942

請問怎么使用STM32F723的開發板測試HS的眼圖,開發板程序包含USBD_HS_TESTMODE_ENABLE后按教程修改了USBD_LL_TestMode函數,結果文件顯示USBx_DEVICE定義的USBx_BASE沒有定義,應該怎么改呀

2025-03-13 07:32:58

DDR內存控制器是一個高度集成的組件,支持多種DDR內存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設計的架構來優化內存訪問效率。

2025-03-05 13:47:40 3573

3573

據報道,業內人士透露,全球三大DRAM內存制造商——三星電子、SK海力士和美光,有望在2025年內正式停產已有多年歷史的DDR3和DDR4兩代內存。 隨著技術的不斷進步和消費級平臺的更新換代

2025-02-19 11:11:51 3465

3465 ;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM內存模塊,專為滿足現代計算需求而設計。該產品以其高帶寬和低功耗的特性,廣泛應用于個人電腦、服務器和嵌入式系統中,成為市場上備

2025-02-10 20:10:39

最近一項目中利用ADS1274采集20mv的微量信號,采集出來數據不正確。

具體情況為:

輸入前端模擬信號幅度采集出來數據換算后

5.10mv,4.338mv;

5.11mv 4.348mv

2025-02-06 06:29:51

示波器作為電子測試測量領域的重要工具,其功能多樣且強大。其中,眼圖分析功能是示波器在數字信號完整性測試中的一項關鍵應用。眼圖不僅直觀展示了數字信號的整體特征,還能夠反映出碼間串擾、噪聲、抖動等關鍵

2025-02-02 14:04:00 2311

2311 的重要性 通信質量評估 :信道信號強度是評估通信質量的重要參數,它可以幫助我們了解信號在傳輸過程中的損耗情況。 網絡優化 :通過測試信道信號強度,可以發現網絡覆蓋的盲區,為網絡優化提供數據支持。 設備性能測試 :信道信

2025-01-22 16:25:35 3622

3622 在現代通信系統中,調制技術是實現信息傳輸的關鍵環節。調制過程涉及將原始信息信號(基帶信號)轉換成適合在特定信道上傳輸的形式。這一過程對信號的傳輸質量有著深遠的影響,包括信號的可靠性、傳輸效率、抗干擾

2025-01-21 09:25:53 1743

1743 一個10Nf~100nF的電容,整個VTT電路上需要有uF級大電容進行儲能。

一般情況下,DDR的數據線都是一驅一的拓撲結構,且DDR2和DDR3內部都有ODT做匹配,所以不需要拉到VTT做匹配即可

2025-01-21 06:02:11

復雜的實時嵌入式系統應用,支持多種內存接口和豐富的外設端口,滿足多樣化場景需求。

通過硬核NPU,JPU,MIPI 來支持邊緣智能應用,為FPGA市場注入新的活力。SOM模組標配1GB DDR3

2025-01-10 14:32:38

很多方法都可以表征高速數字通道,目標是驗證說明通道合規性的特定信號完整性指標。S參數和阻抗等指標都很有用,但還有一項重要測量需要使用數字比特流進行評估:眼圖。 作為通道合規性的一部分,眼圖是一種有用

2025-01-08 11:27:02 2632

2632

,保證良好的電氣連接。

4、焊接質量審核

檢查已焊接元器件的接點,確保焊接牢固,無虛焊或漏焊現象。

5、性能測試

驗證元器件的功能指標,確保其性能滿足產品設計的需求。

6、材料認證

確保使用正確的材料

2025-01-07 16:16:16

電子發燒友App

電子發燒友App

評論