在亞微米以下的電路設計中,需要對電路進行全芯片的ESD保護結構的設計。如何使全芯片有效面積盡可能小、ESD性能可靠性滿足要求且不需要增加額外的工藝步驟成為全芯片設計者的主

2012-04-23 10:17:42 4709

4709

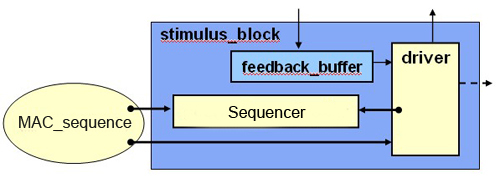

物聯網(IoT)應用興起,除為半導體廠開創新的市場商機外,亦帶來諸多積體電路(IC)設計新挑戰,特別是系統單芯片(SoC)功能整合度愈來愈高,已使IC設計業者面臨更嚴峻的數位和類比混合信號(Mixed Signal)電路驗證(Verification)挑戰。

2014-08-14 09:36:31 1126

1126 摩爾定律究竟還能走多遠?一旦摩爾定律正式走入歷史,半導體產業該如何繼續向前邁進?而在所謂的「后摩爾定律時代」,IC業者面臨的挑戰是什么?又該如何因應?

2017-02-06 11:04:39 7048

7048 中國IC芯片制造業保持著高速增長的勢頭,但面臨的挑戰也前所未有地嚴峻

2011-11-09 09:06:01 2078

2078 請問有那寫途徑可以買到直徑10微米的鉑絲

2021-04-04 22:31:50

本文討論 IC制造商用于克服精度挑戰的一些技術,并讓讀者更好地理解封裝前和封裝后用于獲得最佳性能的各種方法,甚至是使用最小體積的封裝。

2021-04-06 07:49:54

模型。使的他在亞微米和深亞微米工藝的今天依舊是模擬電路仿真的主要工具之一。AVANTI是IC設計自動化軟件的“英雄少年”,它的HSPICE因其在亞微米和深亞微米工藝中的出色表現而在近年得到了廣泛

2011-12-19 16:50:52

為原理的數字電路。 10、IC封裝:指把硅片上的電路管腳用導線接引到外部接頭處,以便與其它器件連接。 11、IC工藝線寬:線寬:4微米、1微米、0.6微米、0.35微米、0.25微米、0.18微米

2021-05-31 06:21:24

微米傳感器是屬于高精度的傳感器嗎?可測量的最大精度是多少?

2015-07-19 09:41:08

越來越薄,柵極泄漏呈指數增長,最終動態功耗等于亞閾值泄漏電流,也等于柵極泄漏電流。這就迫使業界必須從IC的設計端就開始采用低功耗設計技術。為了應對這些挑戰,設計工程師們開始提倡采用復雜的時鐘門電路開關

2019-06-27 08:05:18

摘 要:EDA技術是現代電子設計技術的核心,它在現代集成電路設計中占據重要地位。隨著深亞微米與超深亞微米技術的迅速發展,FPGA設計越來越多地采用基于VHDL的設計方法及先進的EDA工具。本文詳細

2019-06-27 08:01:28

告訴《中國電子報》記者,據統計,超過60%的IC失效都源于ESD。 隨著超大規模集成電路工藝的高速發展,特征尺寸已經到深亞微米階段,大大提高了集成電路的性能及運算速度,但隨著器件尺寸的減小,對可靠性

2013-02-21 10:54:18

超大規模集成電路工藝的高速發展,特征尺寸已經到深亞微米階段,大大提高了集成電路的性能及運算速度,但隨著器件尺寸的減小,對可靠性的要求也越來越高。 高集成度意味著單元線路會越來越窄,耐受靜電放電的能力越來越差

2013-08-16 10:22:02

HDMI接收器和發射器的IC芯片全部采用深亞微米工藝制造。亞微米CMOS制程十分敏感,通常設有ESD保護限制(最高2kV),必須符合人體放電模式(HBM)標準。另外,LCD電視和機頂盒(STB)等

2013-11-21 09:57:59

,基于靜態電流(IDDQ)的測試方法被廣泛使用。然而,隨著深亞微米技術時代的到來,總的靜態漏電流急劇增加,IDDQ測試技術受到嚴峻挑戰,因此,需要尋找新的測試技術,而瞬態電流測試技術提供一個很好的替代或補充。這種測試方法能夠檢測傳統測試和IDDQ測試所不能檢測的缺陷。

2019-09-18 07:31:31

大佬們好我有一定的Labview基礎,然而對Labview的雙目視覺測量所知甚少,現在有一個需求,就是在比較小的空間內實現微米級的三維動態測量,想知道通過Labview雙目視覺有實現的可能性嗎?希望大佬們多多指導。感激不盡!謝謝!

2020-07-21 21:50:21

亞嵌起源AKA發萌于1998年早些時候的水木清華BBS上,1998年10月1日宣告成立,2000年前后發展到頂峰,此后受骨干成員出國、成家、創業等影響,加上當時網絡泡沫的破滅,2000年后進入低潮

2010-04-09 15:14:56

有什么辦法吧亞像素輪廓坐標轉換后還是亞像素的?

2019-06-20 20:07:46

“2017至2019年,三亞將實施電網建設改造與電纜入地改造,重點解決三亞主城區、鎮墟、重點工業園區單回路供電和可轉供率不高的問題,同時美化城市景觀。在電網建設上共計投資約20.49億元。”這是三亞

2017-10-16 14:48:11

亞微米(1um≥L≥0.35um),多晶硅柵電阻率高的問題變得越發嚴重。為了降低多晶硅柵的電阻,半導體業界利用多晶硅和金屬硅化物(polycide)的雙層材料代替多晶硅柵,從而降低多晶硅柵的電阻

2018-09-06 20:50:07

對于vdsat我的個人的理解是:該器件在當前的VGS偏置下,達到飽和電流(電流的最大值)時所需的最小VDS。比較困惑的是,低電壓設計的時候管子經常會在亞閾值區,管子處于亞閾值區的時候,spectre

2021-06-24 06:56:31

36ohm/sq。雖然高電阻率的多晶硅柵對MOS管器件的直流特性是沒有影響的,但是它嚴重影響了MOS管器件的高頻特性,特別是隨著MOS管器件的特征尺寸不斷縮小到亞微米(1um≥L≥0.35um),多晶硅

2018-11-06 13:41:30

項目開發需要1微米以上的紅外LED光源,哪里有銷售,請知道的高手指點。先謝了!

2012-04-08 11:35:11

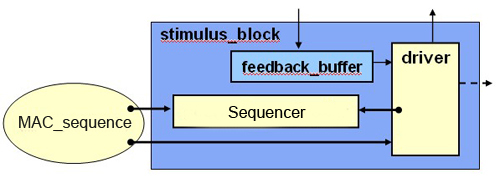

隨著深亞微米工藝的發展, FPGA的容量和密度不斷增加,以其強大的并行乘加運算(MAC)能力和靈活的動態可重構性,被廣泛應用于通信、圖像等許多領域。

2019-10-30 06:16:57

如何用“亞印刷”法制作印刷電路板?

2021-04-23 06:08:22

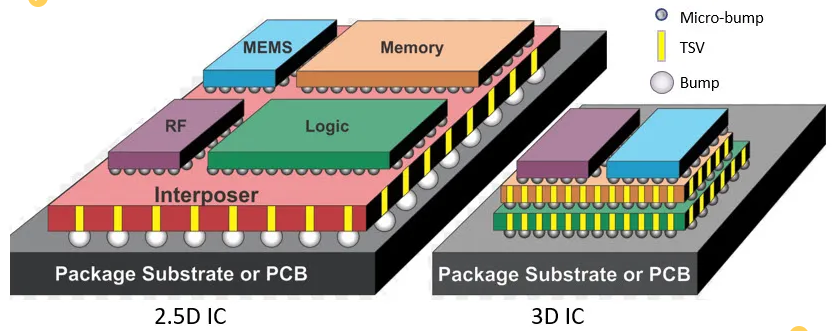

近年來,消費者對電子產品的更高性能和更小尺寸的要求持續推動著SoC(系統級芯片)產品集成水平的提高,并促使其具有更多的功能和更好的性能。要繼續推動這種無止境的需求以及繼續解決器件集成領域的挑戰,最關鍵的是要在深亞微米半導體的設計、工藝、封裝和測試領域獲得持續的進步。

2019-08-23 07:21:02

和低功耗設計、設計驗證、芯片測試和可測性設計等主題,著重探討了深亞微米數字集成電路設計面臨的挑戰和啟示。本書可作為高等院校電子科學與技術(包括微電子與光電子)、電子與信息工程、計算機科學與技術、自動化等

2009-02-12 09:51:07

機器開發人員面臨哪些軟件挑戰以及硬件挑戰?如何去應對這些挑戰?

2021-06-26 07:27:31

【作者】:張科營;郭紅霞;羅尹虹;何寶平;姚志斌;張鳳祁;王園明;【來源】:《原子能科學技術》2010年02期【摘要】:采用TCAD工藝模擬工具按照等比例縮小規則構建了從亞微米到超深亞微米級7種

2010-04-22 11:50:00

0.13微米幾何設計規則與0.5微米幾何設計規則

2019-04-09 22:43:50

請問一下,ADI 的哪款產品能夠測量幅值0-100微米,頻率0-20Hz的振動信號呢?要求測量精度不低于5微米,聽說ADXL203可以?初涉傳感器領域,希望大家多多指教。

2019-01-30 10:32:12

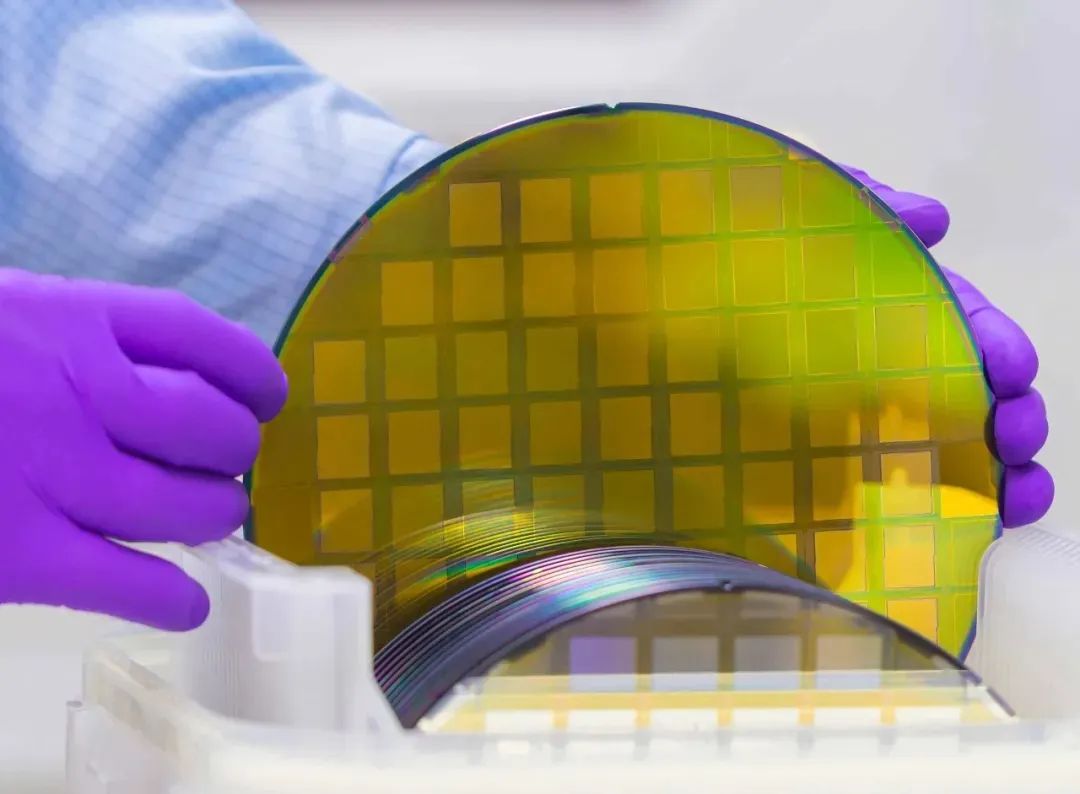

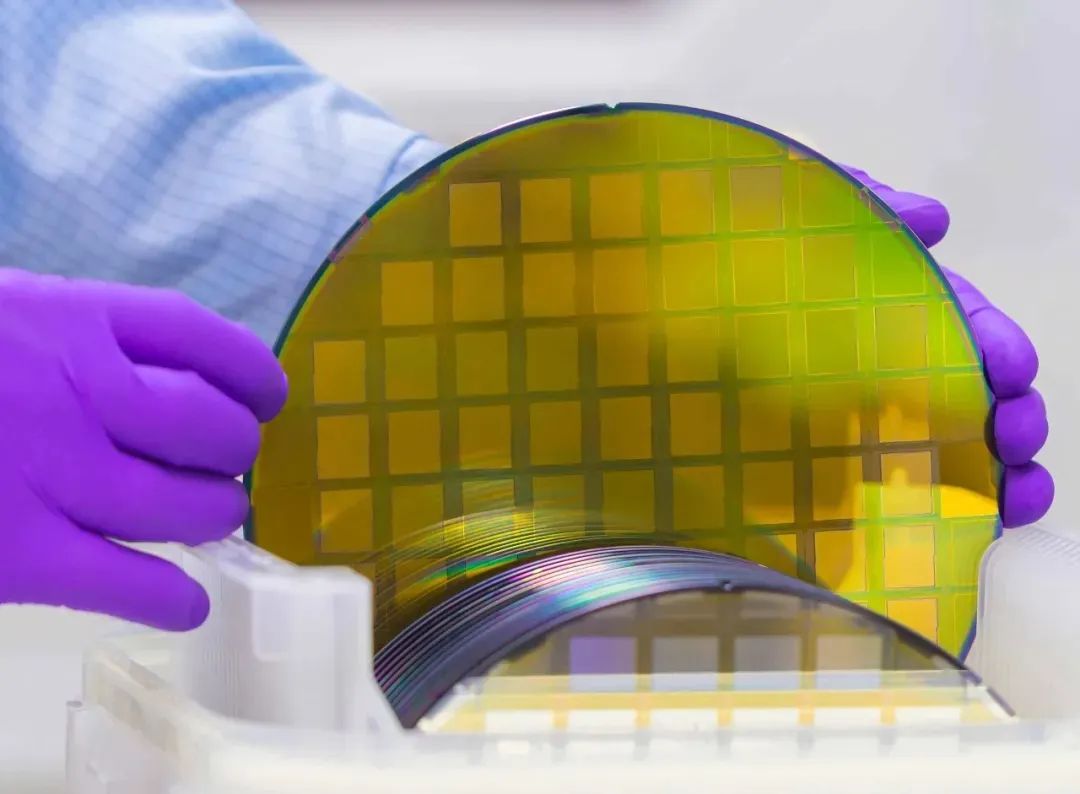

工序。光刻:IC生產的主要工藝手段,指用光技術在晶圓上刻蝕電路。線寬:4微米/1微米/0.6微未/0.35微米/035微米等,是指IC生產工藝可達到的最小導線寬度,是IC工藝先進水平的主要指標.線寬

2013-01-11 13:52:17

的設計流程。從市場占有來看,Cadence的強項產品為IC板圖設計和服務,Synopsis的強項產品為邏輯綜合,MentorGraphics的強項產品為PCB設計和深亞微米IC設計驗證和測試等。毫無疑問

2018-08-24 16:48:10

,以及在不同應用領域中面臨的挑戰。智能卡天線設計需要考慮的因素智能卡天線是一種電氣組件,可通過讀卡器產生的射頻(RF)磁場的電磁感應,向智能卡集成電路(IC)供電。它同時也是智能卡IC與讀卡器之間的通訊

2018-12-05 09:55:07

高清音頻的三大主要應用機會是什么?高清音頻IC的設計挑戰是什么?

2021-06-03 06:30:30

本文介紹了以超深亞微米技術為支撐的 SOC 的定義以及芯片設計方法,并闡述了軟硬件協同設計理論、IP 核生成及復用技術、超深亞微米IC 設計面對的難題以及SOC 測試與驗證技術。

2009-06-19 09:28:12 35

35

隨著工藝的發展,器件閾值電壓的降低,導致靜態功耗呈指數形式增長。進入深亞微

米工藝后,靜態功耗開始和動態功耗相抗衡,已成為低功耗設計一個不可忽視的因素

2009-09-15 10:18:10 18

18 隨著工藝的發展,器件閾值電壓的降低,導致靜態功耗呈指數形式增長。進入深亞微米工藝后,靜態功耗開始和動態功耗相抗衡,已成為低功耗設計一個不可忽視的因素。針對近

2009-09-15 10:18:10 26

26 本文通過對傳統大規模集成電路設計流程的優化,得到了更適合于深亞微米工藝集成電路的后端設計流程,詳細介紹了包括初步綜合、自定義負載線的生成、版圖規劃、時鐘樹綜合

2009-12-14 11:03:09 15

15 和艦科技自主創新研發的0.16 微米硅片制造工藝技術在原有比較成熟的0.18 微米工藝技術基礎上,將半導體器件及相關繞線尺寸進行10%微縮(實際尺寸為0.162 微米),大大降低了芯

2009-12-14 11:23:36 25

25 基于深亞微米MOS 器件溝道的熱噪聲淺析曾獻芳摘要: 隨著 MOS 器件工藝尺寸的不斷減小,其不斷增高的單位增益截止頻率足以滿足射頻/模擬電路的工作要求。然而,隨著溝

2009-12-15 14:31:04 10

10 超深亞微米IC設計中的天線效應李蜀霞 劉輝華 趙建明 何春(電子科技大學電子電子科學技術研究院 成都 610054)【摘要】本文主要分析了超深亞微米集成電路設計中天線效應

2009-12-19 14:54:53 45

45 摘要:就超深亞微米集成電路中高K柵介質、金屬柵、cU/低K互連等相關可靠性熱點問題展開討論.針對超深亞微米集成 電路可靠性問題.提出可靠性設計、生產過程的質量控制、可

2010-04-27 14:13:33 19

19 摘要:增強測試質量和抑制測試代價是超深亞微米集成電路測試及可測性設計領域的兩個研究主題。本文介紹了一個基于Mentor公司可測性設計工具的面向多種故障模型的超深亞微

2010-06-07 11:01:17 10

10 的能力和亞埃級的分辨率,同時,其集成了超低噪聲信號采集、超精細運動控制、標定算法等核心技術,使得儀器具備超高的測量精度和測量重復性。 CP系列微米到納米尺

2024-06-07 14:14:42

中圖儀器SJ5100亞微米級高精度光柵測長機常用于工業制造業精確測量物體長度、角度和位置等參數。它采用進口高精度光柵測量系統、高精密研磨直線導軌、高精度溫度補償系統、雙向恒測力系統、高性能計算機

2024-07-12 15:35:42

MIT研發出微米級的電池材料通過將微接觸印刷技術和基于病毒的自行裝配技術結合起來,麻省理工學院的研究人員聲稱研發出了一種微米級的電池。

采用微接觸印刷技

2008-09-02 08:48:26 870

870 ST推出獨立看門狗IC,增加芯片使能輸入,解決系統設計挑戰

中國,2008年12月17日 – 模擬和混合

2009-01-12 09:05:36 1955

1955 什么是亞音

亞音就是一個頻率較低的音頻信號,比如較常用的88.5Hz。亞音的作用主要是開啟靜噪,這樣即提高靈敏度又避免干擾和噪音。

2009-03-15 11:04:53 6619

6619 隨著深亞微米工藝技術日益成熟,基于IP復用的IC設計方法廣泛采用,集成電路芯片的規模越來越大,這對集成電路驗證技術和方法學提出了很大的挑戰。就如芯片

2009-04-04 10:58:40 2084

2084

分析了在超深亞微米階段,串擾對高性能芯片設計的影響,介紹了消除串擾影響的方法。 關鍵詞:串擾,布線,關鍵路徑,

2009-05-05 20:59:16 1434

1434

一種全新的深亞微米IC設計方法

本文分析了傳統IC設計流程存在的一些缺陷,并且提出了一種基于Logical Effort理論的全新IC設計方法。

眾所周知,傳統的IC設計流

2009-12-27 13:28:50 896

896

IC在后摩爾時代的挑戰和機遇

后摩爾時代的特點

隨著工藝線寬進入幾十納米的原子量級,反映硅工藝發展規律的摩爾定律">摩爾定律最終將難以為繼。于

2010-02-21 09:13:22 1489

1489 多內核處理器開發趨勢下的高性能視頻系統設計

時鐘頻率的提高帶來的高功耗、深亞微米半導體制造工藝漏電流產生的高功耗以及更多的設計挑戰促使處理器設計制造

2010-03-04 10:02:55 978

978

TSMC推出最新深亞微米互通式EDA格式

TSMC 7日宣布針對65納米、40納米及28納米工藝推出已統合且可交互操作的多項電子設計自動化(Electronic Design Automatio

2010-04-09 10:36:49 939

939 新型深亞微米電流靈敏放大器技術設計

隨著便攜式電子設備(PDA、射頻卡、GPS等)的廣泛應用,半導體存儲器得到了長足的發展。半導體存儲器的性能

2010-04-27 17:37:46 873

873

模擬/混合信號Ic設計一直是困擾很多中國Ic設計工程師的難題。與數字電路設計相比,模擬/混合電路設計要求更為嚴苛,而且需要嚴格的環境控制工藝。而對于深亞微米級的SOC設計還必

2011-03-31 16:16:10 0

0 集成電路測試是保證集成電路質量、發展的關鍵手段。CMOS 器件進入超深亞微米階段, 集成電路繼續向高集成度、高速度、低功耗發展, 使得IC 在測試和可測試性設計上都面臨新的挑戰。

2011-05-20 16:48:20 83

83 設計了一款應用于亞微米工藝的傳輸只讀存儲器的編程高壓的單閾值開關 電荷泵 。隨著亞微米和深亞微米工藝的應用,N+/PWLL結反向擊穿電壓和柵氧擊穿電壓都明顯降低,用于只讀存儲

2011-09-26 09:56:54 1537

1537

CMOS工藝發展到深亞微米階段,芯片的靜電放電(ESD)保護能力受到了更大的限制。因此,需要采取更加有效而且可靠的ESD保護措施。基于改進的SCR器件和STFOD結構,本文提出了一種新穎

2012-03-27 16:27:34 5303

5303 研究了深亞微米pMOS 器件的熱載流子注入(hot2carrier injection ,HCI) 和負偏壓溫度不穩定效應(negative bias temperature instability ,NBTI) 的耦合效應和物理機制.

2012-04-23 15:35:39 34

34 IC設計禾瑞亞積極將觸控IC進軍筆電市場,搶食Windows 8商機,看好筆記本電腦觸控商機,并預計第 4 季營運將較第 3 季持續成長,禾瑞亞強調,Windows 與Ultrabook若能順利獲得使用者采用與

2012-10-12 15:07:28 945

945

物聯網(IoT)應用興起,除為半導體廠開創新的市場商機外,亦帶來諸多積體電路(IC)設計新挑戰,特別是系統單芯片(SoC)功能整合度愈來愈高,已使IC設計業者面臨更嚴峻的數位和類比混合訊號(Mixed Signal)電路驗證(Verification)挑戰。

2014-08-18 09:51:25 1258

1258 微米聲納產品手冊,完整版,需要的可以下載。

2016-09-07 17:57:47 0

0 主要研究了自動微器件裝配系統的定標技術和操縱策略兩個問題。在加入了尺度因子優化步驟之后,一種基于Tsai兩步法的自定標方法實現了亞微米級的定標精度,并且獲得了更加可信的定標角度參數.

2017-09-20 16:10:17 4

4 BiCMOS[B]的 Twin-Well[1]與P-Well[2]或 N-Well[3] 的制造技術有很大的不同。主要是 CMOS 特征尺寸為亞微米級,使制造技術發生了重要的變化。

由于器件

2017-12-18 14:30:18 7662

7662 1 深亞微米 BiCMOS[B] 技術

器件進入深亞微米特征尺寸,為了抑制 MOS 穿通電流和減小短溝道效應,深亞微米制造工藝提出如下嚴格的要求:

(1)高質量柵氧化膜。柵氧化膜厚度

2018-03-16 10:29:54 8670

8670 明微電子總經理李照華發表了題為《驅動IC應對照明情景化的新挑戰》的主題演講。演講中,李照華代表明微電子表明對于傳統照明、智能照明以及情景照明的獨特認知,以及在這三個領域中今后的產品理念及具體行動。

2018-06-14 16:59:58 3561

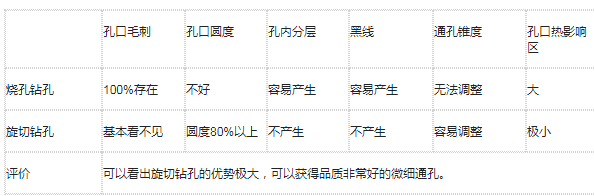

3561 對于35微米通孔,則有兩種情況,一種情況是調整一下外光路和激光參數或者采取激光焦點離焦的做法,讓激光對銅箔的有效光斑加大到35微米,采用和25微米通孔鉆孔一樣的燒孔方式加工,這樣可以快速燒出需要

2018-09-07 15:19:36 7706

7706

本次網絡研討會將介紹RF IC技術集成的現狀,重點討論非手機無線設備設計人員所面臨的挑戰,他們努力在更小的空間中實現更多的功能,有時候還要面臨必須采用可在多頻率下重復使用的寬帶收發器等棘手問題。

2019-07-15 06:03:00 2605

2605 與產業環境。隨著電子工業中深亞微米、超深亞微米技術的突破,以往電子工程師們擅長的電路設備正在一步步被IC設計所取代。

2019-05-01 20:49:00 4761

4761 KLA-Tencor光刻工藝控制解決方案將產量優化至0.13微米 SAN JOSE - KLA-Tencor公司推出了一款工藝模塊控制(PMC)解決方案芯片制造商實施和控制0.13微米及更小

2020-02-14 11:05:23 1983

1983 佳能提高了用于0.15微米IC的248納米掃描儀的吞吐量 SAN JOSE - 佳能美國公司的半導體設備部門今天宣布將推出一款新產品下周在加利福尼亞州圣克拉拉舉行的SPIE微光刻研討會上,用于

2020-02-03 14:01:39 2869

2869 瑞士NEUCHATEL - (ChipWire) - Xemics SA宣布其CooLIB 4.1低功耗單元庫現在支持臺灣半導體制造公司的0.18微米工藝。早期版本的CooLIB標準單元庫支持

2019-08-13 10:26:47 3313

3313 一家業界領先的半導體設備供應商,專業從事亞微米級的貼片設備制造及翻新。他們憑借柔性的多片貼裝技術成為該領域的佼佼者。

2020-05-10 10:30:08 2425

2425 荷蘭代爾夫特理工大學的科學家開發出了一種交錯背觸式(IBC)、銅-銦-硒化鎵(CIGS)太陽能電池,其亞微米厚度為673納米。

2020-06-17 14:35:11 2661

2661 此外,電裝還減少了用于電池電控單元(ECU)的IC和外圍部件的數量。該公司還研發了深亞微米工藝技術和專有的高擊穿電壓設備,可以將ECU的尺寸和成本降至最小。

2020-10-14 14:44:55 2113

2113 采用基于物理的指數MOSFET模型與低功耗傳輸域MOSFET模型,推導了新的超深亞微米無負載四管與六管SRAM存儲單元靜態噪聲容限的解析模型.對比分析了由溝道摻雜原子本征漲落引起的相鄰MOSFET的閾值電壓失配對無負載四管和六管SRAM單元靜態噪聲容限的影響。

2021-03-26 15:17:54 6

6 ADF7030-1:高性能、亞GHz無線電收發器IC產品手冊

2021-04-17 11:11:38 6

6 AN-306:同步系統海洋微米

2021-04-26 12:06:26 1

1 數字集成電路分析與設計:深亞微米工藝免費下載。

2021-05-12 14:52:40 180

180 東莞普萊信智能發布亞微米級固晶機DA403,貼裝精度達到0.3μm@3σ,采用高精度光學多次校準,適用于8英吋及以下晶圓級封裝,廣泛應用于硅光、光器件、晶圓級封裝等亞微米級封裝領域,該設備打破國際

2021-12-09 09:49:16 2501

2501 北京2022年12月15日 /美通社/ -- ?以下為來自21ic電子網的報道: 距離馬里亞納 X發布時隔僅一年的時間,OPPO就在今年未來科技大會上發布了其第二款自研芯片 -- 馬里亞納? Y

2022-12-16 21:07:22 2890

2890 新研發中心將基于麥吉爾大學授權的獨家技術專利組合進行研究,開發全球首個高效亞微米級別Nano LED,將下一代Nano LED技術商業化,應用到電視、手機、智慧手表、AR眼鏡等電子產品當中。

2023-03-15 11:13:47 803

803 像素中心之間的距離有幾個至十幾個微米不等。為了最大限度利用圖像信息來提高分辨率,有人提出了亞像素概念。意思是說,在兩個物理像素之間還有像素,稱之為亞像素,它完全是通過計算方法得出來的。

2023-07-31 15:53:26 6058

6058

在IC設計領域,大摩科技產業分析師顏志天認為,由于消費者需求依然疲弱,特別是聯詠預期第3季PC業務將明顯滑落,將導致下半年大型面板驅動IC(LDDI)跌價5%至10%。

2023-08-24 14:33:19 617

617 半導體芯科技編譯 隨著電子設備越來越小型化,對更小光學元件的需求帶來了生產方面的挑戰。 在大多數情況下,亞微米級光子器件的3D打印傳統方法成本非常高,而且在實驗室之外進行不切實際。 為了克服這一挑戰

2023-09-05 16:35:48 901

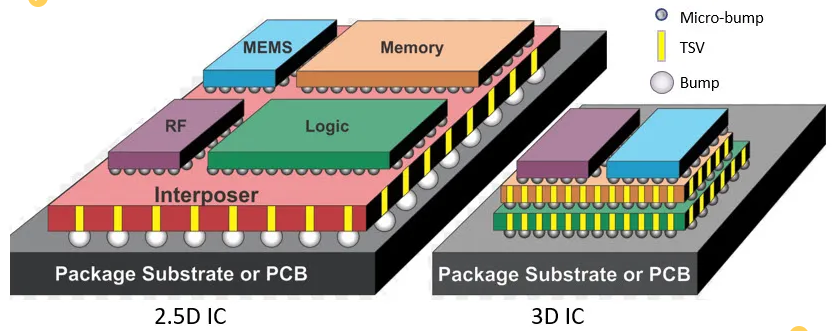

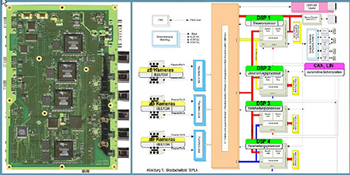

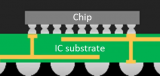

901 半導體封裝載板(ICS或IC載板)是整體晶圓封裝的基礎,在半導體晶圓的納米世界與印刷電路板PCB的微米世界之間,建立了強大的連接。IC載板包含多層板,而且中央通常有一個支撐核心,可保護及支持封裝內

2023-10-20 10:39:49 3776

3776

整個芯片都有一個溫度,所以分辨率是厘米大小的,用于觀察電路板上或外殼內部的散熱情況。然后是 IC 團隊,他們現在不再只有一張 IC。有一堆IC粘在一起。這個 IC 團隊以微米的分辨率來研究事物。

2023-11-24 16:10:34 1565

1565

據麥姆斯咨詢報道,近期,在美國加利福尼亞州舊金山舉行的國際電子器件會議(IEEE IEDM 2023)上,比利時納米電子學和數字技術研究與創新中心imec展示了一種“在300mm晶圓上使用標準后端制造工藝來實現以亞微米像素尺寸分離顏色”新方法。

2023-12-19 16:13:56 1733

1733

超微電極是一類一維尺寸在微米或亞微米級的一類電化學傳感器,具有尺寸小、傳質速率快、時-空分辨率高等多種優勢,因此被廣泛應用于電化學研究和傳感器開發等領域。

2024-04-15 11:18:17 2427

2427

據江陰發布的信息透露,此次發布的亞微米互聯技術依托本土設備技術實力,運用大視場光刻技術達到了0.8um/0.8um的線寬線距技術水準,所生產的硅穿孔轉接板產品達到3倍光罩尺寸,這標志著盛合晶微在先進封裝技術領域邁入亞微米時代

2024-05-20 11:47:57 1632

1632 的心臟注入了精準導航的靈魂,更以其卓越的技術特性,為機器人裝箱機系統的性能飛躍插上了翅膀。 www.abitions.com MT6501磁編碼IC,以其微米級的高精度位置檢測能力,仿佛擁有了一雙洞察秋毫的慧眼,能夠細膩捕捉電機旋轉的每一絲微妙變化,確

2024-08-13 17:52:15 941

941

光譜共焦位移傳感器通過亞微米級精度、強材質適應性、超高速采樣頻率及非接觸式測量技術,解決晶圓表面平整度檢測的行業痛點,為半導體制造企業提供高效、精準的檢測手段。檢

2025-04-21 08:18:31 784

784

電子發燒友App

電子發燒友App

評論