在亞微米以下的電路設計中,需要對電路進行全芯片的ESD保護結構的設計。如何使全芯片有效面積盡可能小、ESD性能可靠性滿足要求且不需要增加額外的工藝步驟成為全芯片設計者的主

2012-04-23 10:17:42 4709

4709

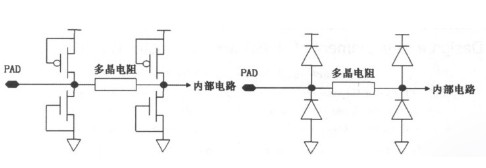

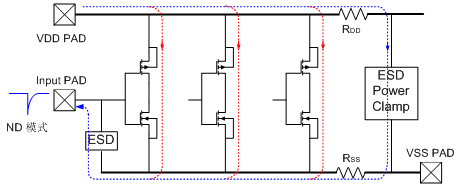

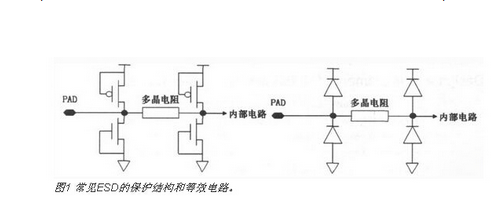

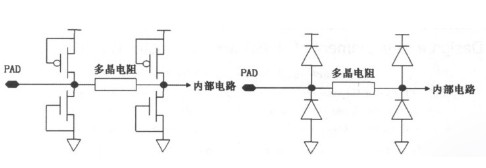

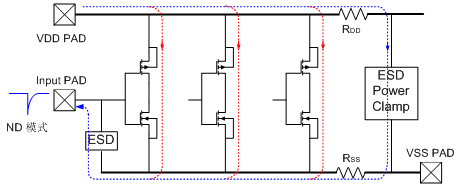

大部分的ESD電流來自電路外部,因此ESD保護電路一般設計在PAD旁,I/O電路內部。典型的I/O電路由輸出驅動和輸入接收器兩部分組成。ESD 通過PAD導入芯片內部,因此I/O里所有與PAD直接

2014-12-24 11:05:47 3291

3291

要求,重點討論了在I/O電路中ESD保護結構的設計要求。 1 引言 靜電放電會給電子器件帶來破壞性的后果,它是造成集成電路失效的主要原因之一。隨著集成電路工藝不斷發展,CMOS電路的特征尺寸不斷縮小,管子的柵氧厚度越來越薄,芯片的面積規模越來越大,MOS管能

2017-12-05 09:03:40 13455

13455

近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發展。目前,幾個研究組已利用標準

2021-07-29 07:00:00

, EOS等各項指標的要求。隨著IC先進制程技術的應用, 芯片功能的增多和尺寸的減小, 對于半導體廠和設計公司來說, 不斷面臨著產品對靜電保護ESD提出的越來越高的要求。這次授課老師為Bart Keppens

2015-04-22 22:19:54

。 IC制造商已經將ESD損傷確定為互補式金屬氧化物半導體(CMOS)元件現場可靠性的一項主要威脅,它可能損害品牌形象并妨礙市場接受新技術。為避免此情況,業界積極努力用后續新制程世代來最佳化整合ESD

2011-11-24 15:00:58

UM5051/5052的重要參數ESD保護器件的種類ESD應用舉例

2021-04-02 07:37:30

能夠承受ESD的沖擊,并繼續正常工作。ESD保護方法為了給電子系統提供ESD保護,可以從不同的角度來著手。一種方法是在半導體芯片內建ESD保護架構。不過,日趨縮小的CMOS芯片已經越來越不足以承受進行

2011-07-05 14:19:03

取舍,實際上會使系統整體性能在某種程度上受損。對于設計能夠同時符合更高數據率和更好ESD保護新需求的芯片的制造商來說,要實現這個目標極具挑戰性。ESD保護領域的變化 由于采用更小的制造幾何尺寸、片上保護

2011-01-27 10:35:10

水平,以便使那些采用了對ESD越來越敏感的IC的終端產品保持高可靠性。 ESD波形 以系統級的方法來定義典型的ESD事件所采用的最常見的波形,是以其亞納秒上升時間和高電流電平(參見圖1)為顯著特征

2010-08-18 19:44:07

徑,把異常電壓箝制在一個安全的水平,從而保護被保護IC或線路。ESD二極管憑借體積小、封裝多樣化、響應速度快(小于1ns)、電容值低、漏電流低(小于1uA)、超低箝位電壓、電壓值低等獨有優勢,廣泛應用

2018-10-17 16:04:52

如何正確保護IC?ESD傳遞模式有哪幾種?ESD保護和應用電路如何提高ESD保護?

2021-04-23 06:23:47

告訴《中國電子報》記者,據統計,超過60%的IC失效都源于ESD。 隨著超大規模集成電路工藝的高速發展,特征尺寸已經到深亞微米階段,大大提高了集成電路的性能及運算速度,但隨著器件尺寸的減小,對可靠性

2013-02-21 10:54:18

對電子器件來說,一次我們無法察覺的輕微靜電放電就可能對其造成嚴重的損傷。泰科電子瑞侃電路保護產品應用工程經理董告訴《中國電子報》記者,據統計,超過60%的IC失效都源于ESD。 隨著

2013-08-16 10:22:02

[table][tr][td]隨著現代社會的飛速發展,我們對電子設備的依靠與日俱增.現代電腦越來越多的采用低功率邏輯芯片,由于MOS的電介質擊穿和雙極反向結電流的限制,使這些邏輯芯片對ESD非常敏感

2013-11-20 15:43:19

`隨著半導體工藝尺寸從微米量級向納米量級縮小,靜電放電(ESD)對于半導體器件與系統的影響仍在持續。本書從全芯片ESD設計綜合的角度,對EOS、ESD以及Latchup進行了探討。針對ESD保護

2013-09-04 09:17:26

因為要求高集成度、快速度和小體積,如今的新興電子產品都使用基于先進深次微米制程的芯片。但制程越先進,芯片對 ESD 耐受度也就越差。當這些電子產品在實際環境下受到 ESD沖擊時,IC 內部更容易受到

2013-06-14 16:42:50

(螺絲起子)靠近有相反電勢的集成電路(IC)時,電荷“跨接”,引起靜電放電(ESD)。 ESD以極高的強度很迅速地發生,通常將產生足夠的熱量熔化半導體芯片的內部電路,在電子顯微鏡下外表象向外吹出的小?彈孔

2018-10-11 16:10:23

。不過,日趨縮小的CMOS芯片已經越來越不足以承受進行內部2 kV等級的ESD保護所需要的面積。安森美半導體標準產品部亞太區市場營銷副總裁麥滿權指出:真正有效的ESD保護是不能完全集成到CMOS芯片之中

2013-01-04 14:58:24

為了給電子系統提供ESD保護,可以從不同的角度來著手。一種方法是在半導體芯片內建ESD保護架構。不過,日趨縮小的CMOS芯片已經越來越不足以承受進行內部2KV等級的ESD保護所需要的面積。真正有效

2014-02-14 10:30:16

的安全保護傘的所有部分都應該“硬化”或者屏蔽攻擊,包括加密密鑰、驗證碼和固件。深聯華 基于硬件的安全性可在很小的空間內通過簡單且高成本效益的方式實現這一目標。幾乎沒有任何方法可以下載已鎖定在芯片中的秘密

2013-12-30 16:04:47

摘 要:EDA技術是現代電子設計技術的核心,它在現代集成電路設計中占據重要地位。隨著深亞微米與超深亞微米技術的迅速發展,FPGA設計越來越多地采用基于VHDL的設計方法及先進的EDA工具。本文詳細

2019-06-18 07:33:04

摘 要:EDA技術是現代電子設計技術的核心,它在現代集成電路設計中占據重要地位。隨著深亞微米與超深亞微米技術的迅速發展,FPGA設計越來越多地采用基于VHDL的設計方法及先進的EDA工具。本文詳細

2019-06-27 08:01:28

HDMI接收器和發射器的IC芯片全部采用深亞微米工藝制造。亞微米CMOS制程十分敏感,通常設有ESD保護限制(最高2kV),必須符合人體放電模式(HBM)標準。另外,LCD電視和機頂盒(STB)等

2013-11-21 09:57:59

和發射器IC芯片采用的是亞微米CMOS工藝制造而成的,而亞微米CMOS十分地敏感,為此需要借助ESD靜電保護器件和ESD靜電保護解決方案為其保駕護航。機頂盒STB、電視LCD等終端應用極其容易受到ESD

2020-12-31 15:57:17

已經過第三方實驗室驗證。 產品特點及其優點l CMOS霍爾IC技術l 強大的抗RF噪聲技術l 工作電壓1.8至6V,適用于電池供電的應用l 低至1.65V的工作電壓,全極霍爾開關微功耗l 高靈敏度可替換

2019-11-07 10:34:36

)的沖擊經由NFC天線對整個NFC的溝通功能所造成的錯誤動作。移動電話這些電子產品由于頻繁地與人體接觸,很容易受到靜電放電(ESD)的沖擊。此外,這些電子產品所采用的IC大多是使用最先進的半導體制程技術,所

2019-06-13 08:18:01

TVS的ESD保護原理ESD TVS器件采用的技術匯總

2021-04-02 06:19:56

的應用很容易受到靜電放電的影響。一些采用了深亞微米工藝和甚精細線寬布線的復雜半導體功能電路,對電路瞬變過程的影響更加敏感,將導致上述的問題更加激化。電路保護元件存在幾種技術,當選擇電路保護元件時,若

2019-07-29 17:50:09

的電路板空間以及被保護電路的電特性來決定。因為利用先進工藝技術**的IC電路里氧化層比較薄,柵極氧化層更易受到損害。而且一些采用深亞微米工藝和甚精細線寬布線的復雜半導體功能電路,對電路瞬變過程的影響更加

2018-11-20 14:09:05

如今的電子系統中越來越多地采用以CMOS工藝制造的低功率邏輯芯片。這些芯片如果遭遇足夠高的靜電放電(ESD)電壓,芯片內部的電介質上就會產生電弧,并在門氧化物層燒出顯微鏡可見的孔洞,造成芯片的永久

2013-12-27 16:21:39

...............................................................................1ESD (Electrostatic Discharge) Protection in CMOS Integrated Circuits ..........................1目錄

2011-02-24 09:55:18

)靠近有相反電勢的集成電路(IC)時,電荷“跨接”,引起靜電放電(ESD)。ESD以極高的強度很迅速地發生,通常將產生足夠的熱量熔化半導體芯片的內部電路,在電子顯微鏡下外表象向外吹出的小?彈孔,引起即時

2016-07-22 11:26:49

隨著半導體工藝的飛速發展和芯片工作頻率的提高,芯片的功耗迅速增加,而功耗增加又將導致芯片發熱量的增大和可靠性的下降。因此,功耗已經成為深亞微米集成電路設計中的一個重要考慮因素。為了使產品更具競爭力

2019-10-14 07:48:14

深亞微米的CMOS工藝制造高速分頻器。由于CMOS器件的價格低廉,因而高速CMOS分頻器有著廣闊的市場前景。那分頻電路由什么構成?你們知道2.4GHz動態CMOS分頻器設計難嗎?

2021-04-07 06:17:39

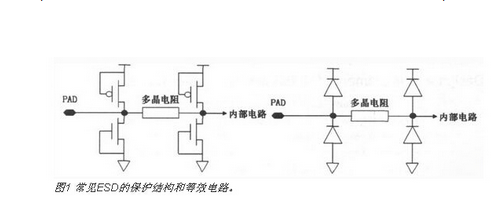

ESD(靜電放電)是CMOS電路中最為嚴重的失效機理之一,嚴重的會造成電路自我燒毀。論述了CMOS集成電路ESD保護的必要性,研究了在CMOS電路中ESD保護結構的設計原理,分析了該結構對版圖的相關要求,重點討論了在I/O電路中ESD保護結構的設計要求。

2021-04-02 06:35:57

,提高了芯片的運算速度。 但是,隨著工藝的進步和尺寸的減小,靜電釋放(ESD),Elecyro Static Discharge)問題變得日益嚴峻。據統計,在集成電路設計中大約40%的失效電路是ESD問題造成的。如何設計ESD保護電路?這個問題急需解決。

2019-08-07 06:24:17

關鍵芯片組外部ESD保護要求硅ESD保護技術與無源ESD保護技術比較消除信號完整性問題的PicoGuard XS ESD保護技術智能手機等便攜及消費產品電路保護及濾波應用示例

2021-04-09 06:55:32

首創。集成式固態ESD保護是專有的ADI技術,可實現非常高的ESD保護同時對MEMS開關RF性能影響最小。圖3顯示了采用SMD QFN封裝的ESD保護元件。其中,芯片安放在MEMS芯片上,通過焊線連接

2018-11-01 11:02:56

本文選擇了SoC芯片廣泛使用的深亞微米CMOS工藝,實現了一個10位的高速DAC。該DAC可作為SoC設計中的IP硬核,在多種不同應用領域的系統設計中實現復用。

2021-04-14 06:22:33

近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發展。目前,幾個研究組已利用標準

2019-08-22 06:24:40

和低功耗設計、設計驗證、芯片測試和可測性設計等主題,著重探討了深亞微米數字集成電路設計面臨的挑戰和啟示。本書可作為高等院校電子科學與技術(包括微電子與光電子)、電子與信息工程、計算機科學與技術、自動化等

2009-02-12 09:51:07

深亞微米CMOS工藝中,I/O單元的實現可以從235微米減小到160微米和138微米。 這種新的設計方法在ESD防護性能和效率上都很大程度提高,并且在實現防靜電保護避免IC損壞,進一步提高晶圓使用的效率方面發揮了積極作用。參考資料:防靜電資訊網

2012-12-11 13:39:47

新型互補電容耦合ESD保護電路的設計提出了一種改進型的基于亞微米工藝中ESD 保護電路, 它由互補式電容實現, 結構與工藝簡單。電路采用0.6μm1P2MCMOS 工藝進行了驗證, 結果表明

2009-12-23 16:33:58

。從成本效益比的角度來看,這已經被證明是件很難做到的事。從圖1可以看出,隨著制造技術轉向90nm以下,將ESD保護水平維持在2,000V的成本,已開始以指數級上升。因此,現在新的目標是降低芯片上

2019-05-22 05:01:12

我在LM386的技術文檔中看到了該芯片的內部電路圖,發現電路中有兩個二極管連接了VSS和VDD,應該是構成了ESD保護電路,請問這個保護電路是只對輸出引腳Vout進行保護,還是被所有引腳所共享,即

2024-09-30 06:22:18

IC。在一個新的模塊快速連接該器件和ESD測試開始獲得好的結果,因為SZESD9101成功保護了GPS通過所需的8kV存在等級。有了推薦的ESD保護器件、TLP的結果以及向上層管理報告8kV通過結果

2018-10-25 09:02:26

【作者】:張科營;郭紅霞;羅尹虹;何寶平;姚志斌;張鳳祁;王園明;【來源】:《原子能科學技術》2010年02期【摘要】:采用TCAD工藝模擬工具按照等比例縮小規則構建了從亞微米到超深亞微米級7種

2010-04-22 11:50:00

,不普通數字電路更容易遭到損壞,因為用于ESD保護的傳輸入保護結構會增加輸入泄露,因此不能使用。所有ESD敏感器件均采用保護性封裝。IC通常裝在導電泡沫中或者防靜電包裝套管中,而后將容器密封在一個靜電

2018-01-16 14:21:19

解讀ESD靜電抑制器 因為要求高集成度、快速度和小體積,如今的新興電子產品都使用基于先進深次微米制程的芯片。但制程越先進,芯片對 ESD 耐受度也就越差。當這些電子產品在實際環境下受到 ESD沖擊

2013-12-11 15:58:03

使用液晶電視等HDMI終端設備支持的音頻/視頻格式。 HDMI接收器和發射器的IC芯片全部采用深亞微米工藝制造。亞微米CMOS制程十分敏感,通常設有ESD保護限制(最高2kV),必須符合人體放電模式

2019-06-17 05:00:06

摩爾定律對先進CMOS IC的ESD保護的影響 持續不斷的特征尺寸小型化趨勢,已經使半導體制造商能夠在過去幾十年中通過把幾十億三極管集成到單一芯片之中來提高芯片性能、降低功耗及驅動成本的下降。盡管

2018-12-05 10:39:44

隨著現代社會的飛速發展,我們對電子設備的依賴與日俱增.現代電腦越來越多的采用低功率邏輯芯片,由于MOS的電介質擊穿和雙極反向結電流的限制,使這些邏輯芯片對ESD非常敏感。大多數USB集成電路都是

2019-08-02 17:43:22

本文介紹了以超深亞微米技術為支撐的 SOC 的定義以及芯片設計方法,并闡述了軟硬件協同設計理論、IP 核生成及復用技術、超深亞微米IC 設計面對的難題以及SOC 測試與驗證技術。

2009-06-19 09:28:12 35

35

隨著工藝的發展,器件閾值電壓的降低,導致靜態功耗呈指數形式增長。進入深亞微

米工藝后,靜態功耗開始和動態功耗相抗衡,已成為低功耗設計一個不可忽視的因素

2009-09-15 10:18:10 18

18 隨著工藝的發展,器件閾值電壓的降低,導致靜態功耗呈指數形式增長。進入深亞微米工藝后,靜態功耗開始和動態功耗相抗衡,已成為低功耗設計一個不可忽視的因素。針對近

2009-09-15 10:18:10 26

26 CMOS工藝中GG2NMOS結構ESD保護電路設計:采用GG2NMOS 結構的ESD 保護電路的工作原理和對其進行的ESD 實驗,提出了一種保護電路的柵耦合技術方案,并達到了預期效果. 通過實驗可以看出其性

2009-11-20 14:48:43 41

41 本文研究了在CMOS 工藝中I/O 電路的 ESD 保護結構設計以及相關版圖的要求,其中重點討論了PAD 到VSS 電流通路的建立。關鍵詞:ESD 保護電路,ESD 設計窗口,ESD 電流通路Constru

2009-12-14 10:45:54 55

55 本文采用 MEDICI 作為集成電路ESD 保護常用器件—柵極接地N 型MOS 管(GGNMOS)ESD 性能分析的仿真工具,綜合分析了各種對GGNMOS 的ESD 性能有影響的因素,如襯底摻雜、柵長、接觸

2009-12-14 10:59:02 22

22 本文通過對傳統大規模集成電路設計流程的優化,得到了更適合于深亞微米工藝集成電路的后端設計流程,詳細介紹了包括初步綜合、自定義負載線的生成、版圖規劃、時鐘樹綜合

2009-12-14 11:03:09 15

15 和艦科技自主創新研發的0.16 微米硅片制造工藝技術在原有比較成熟的0.18 微米工藝技術基礎上,將半導體器件及相關繞線尺寸進行10%微縮(實際尺寸為0.162 微米),大大降低了芯

2009-12-14 11:23:36 25

25 基于深亞微米MOS 器件溝道的熱噪聲淺析曾獻芳摘要: 隨著 MOS 器件工藝尺寸的不斷減小,其不斷增高的單位增益截止頻率足以滿足射頻/模擬電路的工作要求。然而,隨著溝

2009-12-15 14:31:04 10

10 超深亞微米IC設計中的天線效應李蜀霞 劉輝華 趙建明 何春(電子科技大學電子電子科學技術研究院 成都 610054)【摘要】本文主要分析了超深亞微米集成電路設計中天線效應

2009-12-19 14:54:53 45

45 摘要:就超深亞微米集成電路中高K柵介質、金屬柵、cU/低K互連等相關可靠性熱點問題展開討論.針對超深亞微米集成 電路可靠性問題.提出可靠性設計、生產過程的質量控制、可

2010-04-27 14:13:33 19

19 摘要:增強測試質量和抑制測試代價是超深亞微米集成電路測試及可測性設計領域的兩個研究主題。本文介紹了一個基于Mentor公司可測性設計工具的面向多種故障模型的超深亞微

2010-06-07 11:01:17 10

10 分析了在超深亞微米階段,串擾對高性能芯片設計的影響,介紹了消除串擾影響的方法。 關鍵詞:串擾,布線,關鍵路徑,

2009-05-05 20:59:16 1434

1434

一種全新的深亞微米IC設計方法

本文分析了傳統IC設計流程存在的一些缺陷,并且提出了一種基于Logical Effort理論的全新IC設計方法。

眾所周知,傳統的IC設計流

2009-12-27 13:28:50 896

896

TSMC推出最新深亞微米互通式EDA格式

TSMC 7日宣布針對65納米、40納米及28納米工藝推出已統合且可交互操作的多項電子設計自動化(Electronic Design Automatio

2010-04-09 10:36:49 939

939 新型深亞微米電流靈敏放大器技術設計

隨著便攜式電子設備(PDA、射頻卡、GPS等)的廣泛應用,半導體存儲器得到了長足的發展。半導體存儲器的性能

2010-04-27 17:37:46 873

873

目前幾乎所有的芯片組都有片上ESD保護。ESD電路放在芯片的外圍和鄰近I/O焊墊處,它用于在晶圓制造和后端裝配流程中保護芯片組。在這些環境中,ESD可通過設備或工廠的生產線工作人員引入到芯片組上

2011-02-18 10:29:07 1260

1260

模擬/混合信號Ic設計一直是困擾很多中國Ic設計工程師的難題。與數字電路設計相比,模擬/混合電路設計要求更為嚴苛,而且需要嚴格的環境控制工藝。而對于深亞微米級的SOC設計還必

2011-03-31 16:16:10 0

0 下一代的實體設計系統IC Compiler,為Synopsys Galaxy Design Platform 2005的核心,其設計概念就在解決這些浮現的挑戰,提供從RTL到芯片的一貫解決方案

2011-04-19 11:14:51 1312

1312 研究了深亞微米pMOS 器件的熱載流子注入(hot2carrier injection ,HCI) 和負偏壓溫度不穩定效應(negative bias temperature instability ,NBTI) 的耦合效應和物理機制.

2012-04-23 15:35:39 34

34 近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發展。目前,幾個研究組已利

2012-05-21 10:06:19 2373

2373

BiCMOS[B]的 Twin-Well[1]與P-Well[2]或 N-Well[3] 的制造技術有很大的不同。主要是 CMOS 特征尺寸為亞微米級,使制造技術發生了重要的變化。

由于器件

2017-12-18 14:30:18 7653

7653 1 深亞微米 BiCMOS[B] 技術

器件進入深亞微米特征尺寸,為了抑制 MOS 穿通電流和減小短溝道效應,深亞微米制造工藝提出如下嚴格的要求:

(1)高質量柵氧化膜。柵氧化膜厚度

2018-03-16 10:29:54 8670

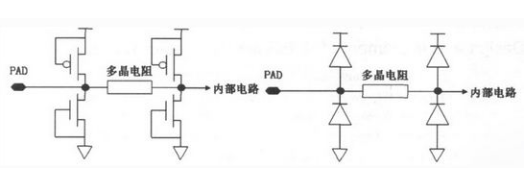

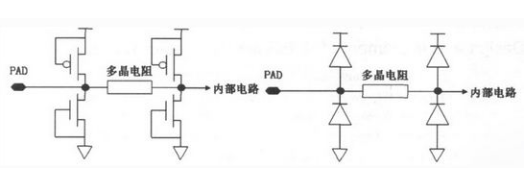

8670 ESD保護電路的設計目的就是要避免工作電路成為ESD的放電通路而遭到損害,保證在任意兩芯片引腳之間發生的ESD,都有適合的低阻旁路將ESD電流引入電源線。這個低阻旁路不但要能吸收ESD電流,還要能箝位工作電路的電壓,防止工作電路由于電壓過載而受損。

2019-03-04 14:24:01 5070

5070

ESD保護電路的設計目的就是要避免工作電路成為ESD的放電通路而遭到損害,保證在任意兩芯片引腳之間發生的ESD,都有適合的低阻旁路將ESD電流引入電源線。這個低阻旁路不但要能吸收ESD電流,還要能箝位工作電路的電壓,防止工作電路由于電壓過載而受損。

2019-04-08 15:26:11 2997

2997

隨著CMOS集成電路產業的高速發展,越來越多的CMOS芯片應用在各種電子產品中,但在電子產品系統的設計過程中,隨著CMOS工藝尺寸越求越小,單位面積上集成的晶體管越來越多,極大地降低了芯片的成本

2020-12-30 10:28:00 2

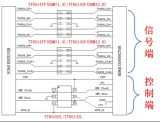

2 ESD保護設計隨著CMOS工藝的演進而越來越困難,迄今已有六百多件ESD相關的美國專利。而且,ESD更應當從芯片全局考慮,而不只是Input PAD,Output PAD,或Power PAD的問題。

2021-03-17 22:28:55 25

25 采用基于物理的指數MOSFET模型與低功耗傳輸域MOSFET模型,推導了新的超深亞微米無負載四管與六管SRAM存儲單元靜態噪聲容限的解析模型.對比分析了由溝道摻雜原子本征漲落引起的相鄰MOSFET的閾值電壓失配對無負載四管和六管SRAM單元靜態噪聲容限的影響。

2021-03-26 15:17:54 6

6 數字集成電路分析與設計:深亞微米工藝免費下載。

2021-05-12 14:52:40 180

180 電子發燒友網站提供《ESD保護芯片CH412技術手冊.pdf》資料免費下載

2022-09-09 11:29:03 3

3 點擊上方“藍字”關注我們!IC片上保護設計對EOS的影響全面的方法可以減少與EOS相關的故障通常理解的是,芯片上ESD保護是必不可少的,以滿足人體模型(HBM)和充電裝置模型產品合格(CDM)ESD

2021-12-31 16:08:02 3499

3499

靜電放電(ESD)是電子設備中一種常見的危害,它可能導致集成電路(IC)的損壞。對于CMOS IC來說,經受過嚴重ESD電擊的可靠性會降低。

2023-12-15 15:32:09 1548

1548 據江陰發布的信息透露,此次發布的亞微米互聯技術依托本土設備技術實力,運用大視場光刻技術達到了0.8um/0.8um的線寬線距技術水準,所生產的硅穿孔轉接板產品達到3倍光罩尺寸,這標志著盛合晶微在先進封裝技術領域邁入亞微米時代

2024-05-20 11:47:57 1632

1632 據統計,靜電放電(Electro-Static Discharge, ESD)造成的芯片失效占到集成電路產品失效總數的38%。完好的全芯片ESD防護設計,一方面取決于滿足ESD設計窗口要求的優質ESD器件結構,另一方面全芯片ESD防護網絡的考量也格外重要。

2024-06-22 00:31:59 2157

2157

如下圖1所示為HDMI接口與ESD保護芯片連接示意圖,其中HDMI CONNECTOR指的是HDMI接口,HDMI RECEVIER指的是各種器件所配置的HDMI連接端口,ESD保護芯片主要

2024-12-29 13:56:10 2044

2044

電子發燒友App

電子發燒友App

評論