1 亞微米 BiCMOS[B] 技術的主要特點

BiCMOS[B]的 Twin-Well[1]與P-Well[2]或 N-Well[3] 的制造技術有很大的不同。主要是 CMOS 特征尺寸為亞微米級,使制造技術發生了重要的變化。

由于器件尺寸縮小,柵氧化膜的厚度也要求按比例減薄,這主要是為了防止短溝效應。薄柵氧化膜要達到其高質量的指標:低的缺陷密度,好的抗雜質擴散的勢壘特性,具有低的界面態密度和固定電荷的Si/SiO2 界面,在熱載流子應力和輻射條件下的穩定性以及低的熱預算(溫度時間乘積量)工藝。

在亞微米制造技術中,P 溝道區的注入一般需要作兩次注入,其中一次用于調整閾值電壓,另一次用于抑制穿通效應。抑制穿通的注入通常是高能量,較高劑量,注入峰值較深(延伸至源-漏耗盡區附近);而調節閾值電壓注入一般能量較低,注入峰值位于表面附近。因此柵下的雜質分布不僅決定于襯底摻雜,而且還決定于注入雜質,因而溝道區雜質呈非均勻分布。

在亞微米技術中,為了抑制 CMOS 穿通電流和減小短溝道效應,工藝要求更淺的源漏結深,達到淺結。工藝對 PN 結有很高的要求:高的表面濃度,淺的結深,低接觸薄層電阻以及很小的結漏電流。

在淺 的 N+P 結中,可用 75As+ 注入來實現。由于砷離子相當重,因而可使被注入區硅表面變為無定形,此時,只要在 900 ℃ 較低溫度下退火,即可由固相外延形成再結晶,相應擴散卻相當小,因此可實現 N+P 淺結。還需要 P+N 淺結。采用 49BF2+ 注入, 由于 49BF2+ 質量大,并能將結深降到單用 11B+ 時的四分之一,來制作 P+N 淺結。

在淺結歐姆接觸中,Al-Si 互擴散產生的結漏電,穿通等是影響器件熱穩定性,甚至造成器件失效的一個嚴重問題,為此采用在 Al 層和 Si 之間加一擴散阻擋層的方法,通常選用 TiN 膜,這是因為 TiN 熱穩定性好。

輕摻雜漏 LDD 結構主要應用于亞微米或深亞微米 MOS 器件中,以提高源漏穿通電壓和減少高電場引入的熱載流子注入問題。具有代表性的結構和技術有利用 TEOS 側墻制作對稱 LDD 結構,它的形成方法就是在柵和源漏的重摻雜區之間引入一個輕摻雜區。這樣,N+ 或 P+ 區注入雜質不會在柵下面發生橫向擴散,但會在側墻下面擴散。

本文提出, 為了直觀顯示出雙極型與 CMOS 器件兼容集成的亞微米 BiCMOS[B] 結構,應用芯片結構技術[4-6],可以得到芯片剖面結構,并利用計算機和它所提供的軟件,描繪出制程中芯片表面﹑內部器件以及互連的形成過程和結構的變化的示意圖。

2 亞微米芯片剖面結構

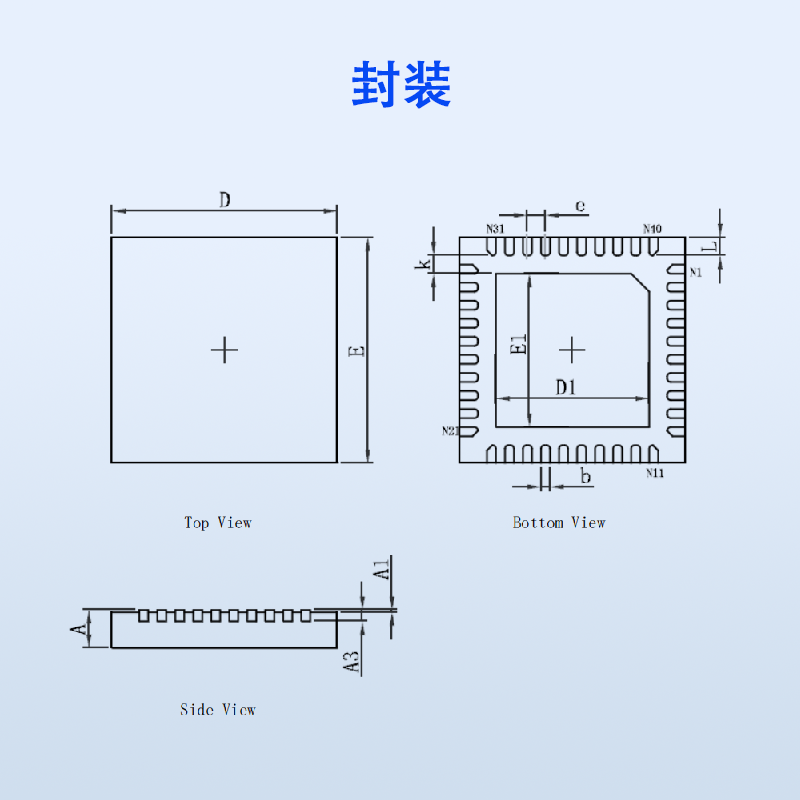

應用芯片結構技術[4-6],使用計算機和它所提供的軟件,可以得到亞微米 BiCMOS[B] 芯片典型剖面結構。首先由設計人員在電路中找出各種典型元器件: NMOS, PMOS, NPN (縱向)以及 PNP(橫向)。然后由制造人員對這些元器件進行剖面結構設計,選取剖面結構各層統一適當的尺寸和不同的標識,表示制程中各工藝完成后的層次,設計得到可以互相拼接得很好的各元器件結構(或在元器件結構庫中選取),分別如圖 1[A]﹑[B]﹑[C] 以及 [D] 等所示(不要把它們看作連接在一起)。最后把各元器件結構依一定方式排列并拼接起來,構成電路芯片剖面結構,圖 1 為其示意圖。

圖 1 芯片剖面結構是以雙極型制程及其所制得的元器件為基礎,引入兼容的 CMOS 器件工藝,最終在同一硅襯底上形成 IC 中主要器件。而圖 1-B的芯片剖面結構中,除了圖 1-A 的四種器件外,還有其它無源器件:如位于場區上的雙層 Poly 電容和 Poly 電阻等;或襯底 MOS 電容(或雙極型電容)和 N-Well 電阻(或基區電阻);或采用摻雜 N+Poly 與硅表面直接相接形成淺發射區的結構來代替圖中 NPN 結構,來提高電路速度;或它們之間的不同結合,就形成多種不同的復雜的 BiCMOS[B] 結構,可選用其中一種與設計電路直接相聯系的結構。限有篇幅,本文僅介紹圖 1-A 技術。

3 亞微米芯片工藝技術

設計電路 CMOS 采用 0.8μm/雙極型為2~ 3μm 設計規則,使用1~2μm 薄外延的亞微米BiCMOS[B] 制造技術。該電路主要元器件﹑制造技術以及主要參數如表1所示。它以雙極型制程及其所制得的元器件為基礎,引入兼容的 CMOS 器件工藝,并對其中芯片結構和制造工藝進行改變,以制得 CMOS 器件的相容技術,最終在同一硅襯底上形成如表 1 所示的 IC 中主要元器件,并使之互連,實現所設計的電路。該電路或各層版圖己變換為縮小的各層平面和剖面結構圖形的 IC 芯片。如果所得到的工藝與電學參數都適合于所設計電路的要求, 則芯片功能和電氣性能都能達到設計指標。

為實現亞微米 BiCMOS[B] 技術,對雙極型制造工藝作如下的改變。

(1)在自對準形成 BLN+ 埋層﹑BLP+ 埋層和 P型薄層外延后,分別引入 11B+﹑31P+ 注入并推進,生成與埋層相接的 Twin-Well,同時形成雙極型隔離;引入場區注入,硅局部氧化,形成 CMOS 隔離;

(2)在基區推進后,引入溝道防穿通注入和閾值調節注入,柵氧化以及 Poly 淀積并摻雜,LDD 注入,TEOS 淀積,刻蝕形成亞微米 CMOS 硅柵結構及其側墻;

(3)75As+ 或 49BF2+ 注入,生成 N+ 或 P+ 區為雙極型的 E/C 摻雜區和 Pb 基區接觸同時,引入形成源漏摻雜區。上述引入這些基本工藝,使雙極型芯片結構和制程都發生了明顯的變化。工藝完成后,以制得 NMOS[A] 與 PMOS[B] 和縱向 NPN[C] 與橫向PNP,并用亞微米 BiCMOS[B] 來表示。

表 1 中的參數: P- 型外延層厚度為 TP-EPI,深磷區(DN)結深/薄層電阻為 XjDN / RSDNN+ 結深/ 薄層電阻為 XjN+ / RSN+,P+ 結深/薄層電阻為 XjP+ / RSP+,基區結深/薄層電阻為 XjPb / RSPb,埋層結深/薄層電阻為 XjBL / RSBL,其它參數符號與通常表示相同。

根據電路電氣特性指標,確定用于芯片制造的基本參數,如表 1 所示。為此,芯片制程工藝中,一方面要確保工藝參數,電學參數都達到規范值,另一方面批量生產中要確保電路具有高成品率,高性能以及高可靠性。根據電路電氣特性的指標,提出對各種參數:(1)工藝參數如各種摻雜濃度及其分布﹑結深﹑柵氧化層厚度﹑基區寬度等;(2)電學參數如各種薄層電阻﹑源漏擊穿電壓﹑閾值電壓﹑CB/CE 擊穿電壓﹑放大系數β等以及(3)硅襯底電阻率/外延層厚度及其電阻率等要求,從而制定出各工序具體工藝條件,以保證所要求的各種參數都達到規范值。

4 亞微米芯片工藝制程

圖 1 所示的芯片結構采用確定的制造技術來實現。它是由工藝規范確定的各個基本工序﹑相互關聯以及將其按一定順序組合構成。為實現此制程,上面(1)~(3)引入這些基本工藝,不僅增加了制造工藝,技術難度增大,使芯片結構發生了明顯的變化,而且改變了雙極型制程,從而實現了亞微米BiCMOS[B] 制程。

為實現此制程,需要作多次氧化﹑光刻﹑雜質擴散﹑離子注入﹑薄膜淀積以及濺射金屬等構成基本工序。這些工序提供了形成電路中各個元器件 NMOS,PMOS,NPN(縱向),PNP(橫向)等所需要的精確控制的硅中的雜質層(BLN+,BLP+,P-EPI,DN,N-Well,P-Well,PF,NF,Pb,N+SN-,P+SP-, N+Poly等),也提供了這些電路元器件連接起來形成集成電路所需要的介質層(F-Ox,G-Ox, Poly-Ox,BPSG / LTO,TEOS等)和金屬層(AlCu)。這些都必須按給定的順序進行的制造步驟構成了制程。

應用計算機,依據芯片制造工藝中的各個工序的先后次序,把各個工序互相連接起來,可以得到芯片制程,。該制程由各工序所組成,而工序則由各工步所組成來實現。根據設計電路的電氣特性要求,選擇工藝規范號和工藝序號,以便得到所需要的工藝和電學參數。

應用芯片結構技術[4],可以得到圖 1 芯片剖面結構,使用計算機和它所提供的軟件,描繪出芯片制程中各個工序剖面結構,根據各個工序的先后次序互相連接起來,得到如圖2所示的亞微米 BiCMOS[B] 制程剖面結構示意圖。該圖直觀地顯示出制程中芯片表面﹑內部元器件以及互連的形成過程和結構的變化。

(1)襯底材料 P-Si <100>,基底氧化(Pad-Ox), Si3N4 淀積(1),光刻 BLN+ 埋層, 刻蝕 Si3N4 ,腐蝕 SiO2,BLN+ 區氧化(BLN+-Ox), 121Sb+ 注入,如圖 2-1 所示。

(2)注入退火,BLN+ 區推進/氧化(BLN+ -Ox),二層(SiON/Si3N4)腐蝕,BLP+ 埋層 11B+ 注入,如圖 2-2 所示。

(3)注入退火,BLP+ 埋層推進, 腐蝕凈 SiO2 , P- 型薄層外延(P-EPI),基底氧化(Pad-Ox),Si3N4(2)淀積,光刻 N-Well, 刻蝕 Si3N4,31P+ 注入,如圖 2-3 所示。

(4)注入退火,N-Well 推進/氧化(N-Well-Ox),二層(SiON/Si3N4)腐蝕,P-Well 11B+ 注入,如圖 2-4 所示。

(5)注入退火,P/N-Well 推進/氧化,光刻DN區,腐蝕 SiO2 , DN 區氧化(DN-Ox),31P+ 注入,DN 區推進/氧化,如圖2-5 所示。

(6)腐蝕凈 SiO2, 出現 P-Well 平面高于 N-Well,基底氧化(Pad-Ox),Poly /Si3N4(3)淀積,光刻源區,刻蝕 Si3N4 /Poly,如圖 2-6 所示。

(7)光刻 P 場區,APT.(防穿通)11B+ 深注入,11B+ 淺注入,如圖 2-7 所示。

(8)光刻 N 場區,75As+ 注入,如圖 2-8 所示。

(9)注入退火,場區氧化(F-Ox),形成四層(SiON / Si3N4 / Poly / SiO2)結構,如圖 2-9 所示。

(10)四層(SiON / Si3N4 / Poly / SiO2)腐蝕,預柵氧化(Pre-Gox), 光刻 Pb 基區,11B+ 注入,如圖 2-10 所示。

(11)注入退火,Pb 基區推進,光刻 N 溝道區,49BF2+ 注入,如圖 2-11 所示。

(12)光刻 P 溝道區,APT.31P+ 深注入,49BF2+ 淺注入,如圖 2-12 所示。

(13)腐蝕預柵氧化層,注入退火,柵氧化(G-Ox),Poly 淀積并摻雜,光刻 Poly,刻蝕 Poly,此時 N-Well 與 Poly 之間出現防穿通區,如圖 2-13 所示。

(14)Poly 氧化(Poly-Ox),光刻 NLDD 區,31P+ 注入(Poly 注入未標出),如圖 2-14 所示。

(15)光刻 PLDD 區,49BF2+ 注入(Poly 注入未標出),如圖 2-15 所示。

(16)注入退火,形成 SN-,SP- 區,TEOS 淀積/致密,刻蝕形成 TEOS 側墻,源漏氧化(S /D-Ox),如圖 2-16 所示。

(17)光刻 N+ 區,75As+ 注入(Poly 注入未標出),如圖 2-17 所示。

(18)光刻 P+ 區,49BF2+ 注入(Poly 注入未標出),如圖 2-18 所示。

(19)注入退火,形成 N+SN-,P+SP- 區(圖中未標出 SN-,SP-),LTO/BPSG 淀積/致密,光刻接觸孔,刻蝕 BPSG / LTO / SiO2,如圖 2-19 所示。

(20)濺射 Ti/TiN, RTA N2 退火,濺射金屬(Metal),光刻金屬, 刻蝕 TiN / AlCu / TiN / Ti , 如圖 2-20 所示。

從亞微米 BiCMOS[B] 制程和剖面結構可以看出,阱區是由向 P 型襯底生長出 P- 型外延層中擴散 N﹑ P 型雜質而制成。阱界面場區氧化表面具有臺階結構。PMOS﹑縱向 NPN﹑橫向 PNP 都是在 N-Well 中制作, NMOS 是在 P-Well 中形成。該制程的主要特點如下。

(1)器件隔離是由硅局部氧化(LOCOS)和對通隔離(P-Well / BLP+)構成。

(2)形成雙極型器件的基底與 PMOS 的 N-Well深度和濃度相同。

(3)PNP 的發射區/集電區和基區(Pb)接觸的P+ 摻雜同時,在 N-Well 中形成源區和漏區,以制得PMOS。

(4)NPN 的發射區/集電區和基區接觸的 N+摻雜同時,在 P-Well 中形成源區和漏區,以制得 NMOS。

(5)為了獲得大電流下的低飽和壓降,采用高濃度的集電極深磷擴散,形成與 BLN+ 埋層相接的深磷區(DN)。

CMOS 的 P-Well深度是十分重要,必須達到BLP+埋層,以便削弱 CMOS 中的“閂鎖效應”,并形成雙極的對通隔離。阱的深度與 NMOS 特性(UTN,體效應因子以及 BUDS 等)密切相關。因此,必須選擇合適的阱深和濃度,以便達到電路電氣特性的要求。

由于雙極和 CMOS 技術的要求相沖突,亞微米 BiCMOS[B] 阱分布的最佳化是一個多方面的問題。因為 N-Well 提供雙極 NPN 和 PMOS 管的基礎,大多數臨界工藝折衷涉及 N-Well 分布。但是,關鍵要點如隔離﹑二極管電容以及反摻雜 P-Well 中遷移率降低亦必須都要考慮,特別在 CMOS 加強電路中,NMOS 性能起支配作用。

5 結語

除去芯片表面鈍化層光刻外,制程中使用了 16次掩模,各層平面結構與橫向尺寸都由各次光刻所確定。制程完成后確定了芯片各層平面結構與橫向尺寸和剖面結構與縱向尺寸,并精確控制了硅中的雜質濃度及其分布和結深,從而確定了電路功能和電氣性能。芯片結構及其尺寸和硅中雜質濃度及其結深是制程的關鍵。它們不僅與雙極型下列參數:

(1)埋層結深及其薄層電阻;

(2)P 型外延層電阻率及其厚度;

(3)基區寬度及其薄層電阻;

(4)發射區結深及其薄層電阻;

(5)與埋層相接的深磷區結深及其薄層電阻;

(6)器件 fT﹑β﹑BUcEo﹑以及 BUcBo 等。

而且,與 CMOS下列參數:

(1)P 型外延層電阻率;

(2)阱深度及其薄層電阻;

(3)各介質層和柵氧化層厚度;

(4)有效溝道長度;

(5)源漏結深度及其薄層電阻;

(6)器件的閾值電壓,源漏擊穿電壓,以及跨導等有關,如表 1 所示。

此外,雙極型與 CMOS 這些參數之間必須進行折衷并優化,以達到互相匹配。制程完成后,先測試晶圓 PCM(表 1 中工藝和電學參數)數據。達到規范值后,才能測試芯片電氣特性。

發布評論請先 登錄

芯片失效故障定位技術中的EMMI和OBIRCH是什么?

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

基于光譜橢偏術的多層結構介質衍射光柵表征研究

北斗雙頻芯片AR9880B

3D 共聚焦顯微鏡 | 芯片制造光刻工藝的表征應用

T0727J5012AHF超低剖面0805阻抗變壓器50?至12.5?

從微米到納米,銅-銅混合鍵合重塑3D封裝技術格局

從毫米到微米:MCX插頭尺寸的技術突破之路

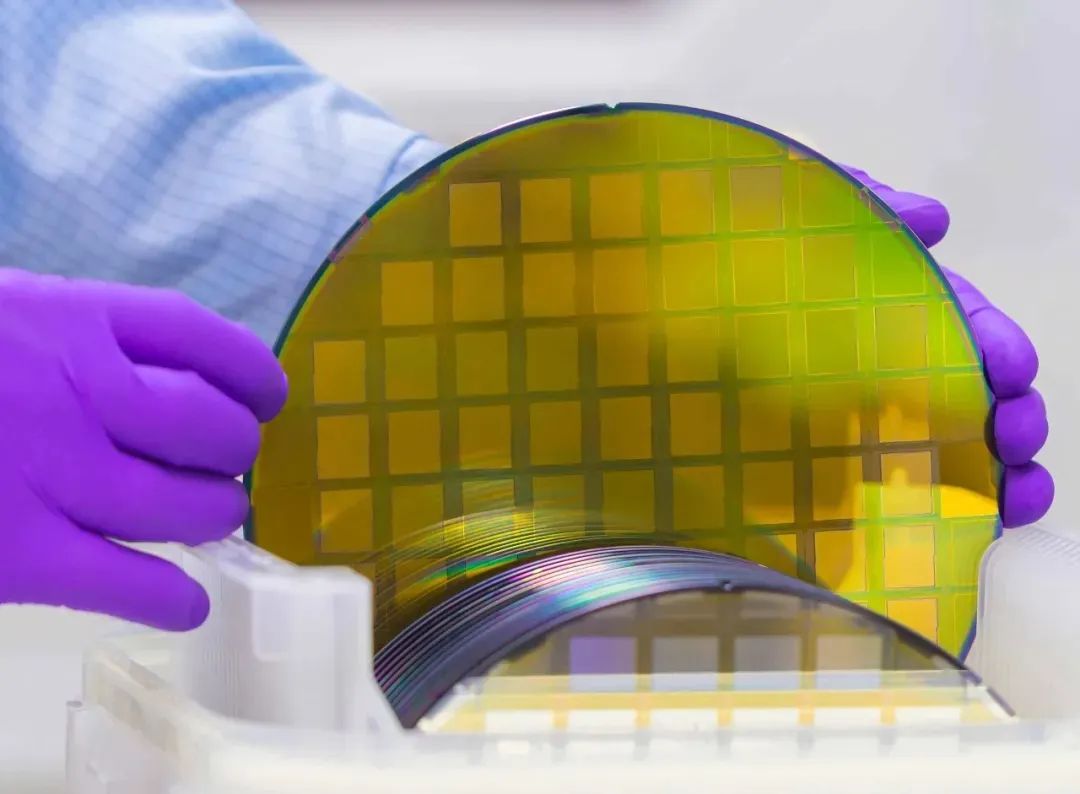

簡單認識晶圓減薄技術

飛秒激光技術在微流控芯片中的應用

深視智能SCI系列光譜共焦位移傳感器以亞微米精度測量晶圓平整度

亞微米BiCMOS[B]芯片及其剖面結構與制程技術分享

亞微米BiCMOS[B]芯片及其剖面結構與制程技術分享

評論