1、在做 PCB 設(shè)計(jì)時(shí),為了滿足某一組所有信號線的總長度滿足在一個(gè)公差范圍內(nèi),通常要使用蛇形走線將總長度較短的信號線繞到與組內(nèi)最長的信號線長度公差范圍內(nèi),這個(gè)用蛇形走線繞長信號線的處理過程,就是

2023-07-27 07:40:03 5391

5391

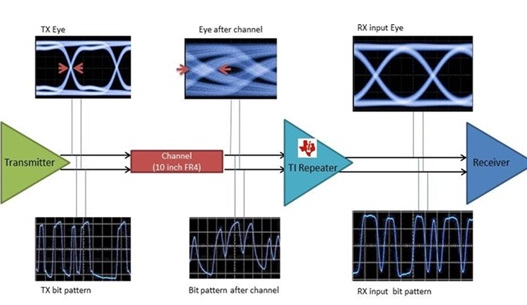

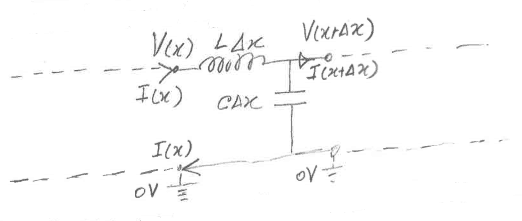

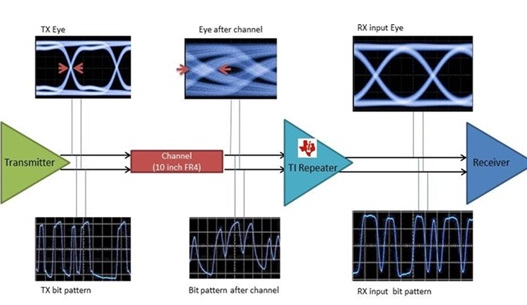

T.K. Chin在他的博客文章《差分對:你真正需要了解的內(nèi)容》里談?wù)摿藢τ?b class="flag-6" style="color: red">差分對的要求。在現(xiàn)實(shí)應(yīng)用中,我們用印刷電路板(PCB)內(nèi)的銅走線或線纜組裝件內(nèi)的銅質(zhì)導(dǎo)線來實(shí)現(xiàn)差分對。較長的PCB走線或

2018-05-29 09:27:02 14782

14782

PCB layout需要豐富的經(jīng)驗(yàn)和扎實(shí)的理論基礎(chǔ)支持,還要多踩幾個(gè)坑,多做幾個(gè)仿真加深對走線的理解,才能形成閉環(huán)的走線設(shè)計(jì)。

2022-07-19 15:10:41 4372

4372 很多人對于PCB走線的參考平面感到迷惑,經(jīng)常有人問:對于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?

2022-09-09 13:05:47 5352

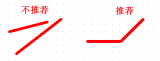

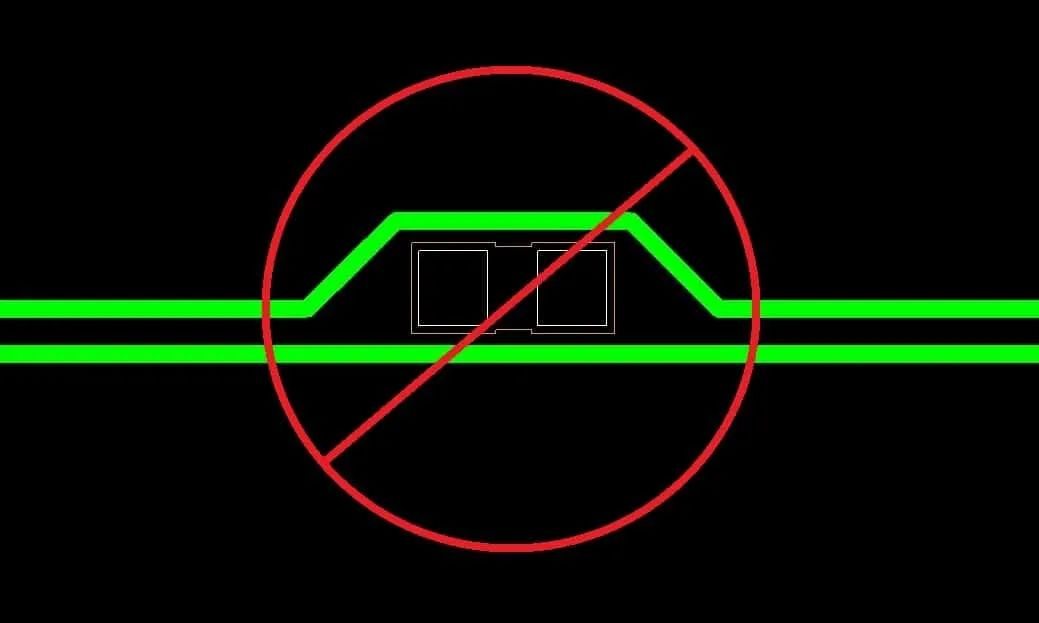

5352 是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。1. 直角走線 直角走線一般是PCB布線中要求盡量

2015-01-12 14:53:57

作為專業(yè)從事PCB快速打樣業(yè)務(wù)的深圳捷多邦科技有限公司的資深工程師們從直角走線,差分走線,蛇形線三個(gè)方面闡述了PCB LAYOUT的走線: 一、直角走線 (三個(gè)方面) 直角走線的對信號

2018-09-13 15:50:25

下面從直角走線、差分走線、蛇形線三個(gè)方面來闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。 1. 直角走線 直角走線一般是PCB布線中要求盡量

2019-06-10 10:11:23

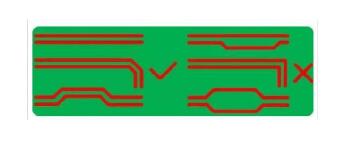

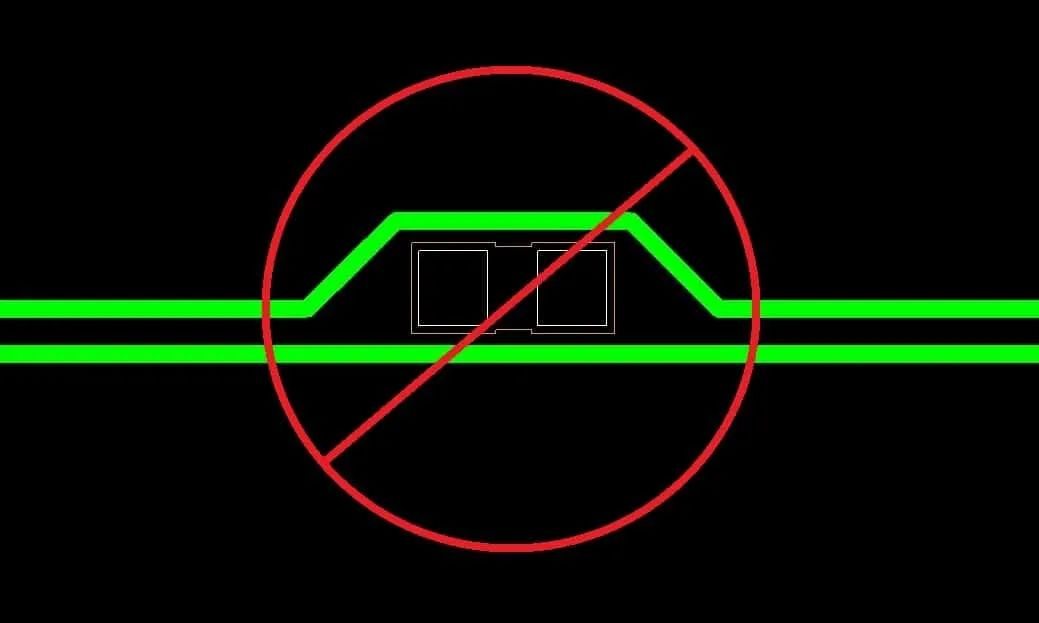

,勢必會造成EMI輻射,這種做法弊大于利。誤區(qū)二:認(rèn)為保持等間距比匹配線長更重要。在實(shí)際的PCB布線中,往往不能同時(shí)滿足差分設(shè)計(jì)的要求。由于管腳分布,過孔,以及走線空間等因素存在, 必須通過適當(dāng)?shù)睦@線

2017-07-07 11:45:56

是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。1、直角走線直角走線一般是PCB布線中要求盡量避免的情況,也

2014-08-13 15:44:05

MIPI信號走線相關(guān)要求 MIPI總線在目前的移動設(shè)備手機(jī)/平板的LCD或者Camera應(yīng)用的十分廣泛。 以下是MIPI信號走線規(guī)則一些Checklist 阻抗要求:MIPI的差分線阻抗

2023-04-12 15:08:27

的地環(huán)。以避免從大地受到干擾噪聲. USB方面的考慮 USB的差分信號線保持平行走線,以達(dá)到90 ohm的差分阻抗。由于PCB和走線的因素這樣的平行走線的要求是很難達(dá)到的。為了避免這樣的偏差盡可能

2023-04-13 16:09:54

保持足夠大的間距,走線的長度也得到了保證。整體上用的過孔比較少。 由于委托方在最后改變了之前的協(xié)議,要求按照他們定義的接口定義以及擺放位置,不得已將布局改成了右邊的圖。實(shí)際上由于整個(gè)PCB的面積只有

2019-10-17 04:37:54

:認(rèn)為保持等間距比匹配線長更重要。在實(shí)際的PCB布線中,往往不能同時(shí)滿足差分設(shè)計(jì)的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能達(dá)到線長匹配的目的,但帶來的結(jié)果必然是差分對的部分

2019-08-21 07:30:00

PCB布線的直角走線、差分走線和蛇形線基礎(chǔ)理論

2015-05-21 11:48:54

為了適應(yīng)PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

2013-08-29 15:43:30

倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

2017-11-22 20:04:14

走線的線距>=2倍的線寬。PCI板上的蛇?線就是為?適應(yīng)PCI 33MHzClock的線長要求。?在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

2018-09-20 11:05:23

》=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

2020-07-14 18:02:17

的線距>=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

2018-08-30 10:14:44

可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。 主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。 1. 直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量

2018-09-17 17:31:52

夾雜在差分信號之間的非查份(單獨(dú)一條)走線方式有什么要求嗎?這就是要畫的連接線PCB高速差分信號線四層怎么弄,還要求阻抗,就是一個(gè)連接線

2023-04-07 17:46:45

;=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等

2019-05-22 02:48:05

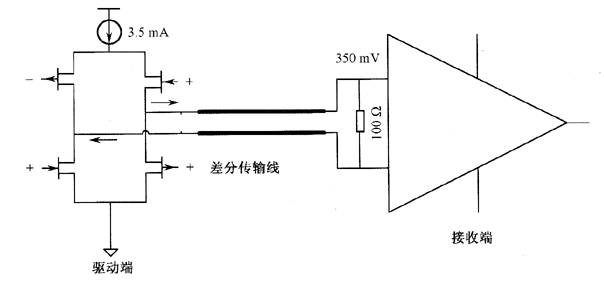

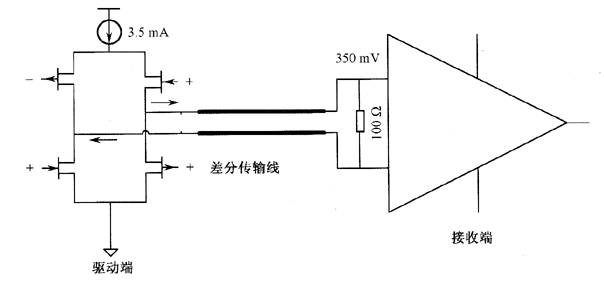

差分線抗干擾能力強(qiáng),信噪比高,輻射小,帶寬容量大等眾多優(yōu)點(diǎn),所以在目前的高速電路設(shè)計(jì)中,都選取差分線作為通信方式。差分線使用兩根走線傳輸一路信號,兩根線上攜帶的信息是相同的,但是信號的相位差是180

2020-10-29 08:56:44

我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復(fù)雜)謝謝!

2023-12-18 06:26:51

我看別人的板子差分對走線之間的過孔距離很寬,而我的這個(gè)差分對走線過孔離得很近,這個(gè)之間的規(guī)則是怎么設(shè)置的啊?沒找到呢,。。

2018-08-13 10:42:05

如何在 Altium Designer 6 中快速進(jìn)行差分對走線1: 在原理圖中讓一對網(wǎng)絡(luò)前綴相同,后綴分別為_N 和_P,并且加上差分隊(duì)對指示。在原理圖中,讓一對網(wǎng)絡(luò)名稱的前綴名相同,后綴分別為

2019-07-10 08:38:05

一.差分對內(nèi)兩信號的走線長度相等。該要求是基于以下兩個(gè)因素而提出的。(1)時(shí)序要求。由于差分信號的時(shí)需參考點(diǎn)是對內(nèi)兩信號邊沿的交叉點(diǎn),差分對內(nèi)兩信號走線長度的差異會造成交叉點(diǎn)的偏移,可能

2019-11-21 14:26:41

PCB布線中,有著許多需要注意的點(diǎn),比如:1.高頻時(shí)鐘線需要蛇形走線2.有些信號線需要設(shè)置差分對,差分走線

2019-05-31 06:23:05

來說,最關(guān)注的是如何確保在實(shí)際走線中能完全發(fā)揮差分線的這些優(yōu)勢。(1)定義差分對信號:在Router中,同時(shí)選定需要走差分線的網(wǎng)絡(luò)(Net),右擊后選擇Make Differential Net,如下

2015-01-12 15:38:59

。 誤區(qū)二:認(rèn)為保持等間距比匹配線長更重要。在實(shí)際的PCB布線中,往往不能同時(shí)滿足差分設(shè)計(jì)的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能達(dá)到線長匹配的目的

2010-03-16 09:23:41

: 2em">誤區(qū)二:認(rèn)為保持等間距比匹配線長更重要。在實(shí)際的PCB布線中,往往不能同時(shí)滿足差分設(shè)計(jì)的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能

2009-05-31 10:08:49

,布線在高速PCB設(shè)計(jì)中是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。

2009-08-20 20:58:49

是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。01直角走線直角走線一般是PCB布線中要求盡量避免

2018-07-08 13:28:36

還不夠深入。 誤區(qū)二:認(rèn)為保持等間距比匹配線長更重要。在實(shí)際的PCB布線中,往往不能同時(shí)滿足差分設(shè)計(jì)的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能達(dá)到線長匹配的目的,但

2018-09-21 11:53:08

如何確保在實(shí)際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是“等長、等距”。等長是為了保證兩個(gè)差分信號時(shí)刻保持相反極性,減少共模分量;等距則主要

2016-01-30 11:11:14

本帖最后由 cooldog123pp 于 2019-8-10 22:49 編輯

設(shè)置差分對,有好幾種方法,下面我就來一一介紹方法一:原理圖中直接設(shè)置好,然后導(dǎo)入到PCB中,如圖,給要設(shè)置的差

2016-09-27 09:19:50

【Altium小課專題 第007篇】差分線的添加走線與蛇形等長差分一般有90歐姆差分和100歐姆差分。差分類的創(chuàng)建(添加)和網(wǎng)絡(luò)類的創(chuàng)建(添加)稍微有點(diǎn)差異,需要在類管理器中添加分類名稱,然后在差

2021-03-29 15:12:01

;=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等.

2016-12-07 22:20:49

:認(rèn)為保持等間距比匹配線長更重要。在實(shí)際的PCB布線中,往往不能同時(shí)滿足差分設(shè)計(jì)的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能達(dá)到線長匹配的目的,但帶來的結(jié)果必然是差分對的部分

2019-03-18 21:38:12

新人,第一次用allegro,在pcb editor里布線,設(shè)置了差分對規(guī)則,返回布線的時(shí)候,選中差分對其中的一個(gè)引腳布線,但是只拉出來了一根線,右鍵里也沒有單根走線模式可選。求解。。。。。。

2015-04-15 17:38:54

請教大家一個(gè)問題,藍(lán)牙芯片NRF51822出來的兩個(gè)天線引腳,連接到巴倫上,這個(gè)兩個(gè)差分天線,走線有什么要求呢?比如阻抗多少呢?巴倫出來的單端天線,我知道做50歐,但是這個(gè)差分的,不曉得怎么走線

2015-02-03 10:13:34

,減小繞線間平行走線長度。 4.小結(jié) 在PCB設(shè)計(jì)時(shí)候要將等長的設(shè)計(jì)觀念逐步向等時(shí)設(shè)計(jì)轉(zhuǎn)變,在對時(shí)序或者等長要求高的設(shè)計(jì)尤其需要注意串?dāng)_,繞線方式,不同層走線,過孔時(shí)延等方面對時(shí)序的影響。豐富的SI(信號完整性)知識和正確的仿真方法可以幫助設(shè)計(jì)去評估PCB板上的傳輸時(shí)延,從而提高設(shè)計(jì)的質(zhì)量。

2014-10-21 09:51:22

畫千兆以太網(wǎng)接口,有4組差分對,每對靜態(tài)相位誤差設(shè)置的是5mil;同時(shí)這幾組差分對相互之間有等長約束。粗略的連好之后準(zhǔn)備繞線,現(xiàn)有如下問題:1.如何繞線使靜態(tài)相位誤差符合要求?目前我使用Delay

2017-12-08 21:08:13

在PCB布局走線時(shí)CAN需要差分等長線嗎?

2023-04-07 17:39:25

對于差分對有哪些要求?如何去設(shè)計(jì)差分對?

2021-05-20 06:15:42

射頻線PCB走線屏蔽孔,都有什么要求???求解

2016-01-13 14:40:40

一、差分對內(nèi)兩信號的走線長度相等該要求是基于以下兩個(gè)因素而提出的。(1) 時(shí)序要求:由于差分信號的時(shí)需參考點(diǎn)是對內(nèi)兩信號邊沿的交叉點(diǎn),差分對內(nèi)兩信號走線長度的差異會造成交叉點(diǎn)的偏移,可能

2023-03-16 11:24:22

能力強(qiáng)、能有效抑制EMI、時(shí)序定位精確。 對于PCB工程師來說,最關(guān)注的還是如何確保在實(shí)際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是“等長

2014-12-16 09:47:09

請教各位 我的差分對模型不對 我主要原理圖中調(diào)整了管腳位置 請問這種情況怎么更新到PCB呢?我導(dǎo)入網(wǎng)表這個(gè)就是不變我的差分對模型不對 我主要原理圖中調(diào)整了管腳位置 請問這種情況怎么更新到PCB呢?我導(dǎo)入網(wǎng)表這個(gè)就是不變

2015-01-29 14:35:38

T.K. Chin在他的博客文章《差分對:你真正需要了解的內(nèi)容》里談?wù)摿藢τ?b class="flag-6" style="color: red">差分對的要求。在現(xiàn)實(shí)應(yīng)用中,我們用印刷電路板(PCB)內(nèi)的銅走線或線纜組裝件內(nèi)的銅質(zhì)導(dǎo)線來實(shí)現(xiàn)差分對。較長的PCB走線或

2018-09-04 14:25:47

的要求一個(gè)良好設(shè)計(jì)差分對是成功進(jìn)行高速數(shù)據(jù)傳輸?shù)年P(guān)鍵因素。根據(jù)應(yīng)用的不同,差分對可以是一對印刷電路板 (PCB) 走線,一對雙絞線或一對共用絕緣和屏蔽的并行線(通常稱為Twin-axial電纜)。在這

2018-09-11 11:50:09

voltagedifferential signaling)就是指這種小振幅差分信號技術(shù)。 蛇形走線的幾點(diǎn)建議 蛇形線是Layout中經(jīng)常使用的一類走線方式。其主要目的就是為了調(diào)節(jié)延時(shí),滿足系統(tǒng)時(shí)序設(shè)計(jì)要求。其中最關(guān)鍵

2013-11-13 21:42:25

>=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 3MHzClock的線長要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等. :

2018-11-23 17:02:19

@我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對的對間等長有沒有要求?(PS:16對差分線,都做等長好復(fù)雜)謝謝!

2018-09-19 09:47:36

HDMI差分對PCB怎么走線?要計(jì)算匹配阻抗嗎?差分對走多長有要求嗎?四對差分對要走一樣長嗎?

2019-05-31 05:35:21

問一下差分信號的pcb走線長度差一般要求在多少mil之內(nèi)?

2011-03-28 12:36:59

管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能達(dá)到線長匹配的目的,但帶來的結(jié)果必然是差分對的部分區(qū)域無法平行,這時(shí)候我們該如何取舍呢?在下結(jié)論之前我們先看看下面一個(gè)仿真結(jié)果。 從上

2012-12-18 12:03:00

管腳分布,過孔,以及走線空間等因素存在,必須通過適當(dāng)?shù)睦@線才能達(dá)到線長匹配的目的,但帶來的結(jié)果必然是差分對的部分區(qū)域無法平行,這時(shí)候我們該如何取舍呢?在下結(jié)論之前我們先看看下面一個(gè)仿真結(jié)果。從上

2012-12-19 16:52:38

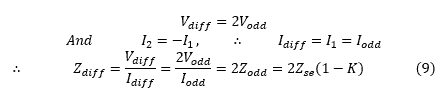

的EMI,如果不對差分信號進(jìn)行恰當(dāng)?shù)钠胶饣驗(yàn)V波,或者存在任何共模信號,就可能會產(chǎn)生EMI問題;其次是和單端信號相比,傳輸差分信號需要雙倍的信號線。 如圖2所示為差分對走線在PCB上的橫截面。D為兩個(gè)差

2018-11-27 10:56:15

PCB走線策略

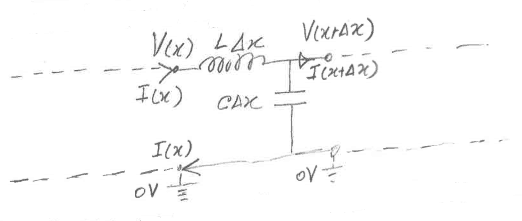

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得

2006-09-25 14:11:02 7284

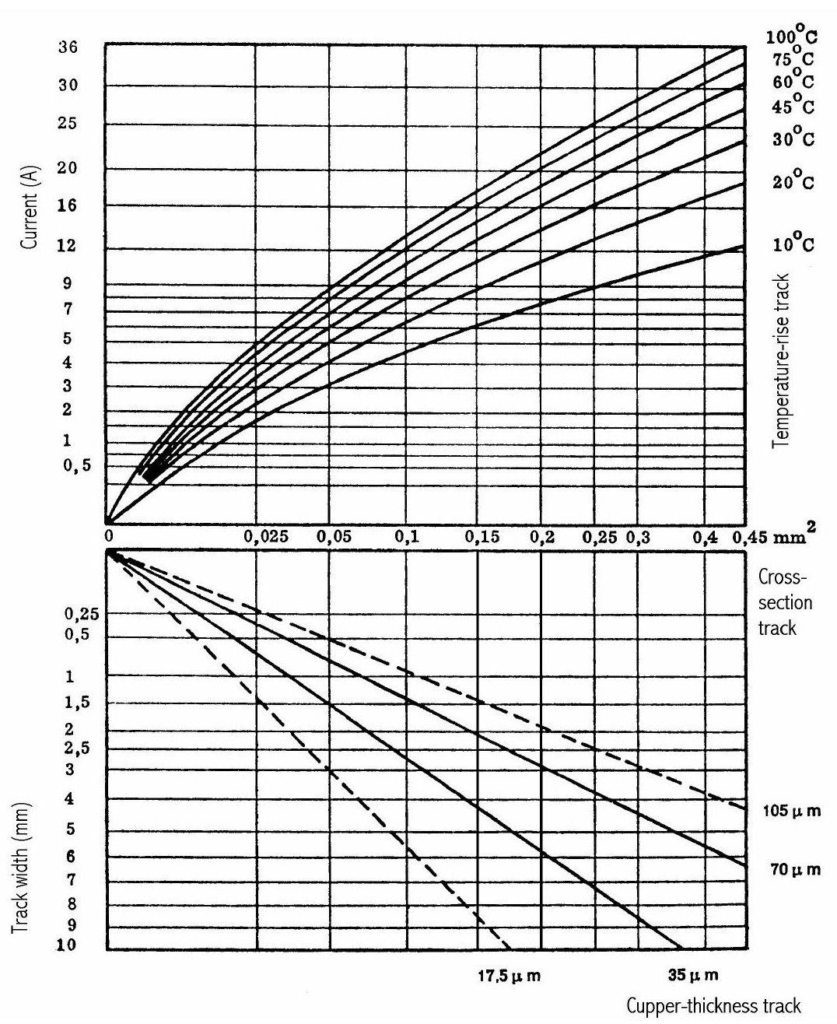

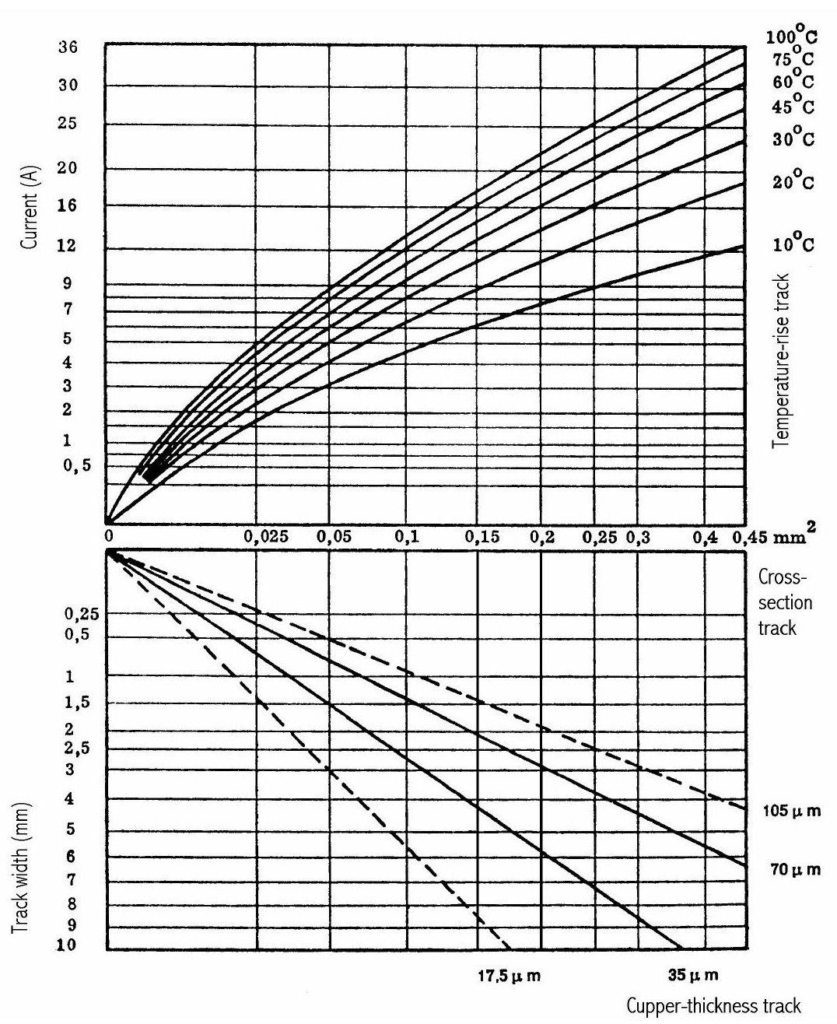

7284 在電路板PCB設(shè)計(jì)時(shí),有時(shí)候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力,通常是在PCB走線上鍍錫(或叫上錫),下面以在PCB底層走線鍍錫為例,使用Protel DXP2004軟件

2011-10-31 15:00:27 0

0 PCB設(shè)計(jì)與走線PCB設(shè)計(jì)與走線layout對PCB走線與擺件規(guī)則全面了解和 掌握提升走線和擺件技能。

2016-07-21 16:33:13 0

0 PCBLayout,中的直角走線、差分走線和蛇形線

2016-12-16 21:58:19 0

0 T.K. Chin在他的博客文章《差分對:你真正需要了解的內(nèi)容》里談?wù)摿藢τ?b class="flag-6" style="color: red">差分對的要求。在現(xiàn)實(shí)應(yīng)用中,我們用印刷電路板(PCB)內(nèi)的銅走線或線纜組裝件內(nèi)的銅質(zhì)導(dǎo)線來實(shí)現(xiàn)差分對。較長的PCB走線或

2017-04-18 01:44:02 1430

1430 是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu) 化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。 1、直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一

2017-12-01 10:37:31 0

0 很多人對于PCB走線的參考平面感到迷惑,經(jīng)常有人問:對于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?

2018-03-08 17:18:54 10628

10628

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中是至關(guān)重要的。下面將針對實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。

2018-04-14 11:06:00 4042

4042

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-07-01 15:24:50 6358

6358 Test Coupon,是用來以 TDR (Time Domain Reflectometer 時(shí)域反射計(jì)) 來測量所生產(chǎn)的 PCB 的特性阻抗是否滿足設(shè)計(jì)的要求,一般要控制的阻抗有單端線和差分對

2019-08-12 11:27:20 7986

7986 PCB走線的參考平面在哪?

很多人對于PCB走線的參考平面感到迷惑,經(jīng)常有人問:對于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?

2019-08-20 15:47:13 7706

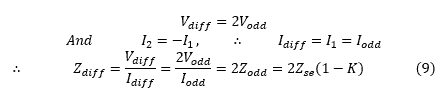

7706 大多數(shù)情況下,差分對的唯一指定要求是其差分阻抗。

2019-09-11 16:48:09 7782

7782

為了獲得較好的信號完整性,可以選用差分對來對高速信號進(jìn)行走線

2019-09-19 14:19:10 6689

6689

在大多數(shù)帶狀線差分對的實(shí)際情況中,歸納如果信號層上方和下方的PCB材料的介電常數(shù)幾乎相等,則耦合系數(shù)'KL'和電容耦合系數(shù)'KC'幾乎相等。

2019-09-08 14:11:00 7162

7162

,參考平面用作信號的接地返回路徑,以最大程度地減少電磁干擾( EMI )。 參考平面與差分對走線所連接的收發(fā)器芯片共享相同的接地連接。它通常用于涉及差分信號的設(shè)計(jì)中,例如 USB , SATA , HDMI 和 PCIe 。 對于差分信號的參考平面的需求一直存在

2020-09-16 20:05:15 4685

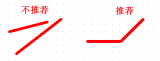

4685 角度走線挑戰(zhàn)廠商生產(chǎn)能力,很多蝕刻銅線時(shí)候出現(xiàn)問題,推薦45°或135°走線,如圖3-21所示。 圖3-21任意角度走線和135°走線 3、如圖3-22,同一網(wǎng)絡(luò)不宜90°直角或銳角走線,一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,直角走線會使傳輸線的線寬發(fā)

2021-01-21 11:35:44 15214

15214

電子發(fā)燒友網(wǎng)為你提供PCB LAYOUT的直角走線、差分走線、蛇形線資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:41:16 17

17 電子發(fā)燒友網(wǎng)為你提供PCB三種特殊走線技巧:直角走線,差分走線,蛇形線資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-16 08:45:45 104

104 布線(Layout)是pcb設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速pcb設(shè)計(jì)中

2022-02-10 12:11:07 40

40 布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過 Layout 得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速 PCB 設(shè)計(jì)中

2022-02-11 15:24:33 30

30 Cadence Allegro在PCB中手動或者自動添加差分對屬性 設(shè)計(jì)PCB過程中,若設(shè)計(jì)中有差分對信號,則需要將是差分的2個(gè)信號設(shè)置為差分對,設(shè)置差分對有2種方式:手動添加及自動添加 一、手動

2022-12-16 08:00:07 3318

3318 設(shè)計(jì) PCB 變得非常容易, 由于可用的工具負(fù)載。對于正在接觸PCB設(shè)計(jì)的初學(xué)者來說, 他可能不太關(guān)心PCB中使用的走線特性。然而,當(dāng)你爬上梯子時(shí),注意PCB走線是非常重要的。在本文中,我們匯總了一些您應(yīng)該了解的有關(guān)PCB走線以及如何為您的PCB設(shè)計(jì)正確走線的重要事項(xiàng)。

2023-05-13 15:15:46 6742

6742

:較之單一的走線,差分對布線更受青睞。不過,差分對布線可能沒那么容易,因?yàn)樗鼈儽仨氉裱囟ǖ囊?guī)則,這樣才能確保信號的性能。這些規(guī)則決定了一些細(xì)節(jié),如差分對的走線寬度和

2022-12-05 11:06:06 2340

2340

但是差分信號也有其缺點(diǎn):首先是會產(chǎn)生潛在的EMI,如果不對差分信號進(jìn)行恰當(dāng)?shù)钠胶饣驗(yàn)V波,或者存在任何共模信號,就可能會產(chǎn)生EMI問題;其次是和單端信號相比,傳輸差分信號需要雙倍的信號線。

2023-09-01 17:26:03 1555

1555

詳解pcb走線電流

2023-10-30 15:59:23 3234

3234 PCB設(shè)計(jì)中常見的走線等長要求

2023-11-24 14:25:36 6535

6535

高效差分對布線指南:提高 PCB 布線速度

2023-11-29 16:00:52 6417

6417

在汽車電子、航空航天等領(lǐng)域中控制器局域網(wǎng)(CAN)接口發(fā)揮著重要作用,在PCB Layout方面工程師需要下夠足夠的功夫才能更好的保證CAN接口的可靠性和穩(wěn)定性,下面捷多邦小編和大家介紹一下CAN總線pcb走線要求都有哪些?

2023-11-28 15:02:38 10130

10130 差分線pcb走線原則? 差分線是PCB設(shè)計(jì)中非常重要的一個(gè)部分,它的設(shè)計(jì)和走線原則可以直接影響到電路性能的穩(wěn)定性和可靠性。在以下文章中,我將詳盡、詳實(shí)、細(xì)致地探討差分線的設(shè)計(jì)原則及其在PCB走線中

2023-12-07 18:09:37 7617

7617 差分走線是一種在高速PCB設(shè)計(jì)中常用的信號傳輸方式,它與射頻走線有一定的關(guān)聯(lián),但也有其獨(dú)特的特點(diǎn)和應(yīng)用場景。

2024-04-10 16:26:37 4160

4160 在PCB設(shè)計(jì)中,差分對的走線操作是一項(xiàng)關(guān)鍵任務(wù),它直接影響到信號的完整性和電路的性能。差分信號通常用于高速數(shù)字通信,因?yàn)樗鼈兡軌蛴行У氐挚闺姶鸥蓴_和提供準(zhǔn)確的時(shí)序信號。

2024-04-10 16:34:08 4520

4520 PCB(Printed Circuit Board)螺旋走線是一種在 PCB 設(shè)計(jì)中常用的布線方式。它通過將導(dǎo)線以螺旋狀的形式布置在 PCB 上,以實(shí)現(xiàn)特定的電氣性能和信號傳輸要求。今天捷多邦小編

2024-08-06 17:28:29 1292

1292

電子發(fā)燒友App

電子發(fā)燒友App

評論