PCB布線中的蛇形走線

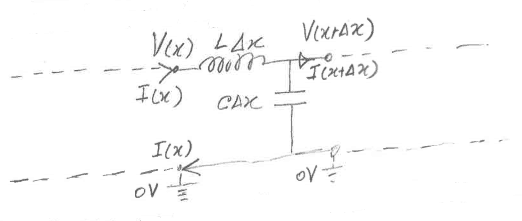

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走

2009-09-13 15:15:12 5923

5923 本文主要詳解PCB設計高速模擬輸入信號走線,首先介紹了PCB設計高速模擬輸入信號走線方法,其次闡述了九大關于PCB設計高速模擬輸入信號走線規則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 10092

10092

層三、網格中添加過孔避免熱點四、路由高速信號135°走線彎曲五、增加瓶頸區域外的線距離六、增加菊花鏈路(避免長存根)七、差分布線原則八、正和負信號間的緊密延遲偏差

2025-05-28 19:34:36 2044

2044

PCB設計布線(Layout)的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。

2016-07-18 14:07:10 48837

48837 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中

2015-01-12 14:53:57

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中

2019-06-10 10:11:23

的設計理論也要最終經過 Layout得以實現并驗證,由此可見,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線

2017-07-07 11:45:56

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-05-23 08:52:37

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2025-03-13 11:35:03

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2014-08-13 15:44:05

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-08-05 06:40:24

打孔換層,換層優先選擇兩邊是GND的層面處理。盡量收發信號布線在不同層,如果空間有限,需收發信號走線同層時,應加大收發信號之間的布線距離。

針對以上高速信號還有如下方面的要求:

一、BGA焊盤區域挖

2023-08-01 18:02:03

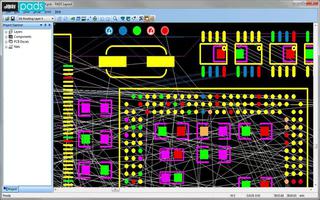

:認為保持等間距比匹配線長更重要。在實際的PCB布線中,往往不能同時滿足差分設計的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當的繞線才能達到線長匹配的目的,但帶來的結果必然是差分對的部分

2019-08-21 07:30:00

PCB布線的直角走線、差分走線和蛇形線基礎理論

2015-05-21 11:48:54

PCB布線這幾種走線方式,你會嗎?在我們學習嵌入式開發的過程中,PCB布線是必不可少的。好的布線方式,輕則看著美觀、布局合理,重則可以節約生產成本,達到良好的電路性能和散熱性能,使元器件的性能達到

2020-02-28 10:50:28

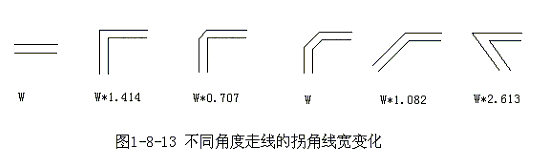

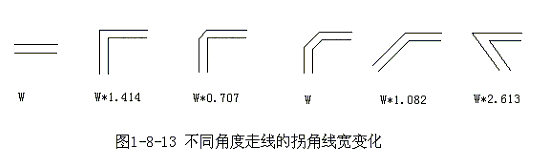

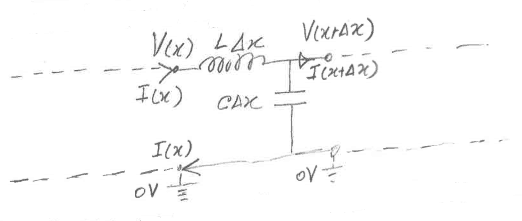

線角度 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產生多大的影響呢? 從原理上說,直角走線會使傳輸線的線寬發生變化,造成阻抗的不連續

2019-08-20 15:27:06

的線寬間距,并設置到約束管理器。 差分線通過互相耦合來減少共模干擾,在條件許可的情況下要盡可能平行布線,兩根線中線不能有過孔或其他信號。 差分對需要嚴格控制相位,所以對內需要嚴格控制等長。 為減少

2023-04-12 15:08:27

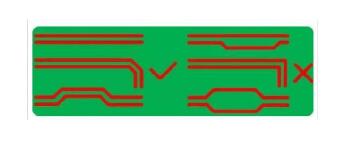

可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。 主要從直角走線,差分走線,蛇形線等三個方面來闡述。 1. 直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量

2018-09-17 17:31:52

在pcb上靠近平行走高速差分信號線對的時候,在阻抗匹配的情況下,由于兩線的相互耦合,會帶來很多好處。但是有觀點認為這樣會增大信號的衰減,影響傳輸距離,為什么?我在一些大公司的評估板上看到高速布線有的

2012-03-03 12:37:52

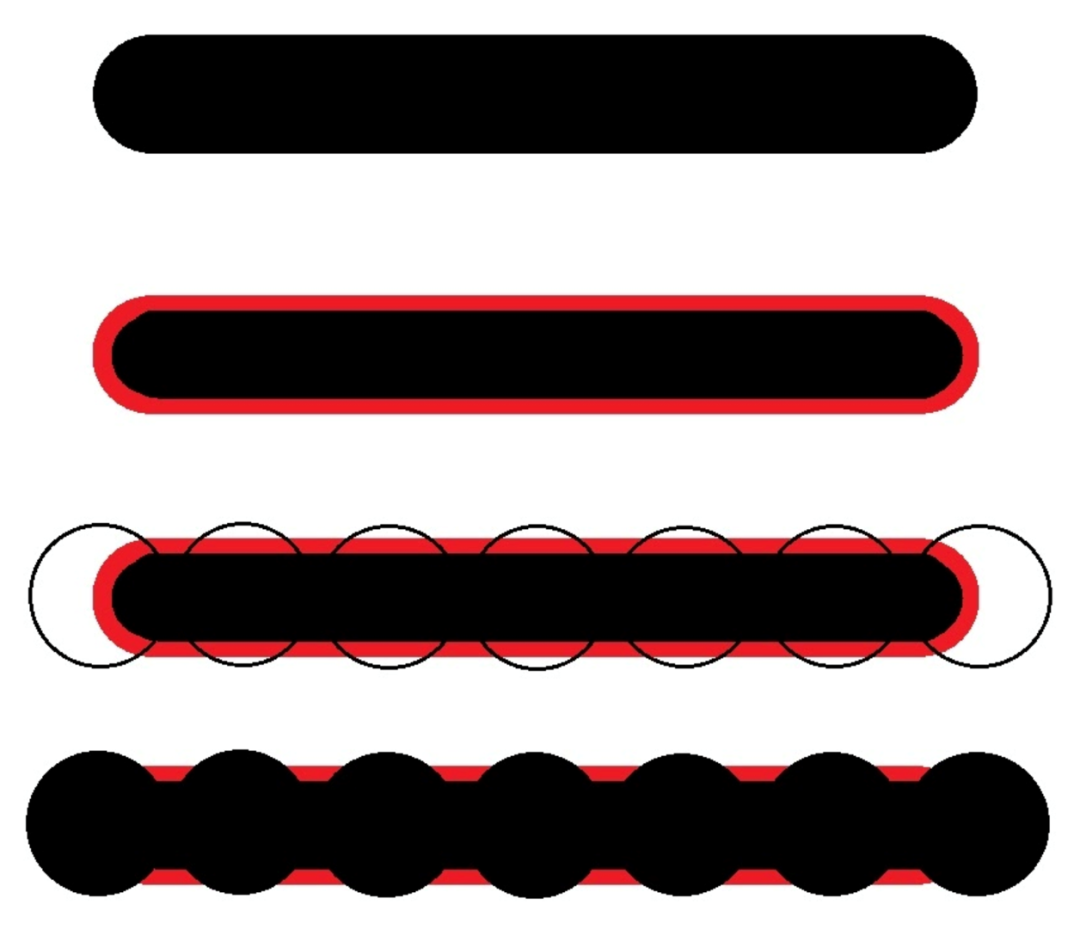

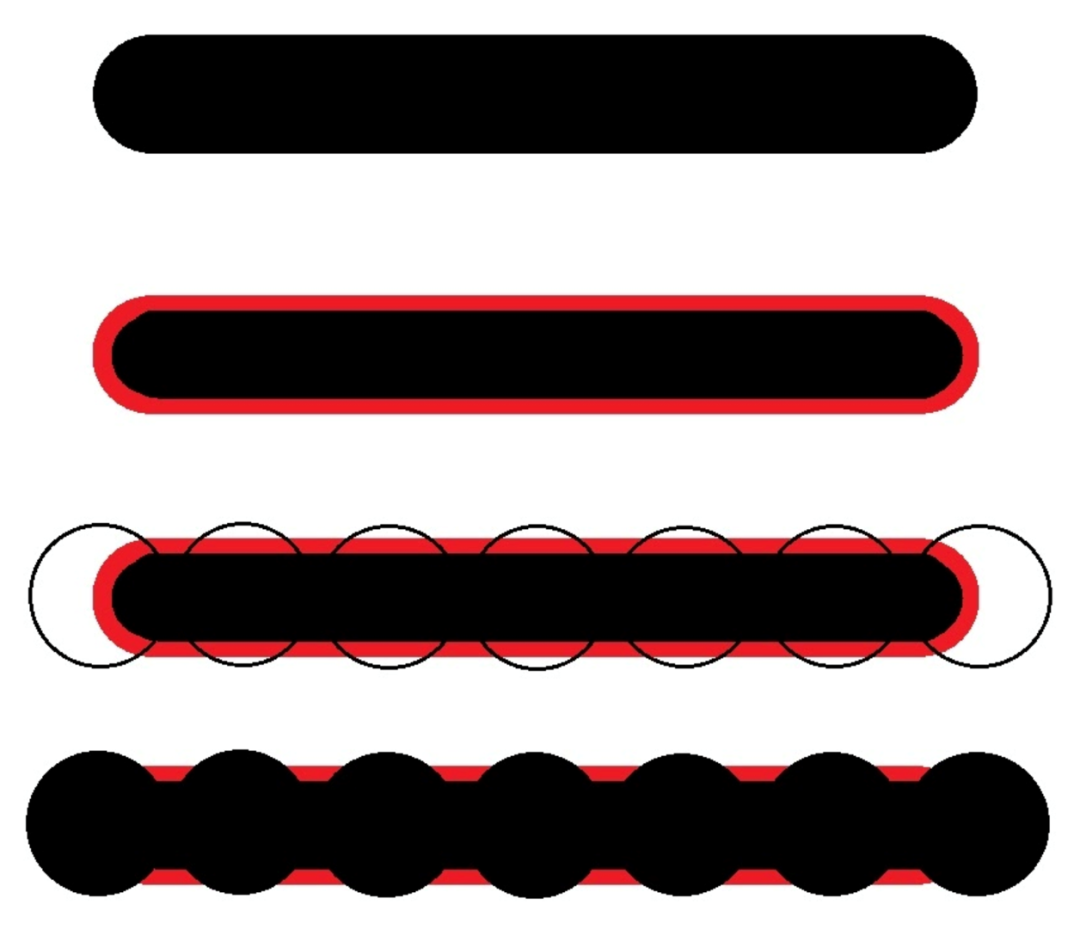

分布線方式是如何實現的? 差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩 種,一為兩條線走在同一走線層

2015-01-09 11:14:05

)與調整走線的拓樸。4、差分布線方式是如何實現的?差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩種,一為

2021-09-19 14:47:06

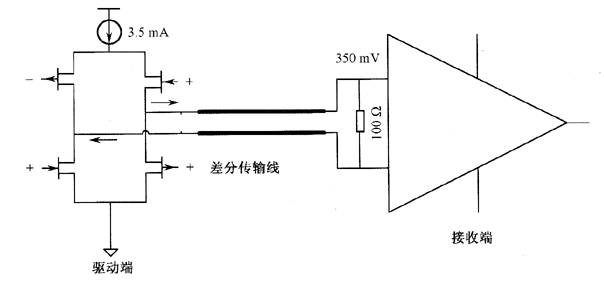

為了避免不理想返回路徑的影響,可以采用差分對走線。為了獲得較好的信號完整性,可以選用差分對來對高速信號進行走線,如圖1所示,LVDS電平的傳輸就采用差分傳輸線的方式。 圖1 差分對走線實例

2018-11-27 10:56:15

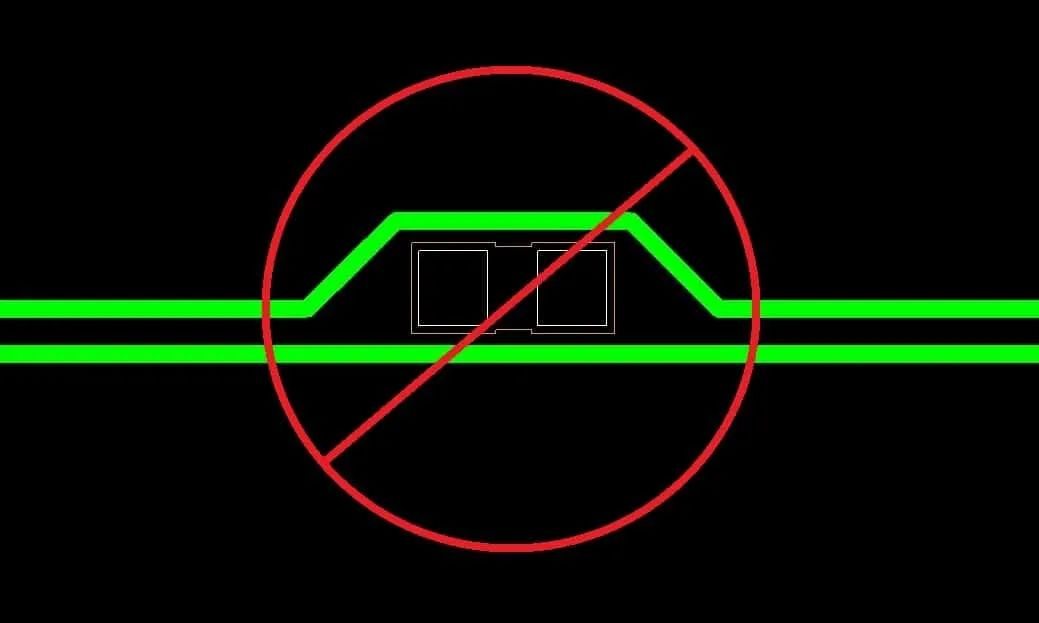

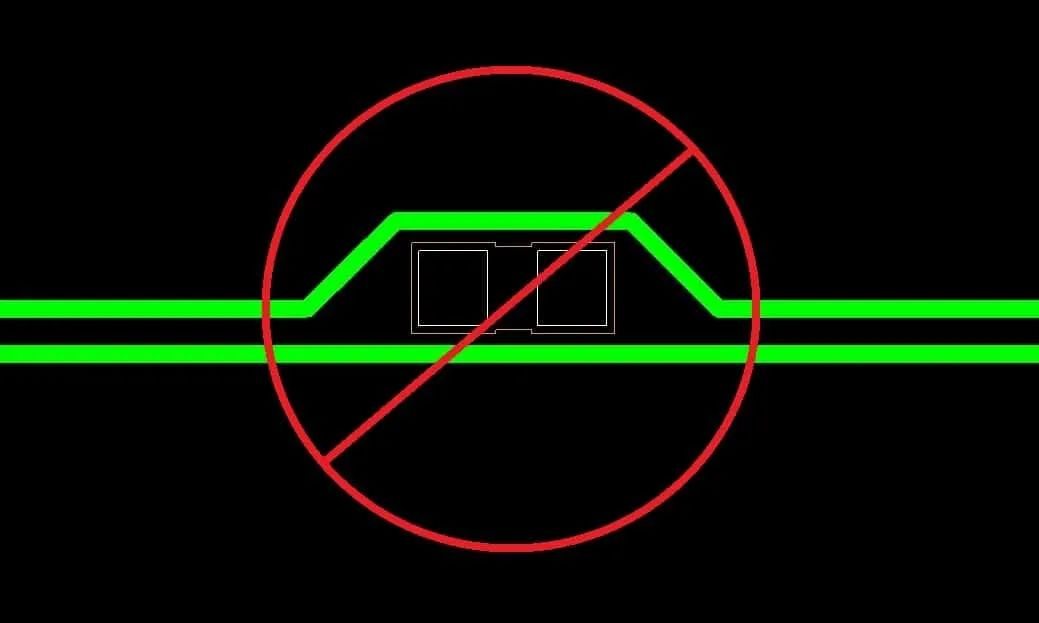

信號的特性阻抗連續規則高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。規則五、高速PCB設計的布線方向規則

2021-03-31 06:00:00

,不同層的走線阻抗必須連續。規則五、高速PCB設計的布線方向規則 相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串擾,增加EMI輻射。 簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以

2022-04-18 15:22:08

管腳分布,過孔,以及走線空間等因素存在,必須通過適當的繞線才能達到線長匹配的目的,但帶來的結果必然是差分對的部分區域無法平行,這時候我們該如何取舍呢?在下結論之前我們先看看下面一個仿真結果。 從上

2012-12-18 12:03:00

管腳分布,過孔,以及走線空間等因素存在,必須通過適當的繞線才能達到線長匹配的目的,但帶來的結果必然是差分對的部分區域無法平行,這時候我們該如何取舍呢?在下結論之前我們先看看下面一個仿真結果。從上

2012-12-19 16:52:38

一系列阻抗問題。 高速設計的另一個關鍵領域是差分對的布線。差分對通過以互補的方式驅動兩個信號跡線來操作。差分對提供出色的抗噪聲能力和更高的S / N比。然而,實現這些優勢有兩個限制: 1、兩條走線

2023-04-12 15:20:37

,工程師應該盡可能地用最少層數滿足實際設計需要,從而致使布線密度不可避免地增大,而在PCB布線設計中,其走線寬度越細,間隔越小,信號間串擾就越大,其能傳送功率越小。因此,走線尺寸的選擇必須考慮到各方面

2018-11-27 09:57:50

影響各自的特性阻抗, 變的較小, 根據分壓原理(voltage divider)這會使信號源送到線上的電壓小一點。 至于, 因耦合而使信號衰減的理論分析我并沒有看過, 所以我無法評論。 對差分對的布線方式

2012-08-15 20:35:17

在未布板之前,先將高速USB主控制器和一些相關的主要器件擺放好。盡可能縮短走線長度,優先考慮對高速時鐘信號和高速USB差分線的布線,盡可能的避免高速時鐘信號與高速USB差分線和任何的接插件靠近走線

2019-05-30 07:36:38

我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2023-12-18 06:26:51

請問,pcb中已經布完差分對后,發現有部分差分對需要調整線寬和線間距,現在只知道修改RULES,然后重新走一遍布線,相當于重新布線了,量大很麻煩。有沒有便捷的方法呢?

2016-08-03 14:50:36

我看別人的板子差分對走線之間的過孔距離很寬,而我的這個差分對走線過孔離得很近,這個之間的規則是怎么設置的啊?沒找到呢,。。

2018-08-13 10:42:05

如何在 Altium Designer 6 中快速進行差分對走線1: 在原理圖中讓一對網絡前綴相同,后綴分別為_N 和_P,并且加上差分隊對指示。在原理圖中,讓一對網絡名稱的前綴名相同,后綴分別為

2019-07-10 08:38:05

PCB布線中,有著許多需要注意的點,比如:1.高頻時鐘線需要蛇形走線2.有些信號線需要設置差分對,差分走線

2019-05-31 06:23:05

來說,最關注的是如何確保在實際走線中能完全發揮差分線的這些優勢。(1)定義差分對信號:在Router中,同時選定需要走差分線的網絡(Net),右擊后選擇Make Differential Net,如下

2015-01-12 15:38:59

為了保證良好的信號質量, USB 2.0 端口數據信號線按照差分線方式走線。為了達到USB 2.0 高速 480MHz 的速度要求,建議 PCB 布線設計采用以下原則:差分數據線走線盡可能短、直,差分數據線對內走線長度嚴格等長,走線長度偏差控制在±5mil 以內。

2019-05-23 08:52:33

,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。

2009-08-20 20:58:49

是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。01直角走線直角走線一般是PCB布線中要求盡量避免

2018-07-08 13:28:36

現在學習cadence,PCB布線時,感覺命令不聽使喚,總是繞的亂不七八糟,但是取消差分對采單個模式又擔心達不到效果,求有經驗的前輩說說看

2015-12-28 22:38:54

:認為保持等間距比匹配線長更重要。在實際的PCB布線中,往往不能同時滿足差分設計的要求。由于管腳分布,過孔,以及走線空間等因素存在,必須通過適當的繞線才能達到線長匹配的目的,但帶來的結果必然是差分對的部分

2019-03-18 21:38:12

新人,第一次用allegro,在pcb editor里布線,設置了差分對規則,返回布線的時候,選中差分對其中的一個引腳布線,但是只拉出來了一根線,右鍵里也沒有單根走線模式可選。求解。。。。。。

2015-04-15 17:38:54

, 是否有足夠的約束條件控制蛇行線(serpentine)蜿蜒的方式, 能否控制差分對的走線間距等。 這會影響到自動布線出來的走線方式是否能符合設計者的想法。 另外, 手動調整布線的難易也與繞線引擎的能力

2009-03-20 14:07:39

大神手把手教你如何進行pcb高速線布線

2021-05-13 06:22:15

怎樣計算PCB布線中走線允許的最大長度?走線太長了都有哪些影響呢?

2023-04-10 17:10:25

在PCB設計中,布線是完成產品設計的重要步驟,PCB走線的好壞直接影響整個系統的性能,布線在高速PCB設計中是至關重要的。布線的設計過程限定高,技巧細、工作量大。PCB布線有單面布線、 雙面布線

2014-12-16 09:47:09

的要求一個良好設計差分對是成功進行高速數據傳輸的關鍵因素。根據應用的不同,差分對可以是一對印刷電路板 (PCB) 走線,一對雙絞線或一對共用絕緣和屏蔽的并行線(通常稱為Twin-axial電纜)。在這

2018-09-11 11:50:09

的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。 圖4 特性阻抗連續規則 規則五:高速PCB設計的布線方向規則 相鄰兩層間的走線必須遵循垂直走線的原則

2018-09-20 10:38:01

HDMI差分對PCB怎么走線?要計算匹配阻抗嗎?差分對走多長有要求嗎?四對差分對要走一樣長嗎?

2019-05-31 05:35:21

)與調整走線的拓樸。4、差分布線方式是如何實現的?差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩種,一為

2017-01-20 10:29:29

PCB走線策略

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得

2006-09-25 14:11:02 7284

7284 PCB設計布線中的3種特殊走線技巧,學習資料,感興趣的可以看看。

2022-05-12 10:34:20 0

0 PCB布線中的走線策略,是精華資料。

2016-12-16 21:54:48 0

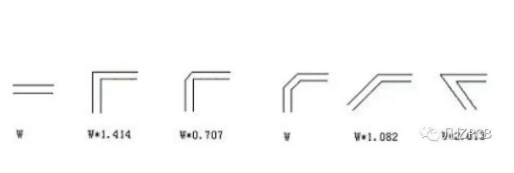

0 PADS可提供強大且易于使用的多走線高速布線功能,幫助您應對這些挑戰。讓您可以根據PCB設計定義的規則選擇并完成多走線布線。以及根據需要選擇要完成的走線數量。如果采用PADS多走線HSDRouter,一切盡在您的掌握之中。

2017-09-19 11:41:38 29

29 PCB設計中的各種特性來教你如何完成PCB布線后的檢查工作,做好最后的把關工作! 在講解PCB布線完成后的檢查工作之前,先為大家介紹三種PCB的特殊走線技巧。將從直角走線,差分走線,蛇形線三個方面來闡述PCB LAYOUT的走線:

2017-09-19 16:23:21 44

44 規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 8707

8707

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2017-12-01 10:37:31 0

0 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。

2018-04-14 11:06:00 4042

4042

布線(Layout)是 PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB設計中

2018-07-06 15:28:18 6749

6749 布線(Layout)是pcb設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速pcb設計中

2018-11-13 09:17:24 3430

3430 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產生多大的影響呢?從原理上說,直角走線會使傳輸線的線寬發生變化,造成阻抗的不連續。其實不光是直角走線,頓角,銳角走線都可能會造成阻抗變化的情況。

2019-07-24 15:12:01 1967

1967

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中是至關重要的。

2019-06-04 14:18:23 1676

1676 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-04-30 08:00:00 0

0 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產生多大的影響呢?從原理上說,直角走線會使傳輸線的線寬發生變化,造成阻抗的不連續。其實不光是直角走線,頓角,銳角走線都可能會造成阻抗變化的情況。

2019-05-08 14:06:17 7397

7397

在設計復雜的 PCB 時,PADS 技術可使您擁有高速布線能力。差分對和具有長度約束的布線,包括匹配長度、虛擬管腳和關聯的網絡,這些功能使您在 PCB 上管理 DDRx、PCI Express、SATA 和實施其他一些高速技術變得非常輕松。

2019-05-15 06:30:00 5488

5488

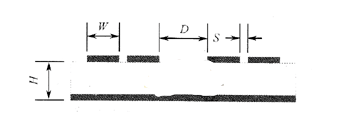

差分對走線分外層微帶線差分模式和內層帶狀線差分模式兩種,通過合理設置參數,阻抗可利用相關阻抗計算軟件(如POLAR-SI9000)計算也可利用阻抗計算公式計算。

2019-05-31 15:55:55 8115

8115

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-07-01 15:24:50 6358

6358 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-07-19 16:47:50 0

0 在保持信號完整性方面,必須在高速數字電路中正確布線差分對。遵循這些差分對路由指南并將你的EMI問題拋在腦后。

2019-07-25 10:48:03 3749

3749 為了獲得較好的信號完整性,可以選用差分對來對高速信號進行走線

2019-09-19 14:19:10 6689

6689

在大多數帶狀線差分對的實際情況中,歸納如果信號層上方和下方的PCB材料的介電常數幾乎相等,則耦合系數'KL'和電容耦合系數'KC'幾乎相等。

2019-09-08 14:11:00 7161

7161

規則一:高速信號走線屏蔽規則 如上圖所示: 在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 13255

13255 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2020-10-14 10:43:00 6

6 對于 PCB 而言,在 布線 和走線通過適當的規劃,可以避免嚴重的故障和因此帶來的流量阻塞或錯誤。為了使流量保持在可接受的水平,有必要在設計過程的早期階段了解所需的電源電路和組件連接。 PCB

2020-09-01 14:10:55 4559

4559 ,參考平面用作信號的接地返回路徑,以最大程度地減少電磁干擾( EMI )。 參考平面與差分對走線所連接的收發器芯片共享相同的接地連接。它通常用于涉及差分信號的設計中,例如 USB , SATA , HDMI 和 PCIe 。 對于差分信號的參考平面的需求一直存在

2020-09-16 20:05:15 4685

4685 高速串行總線的普及,使得PCB板上差分信號越來越多,那么,PCB板如何差分布線? 各類差分線的阻抗要求不同,根據設計要求,通過阻抗計算軟件計算出差分阻抗和對應的線 寬間距,并設置到約束管理器。 差

2020-12-04 11:14:51 9659

9659 讓你布線少走彎道的15條高速PCB布線經驗分享

2022-02-12 10:44:53 6469

6469 讓你布線少走彎道的15條高速PCB布線經驗分享

2021-03-04 06:24:26 31

31 等效為傳輸線上的容性負載,減緩上升時間。 2.阻抗不連續會造成信號的反射。 3.直角尖端產生的EMI。 原理上來說,pcb布線是銳角、直角走線就會讓傳輸線的線寬發生變化,造成阻抗的不連續,阻抗不連續就會反射。按照反射的幅度和延時,在最開始的

2021-08-18 16:34:00 28487

28487 布線(Layout)是pcb設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速pcb設計中

2022-02-10 12:11:07 40

40 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中

2022-02-11 15:24:33 30

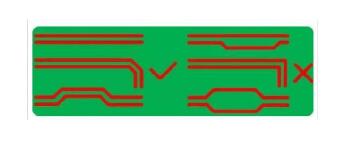

30 高速差分布線最佳實踐:對稱地布置差分對,并保持信號平行。不包括差分器之間的任何組件或通孔。對稱地放置耦合電容器

2022-10-25 10:36:42 852

852 不過,差分對布線可能沒那么容易,因為它們必須遵循特定的規則,這樣才能確保信號的性能。這些規則決定了一些細節,如差分對的走線寬度和間距,以及許多其他方面,如導線如何在電路板上一起布線。

2022-12-30 14:09:12 7440

7440 :較之單一的走線,差分對布線更受青睞。不過,差分對布線可能沒那么容易,因為它們必須遵循特定的規則,這樣才能確保信號的性能。這些規則決定了一些細節,如差分對的走線寬度和

2022-12-05 11:06:06 2340

2340

詳解高密 PCB走線布線的垂直導電結構 (VeCS)

2023-11-28 17:00:09 3158

3158

高效差分對布線指南:提高 PCB 布線速度

2023-11-29 16:00:52 6417

6417

差分線pcb走線原則? 差分線是PCB設計中非常重要的一個部分,它的設計和走線原則可以直接影響到電路性能的穩定性和可靠性。在以下文章中,我將詳盡、詳實、細致地探討差分線的設計原則及其在PCB走線中

2023-12-07 18:09:37 7616

7616 由于 PCB 板的密度越來越高,許多 PCB LAYOUT 工程師在走線的過程中,較容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的 PCB 走線的時候產生了閉環的結果,這樣的閉環結果將產生環形天線,增加 EMI 的輻射強度。

2024-01-08 15:33:04 2544

2544

在PCB設計中,差分對的走線操作是一項關鍵任務,它直接影響到信號的完整性和電路的性能。差分信號通常用于高速數字通信,因為它們能夠有效地抵抗電磁干擾和提供準確的時序信號。

2024-04-10 16:34:08 4519

4519 一根線為正極性信號線(P線),另一根線為負極性信號線(N線),這兩根線平行布線且保持恒定的距離。本文將深入探討高速差分信號走線的要點,包括信號線選擇、阻抗匹配、走線布局、屏蔽與接地等方面,以期為相關領域的工程師和技術人員提供參考。

2024-05-16 16:33:28 2399

2399

電子發燒友App

電子發燒友App

評論