Cadence Allegro在PCB中手動或者自動添加差分對屬性

設計PCB過程中,若設計中有差分對信號,則需要將是差分的2個信號設置為差分對,設置差分對有2種方式:手動添加及自動添加

一、手動添加差分對:

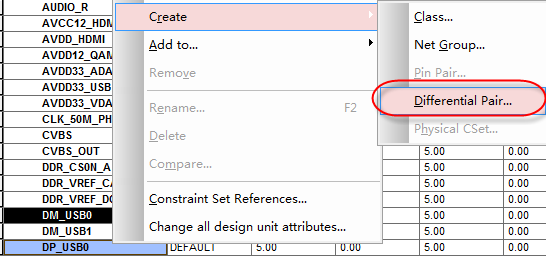

1、點擊Setup-Constraints-Constraint Manager調出CM規則管理器,然后到Physical規則管理器下點擊Net-All Layers,然后在右側欄中選中2根需要設置為差分對的信號,按Ctrl鍵全選中后右擊,選擇Create-Differential Pair,如圖1所示;

圖1 創建差分對圖示

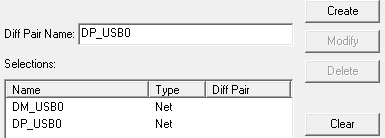

2、在彈出的對話框中設置好差分對的名稱,點擊Create,即可創建差分對規則,如圖2所示;

圖2 Create Differential Pair選項卡

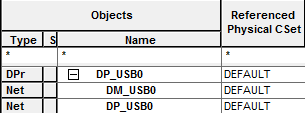

3、創建后即可在此管理器中生成差分對,如圖3所示。

圖3 手動創建的差分對圖示

二、自動生成差分對:

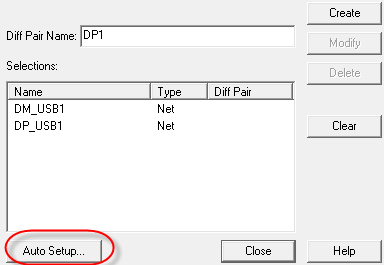

1、可以從上述步驟中的Create Differential Pair選項卡中點擊Auto Setup選項,如圖4所示;

圖4Create Differential Pair選項卡

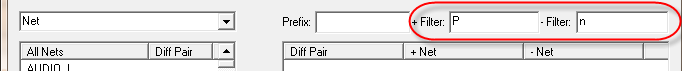

2、在彈出的對話框中,在Filter的2個對話框中輸入差分對的后綴(一般是“+、-”或者“P、N”),如圖5所示;

圖5Differential Pair Automatic Setup選項卡

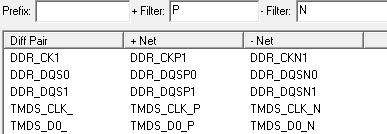

3、輸入后,在Prefix的框中點擊一下,軟件會自動將識別出來的差分信號列在其下的方框內,如圖6所示;

圖6Differential Pair Automatic Setup選項卡

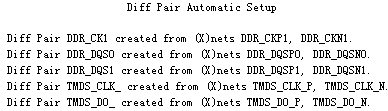

4、然后點擊Create,即可自動將設計中的差分對自動創建好并且會生成Log結果列表,如圖7所示。

圖7Diff Pairs Automatic Setup Log File圖示

聲明: 本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207 ?

?分享點贊在看“三連”支持!

點擊“閱讀原文”查看更多干貨文章

?

?分享點贊在看“三連”支持!

點擊“閱讀原文”查看更多干貨文章

原文標題:Cadence Allegro在PCB中手動或者自動添加差分對屬性

文章出處:【微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

-

pcb

+關注

關注

4404文章

23877瀏覽量

424223

原文標題:Cadence Allegro在PCB中手動或者自動添加差分對屬性

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

2025 Cadence 中國技術巡回研討會即將開啟 ——系統設計與分析專場研討會(上海站)

技術資訊 I 在 Allegro PCB 中如何快速布局

技術資訊 I Allegro PCB 設計中布線優化

技術資訊 I Allegro設計中的過孔陣列設計

技術資訊 I 圖文詳解約束管理器-差分對規則約束

Allegro更新原理圖導入網表后,Xnet混亂何解?

借助Cadence工具簡化PCB設計流程

高速PCB設計挑戰 Allegro Skill布線功能 自動創建match_group

手動添加cubeMX的軟件自動生成代碼后,編譯出現’rtthread.elf’:No Such File 的錯誤怎么解決?

Allegro Skill布線功能-添加差分過孔禁布區

Cadence Allegro在PCB中手動或者自動添加差分對屬性

Cadence Allegro在PCB中手動或者自動添加差分對屬性

評論