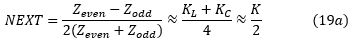

在查看差分阻抗以及偶數或共模之后,我們現在深入研究差分對的物理參數。

我們將討論:

線路電感和電容

案例1:奇數模式

案例2:偶數模式

單端阻抗

兩個串擾相關參數

差分對的詳細分析線電感和電容的分析

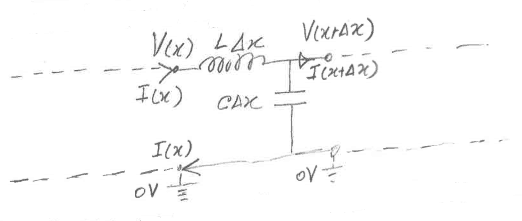

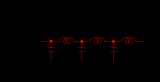

使用以下電路模型對無損單端傳輸線進行分析,得到無窮小的長度'delta x':

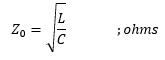

這里,'L'和'C'分別是線路每單位長度的電感和電容。經過分析,我們得出一條點的線的特征(或瞬時)阻抗由下式給出:

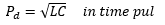

傳播延遲'Pd '給出了:

我們現在可以將上述模型和結果應用于差分對線路的電感和電容分析參與其中。我們假設這樣的線條使得導體電阻('R'')和介電電導('G'')可以忽略阻抗和傳播延遲的目的。這將是感興趣的實際頻率的情況。

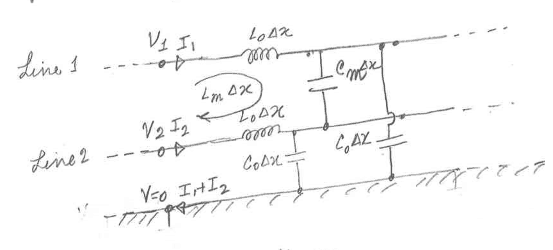

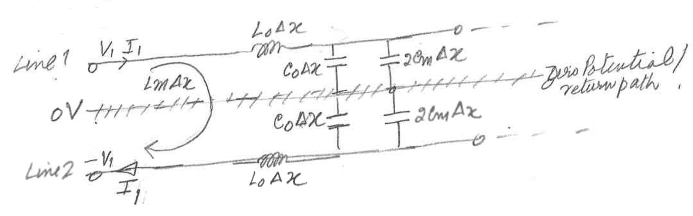

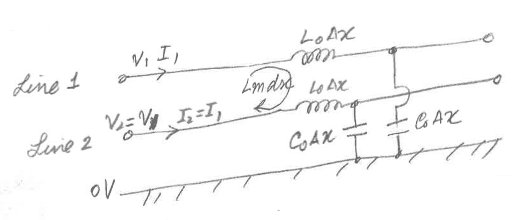

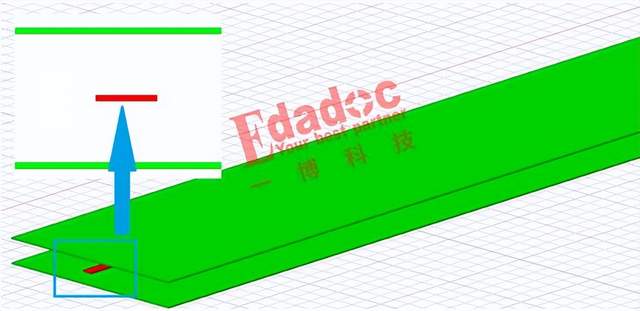

下圖給出了差分對線的無限小長度的電路模型:

這里'L0'和'C0'分別取決于每單位長度每條線的電感和電容。 'Lm'是第1行和第2行之間每單位長度的互感。'Cm'是第1行和第2行之間每單位長度的電容。

情況1:奇數模式(純差分信號)

這里'V2 = -V1'和'I2 = -I1'。因此,沒有電流在返回路徑中流動。 'Cm delta x'可以被認為是兩個電容器,每個電容器的值為“2Cm delta x”,其中心點為零電位。 (這是因為兩個相等電容之間的電位分壓。)因此,奇數模式下的等效電路變為:

讓我們來看看線路1(第2行情況完全相似)。

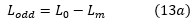

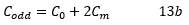

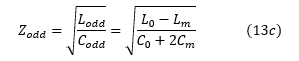

第1行的感應電壓由兩部分組成。一個歸因于'I',流過'L0 delta x'。另一個是由于'I2 = -I1',流過'Lm delta x'。這些可以等效地表示為由于'I',流過'(L0-Lm)delta x'。因此,奇數模式中線1的每單位長度的有效電感,由'Lodd'表示,將由下式給出:

有效電容在第1行和零電位線之間是'(C0 + 2Cm)delta x'。因此,每單位長度的奇模線電容是:

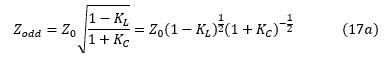

根據定義,類似于在單端線的情況下得到的結果,奇模特征阻抗由下式給出:

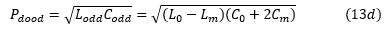

奇模信號的每單位長度傳播延遲由下式給出:

這是純單位信號差分部分的單位長度傳播延遲。此處還要記住的是,奇數模式或純差分信號的電磁波主要存在于兩條線之間的空間內和周圍。并且它們受參考或地平面的影響相對較小。

情況2:偶模式(純共模信號)

在這種情況下,'V2 = V1'并且由于該對中的兩行是相同的,'I1 = I2'。由于'V1 = V2',兩條線之間的電容'Cm'對兩條線中的電流沒有影響。因此可以忽略它,導致以下等效電路:

讓我們看一下第1行(第2行的情況相同)。

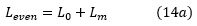

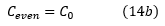

第1行的感應電壓將由'I1'貢獻,流入'L0 delta x'。并且通過'I2 = I1'',流入'Lm delta x'。這相當于說'I1'流過'(L0 + Lm)delta x'。因此,偶數模式下任一行的每單位長度的有效電感將為:

均勻模式下任一行的每單位長度有效電容將是:

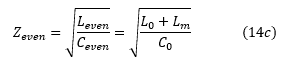

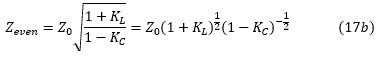

因此,任一行的偶模阻抗將由下式給出:

偶模信號的每單位長度的傳播延遲由下式給出:

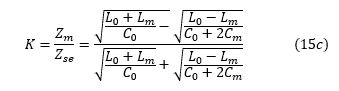

等式(13c)和(14c)清楚地表明' Zeven'比'Zodd'更重要。從理論上講,還知道'Lm'小于'L0','Cm'小于'C0'。

'Zse ','Zm'和'K'用'L0','C0','Lm','Cm'

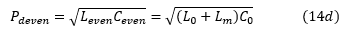

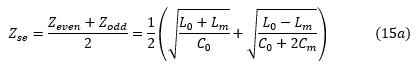

使用等式(12),(13)和(14) ),我們有:

關于'Zse'的一些詞

'Zse'是存在兩條線的任一條中的單端阻抗另一條線。當沒有第二條線時,它與單條線的單端阻抗不完全相同。第二條線的存在稍微降低了阻抗。兩條線越耦合(或越接近),'Zse'將變得更少。

重要的是要注意,如果兩條線之間的耦合是'Zse',則變化不大。不高。或者,如果我們可以使兩條線之間的間隔大于信號層和最近的地面/參考平面之間的導體寬度或介電高度的最大值。

。如果間隔大于信號層和最近參考平面之間的介電高度,則“Zse”相對相同。

此外,'Zse'不接近'L0/C0'但更接近'L0/(C0 + Cm)'。乍一看似乎令人驚訝,但情況確實如此。

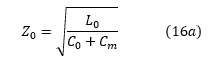

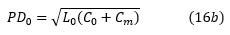

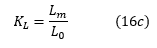

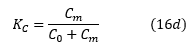

定義一些新術語并不合適:

'KL'和'KC'可以分別稱為電感和電容耦合系數。使用這些,我們可以將等式(15)寫成:

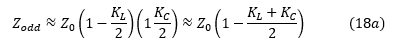

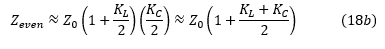

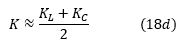

自'KL'和'KC'小于1,并且對于大多數實際案例將明顯小于1,我們只能保留一階項,以便:

如果我們將方程(18a)與(8a)和(18b)與(10a)進行比較,很容易得出結論:

并且:

值得一提的是,在大多數帶狀線差分對的實際情況中,歸納如果信號層上方和下方的PCB材料的介電常數幾乎相等,則耦合系數'KL'和電容耦合系數'KC'幾乎相等。

兩個串擾相關參數

在這里,我們還要定義另外兩個參數,NEXT和FEXT:

NEXT被稱為最近的串擾系數。 FEXT稱為遠端串擾系數。這些參數在串擾分析中是重要的,當兩條附近的線路中,一條是主信號線而另一條線是安靜的線路,我們希望在該線路上確定由于主線路上的信號電壓而引起的串擾電壓。我們將在下一篇關于串擾分析的文章中詳細闡述這一點。

-

pcb

+關注

關注

4404文章

23877瀏覽量

424222 -

線路板

+關注

關注

24文章

1323瀏覽量

49854 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44637 -

華秋DFM

+關注

關注

20文章

3515瀏覽量

6393

發布評論請先 登錄

鋰電池嵌入電極顆粒的傳輸線法TLM 模擬研究

基于改進傳輸線法(TLM)的金屬 - 氧化鋅半導體界面電阻分析

USB 差分信號線 PCB 布線指南

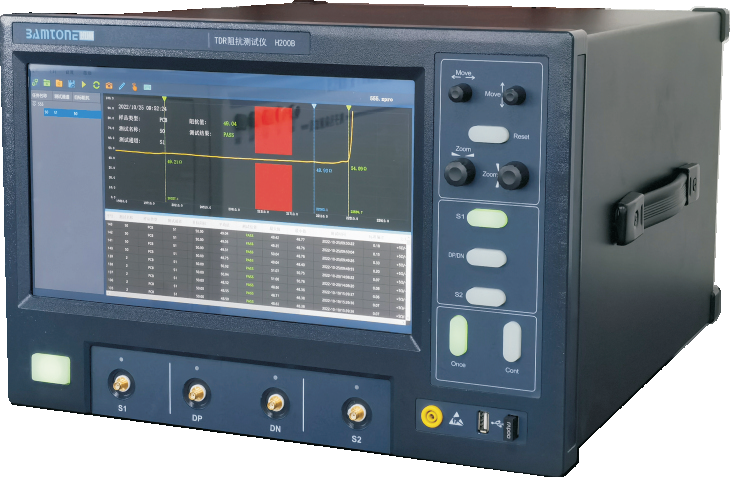

如何用TDR阻抗測量儀快速定位PCB傳輸線故障?

Allegro Skill布線功能-添加差分過孔禁布區

PCB傳輸線中的差分對是怎樣的一情況

PCB傳輸線中的差分對是怎樣的一情況

評論