1、在做 PCB 設計時,為了滿足某一組所有信號線的總長度滿足在一個公差范圍內,通常要使用蛇形走線將總長度較短的信號線繞到與組內最長的信號線長度公差范圍內,這個用蛇形走線繞長信號線的處理過程,就是我們俗稱的 PCB 信號等長處理。等長的目標是為了滿足同組信號的時序匹配要求。

2、等長范圍應嚴格遵守不同接口或者信號的要求,具體的可參考模塊規范內容。如若有疑問,及時與客戶進行確認。

3、處理等長之前應先把同組內線長最長的信號線找到,第一步優化最長信號的長度。

4、等長處理完后應對整根信號線路徑進行檢查,檢查其是否避開干擾源,檢查其是否合格。

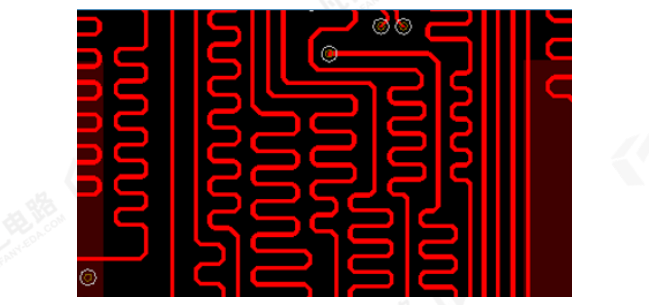

5、等長處理時,間距優選4W,如空間受限,可調整到3W;等長高度控制在40-150mil為宜,不能過高;轉角長度不小于線寬的1.5倍,一般控制在6-10mil大小,如線寬4mil,轉角大小控制在6mil,轉角不能太小,如圖1所示。

圖1 蛇形走線的要求

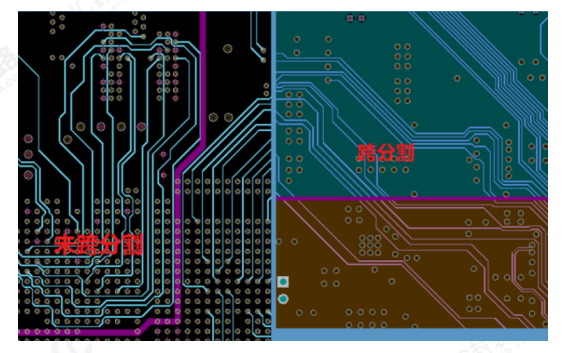

6、等長應盡量處理在水平或豎直方向上,避免處理在斜線上;處理不能太過散亂,應盡量集中處理,保證其美觀性,原則上是處理完一根信號后,第二根先修線挨到其旁邊,再對第二根進行等長處理,以保證空間的利用率及整體設計美觀性。同一設計內,等長的高度應控制差不多相同,不要相差太多,如圖2。

圖2 PCB的蛇形咬合等長

7、處理完等長后,應檢查其參考層情況,不允許其跨分割。PCB上時鐘信號(一般以clk結尾)等重要信號也要避免跨分割情況出現,跨分割后會導致信號阻抗突變。

圖3 PCB布線夸分割

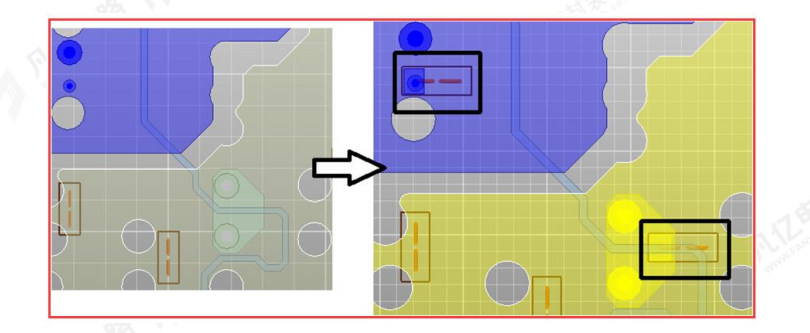

8、當走線的參考平面有跨電源層時,建議在2個電源層分別加對地電容以提供完整的回流路徑,如圖4所示。

圖4 走線夸分割處理

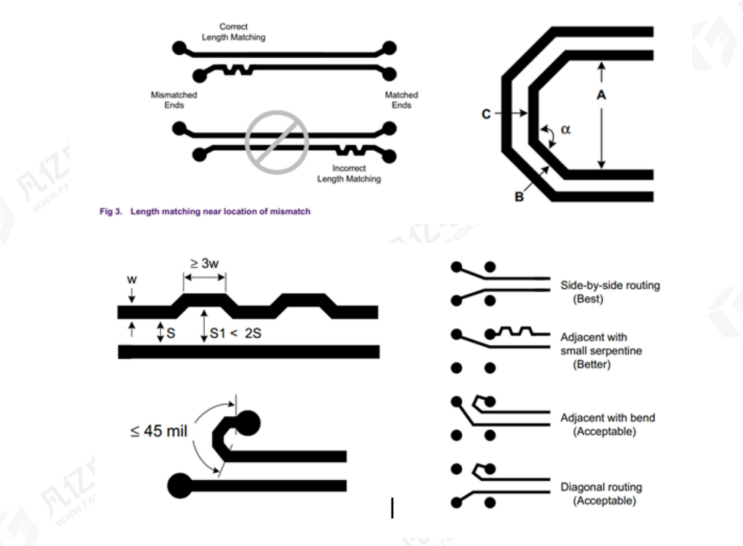

9、差分信號對內等長位置應在不耦合產生的位置附近進行等長,對內等長高度及寬度參考下圖5示要求。

圖5 差分線的等長要求

審核編輯 黃宇

-

PCB設計

+關注

關注

396文章

4933瀏覽量

95652 -

走線

+關注

關注

3文章

120瀏覽量

24649

發布評論請先 登錄

PCB設計中DDR布線要求及繞等長要求

高速PCB設計常見問題

AD9446 LVDS信號線的PCB走線的差分對間等長有沒有要求?

pcb開窗怎么設計_PCB設計怎樣設置走線開窗

PCB設計中常見的走線等長要求

PCB設計中常見的走線等長要求

評論