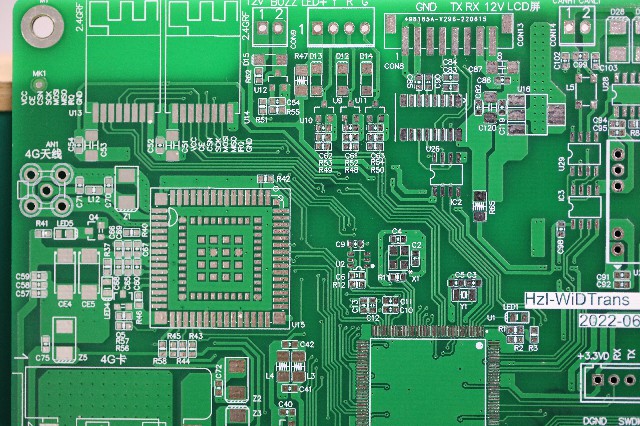

為了避免不理想返回路徑的影響,可以采用差分對走線。為了獲得較好的信號完整性,可以選用差分對來對高速信號進行走線,如圖1所示,LVDS電平的傳輸就采用差分傳輸線的方式。

圖1 差分對走線實例

差分信號傳輸有很多優點,如:

· 輸出驅動總的dI/dr會大幅降低,從而減小了軌道塌陷和潛在的電磁干擾;

· 差分信號在一對緊耦合差分對中傳輸時,在返回路徑中對付串擾和突變的魯棒性更好;

· 因為每個信號都有自己的返回路徑,所以差分新信號通過接插件或封裝時,不易受

到開關噪聲的干擾;

但是差分信號也有其缺點:首先是會產生潛在的EMI,如果不對差分信號進行恰當的平衡或濾波,或者存在任何共模信號,就可能會產生EMI問題;其次是和單端信號相比,傳輸差分信號需要雙倍的信號線。

如圖2所示為差分對走線在PCB上的橫截面。D為兩個差分對之間的距離;s為差分對兩根信號線間的距離;W為差分對走線的寬度;Ff為介質厚度。

使用差分對走線時,要遵循以下原則:

· 保持差分對的兩信號走線之間的距離S在整個走線上為常數;

· 確保D>25,以最小化兩個差分對信號之間的串擾;

· 使差分對的兩信號走線之間的距離S滿足:S=3H,以便使元件的反射阻抗最小化;

· 將兩差分信號線的長度保持相等,以消除信號的相位差;

· 避免在差分對上使用多個過孔,過孔會產生阻抗不匹配和電感。

圖2 PCB上的差分對走線

以前,只有不到50%的電路板采用可控阻抗互連線,而現在這一比例已超過90%。如今有不到50%的電路板使用了差分對,相信在不久的將來,隨著對差分對原理和設計規則的了解加深,將會有超過90%的電路板使用它

-

pcb

+關注

關注

4404文章

23877瀏覽量

424241 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44637

發布評論請先 登錄

高速PCB諧振威力,不容小覷

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

高速線設備和包帶工藝介紹

別蒙我,PCB板上這幾對高速走線怎么看我都覺得一樣!

Allegro Skill布線功能-添加差分過孔禁布區

高速pcb差分對走線應該怎樣來設計

高速pcb差分對走線應該怎樣來設計

評論