在PCB設計中,差分對的走線操作是一項關鍵任務,它直接影響到信號的完整性和電路的性能。差分信號通常用于高速數字通信,因為它們能夠有效地抵抗電磁干擾和提供準確的時序信號。以下是對如何進行PCB差分對走線操作的詳細指導。

理解差分信號的基本概念

差分信號由一對等幅值、反相信號的信號組成,這兩個信號通過兩根導線傳輸。在接收端,通過比較這兩個信號的差值來恢復原始信號。差分信號的主要優點包括強大的抗干擾能力和精確的時序定位。

設計前的準備工作

1.確定差分對的阻抗要求 :根據信號的類型和傳輸速率,確定差分對的阻抗值。常見的差分阻抗值有50歐姆、75歐姆、100歐姆等。

2.選擇合適的PCB材料和層疊結構 :PCB的材料和層疊結構會影響信號的傳輸特性。選擇具有適當介電常數和損耗因子的材料,以及合適的層疊結構,可以優化信號的傳輸性能。

3.設計規則檢查(DRC)設置 :在開始走線之前,應該設置好相關的設計規則,包括走線寬度、間距、過孔大小等,以確保走線滿足設計要求。

差分對走線的基本原則

1.等長 :為了保持差分信號的完整性,兩根差分信號線的長度應該盡可能相等。長度差異會導致信號的時序錯誤和失真。

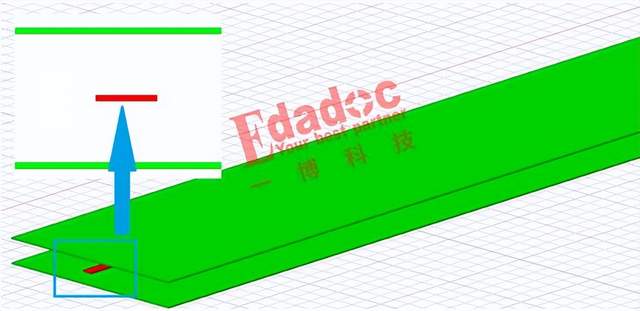

2.等寬和等距 :差分信號線的寬度和間距應該保持一致,以確保阻抗的連續性和信號的平衡。

3.緊密耦合 :差分信號線應該緊密地并排走線,以增強它們之間的磁場耦合,這有助于抵消外部干擾。

4.避免交叉和銳角 :在走線過程中,應避免差分線之間的交叉和銳角轉彎,這些都會破壞信號的平衡和對稱性。

差分對走線的具體步驟

1.創建差分對網絡 :在PCB設計軟件中,首先需要定義差分對網絡。這通常涉及到設置差分對的名稱和包含的網絡。

2.設置差分對規則 :在設計規則中,設置差分對的特定規則,如走線寬度、間距、過孔大小等。

3.開始走線 :使用差分對布線工具開始走線。在布線過程中,軟件會實時顯示布線長度和差異,確保兩根線的長度盡可能相等。

4.調整走線 :在布線過程中,可能需要根據PCB的空間布局和其他設計要求進行調整。使用軟件的編輯工具來優化走線路徑和形狀。

5.檢查和優化 :完成走線后,使用設計規則檢查工具來檢查差分對是否滿足所有設計要求。對于不符合要求的部分,進行必要的優化。

高級技巧和注意事項

1.阻抗匹配 :確保差分對的阻抗在整個傳輸路徑上保持一致,包括走線、過孔、連接器等。

2.屏蔽和接地 :如果可能,為差分對提供屏蔽層,并在接收端正確接地,以進一步減少干擾。

3.熱管理 :考慮PCB的熱管理,確保差分對不會因為過熱而影響性能。

4.信號完整性分析 :在設計過程中,可以使用信號完整性分析工具來預測和評估差分對的性能。

結論

差分對的走線操作是PCB設計中的一項重要任務,需要遵循一系列的原則和步驟。通過精心的設計和優化,可以確保差分信號在高速數字通信中的可靠性和性能。在設計過程中,應該密切關注等長、等寬、等距和阻抗匹配等關鍵因素,以及使用高級分析工具來驗證設計的性能。通過這些方法,可以有效地提高PCB設計的質量和產品的市場競爭力。

-

PCB設計

+關注

關注

396文章

4921瀏覽量

95305 -

信號完整性

+關注

關注

68文章

1486瀏覽量

98115 -

電磁干擾

+關注

關注

36文章

2483瀏覽量

107947 -

差分走線

+關注

關注

0文章

33瀏覽量

13132 -

差分對

+關注

關注

0文章

10瀏覽量

7038

發布評論請先 登錄

如何對PCB進行差分對的走線操作呢?

如何對PCB進行差分對的走線操作呢?

評論