PCB高速差分布線路圖實踐

- 耦合電容器(10597)

- 差分器件(6222)

相關推薦

熱點推薦

如何實現高速時鐘信號的差分布線

如何實現高速時鐘信號的差分布線

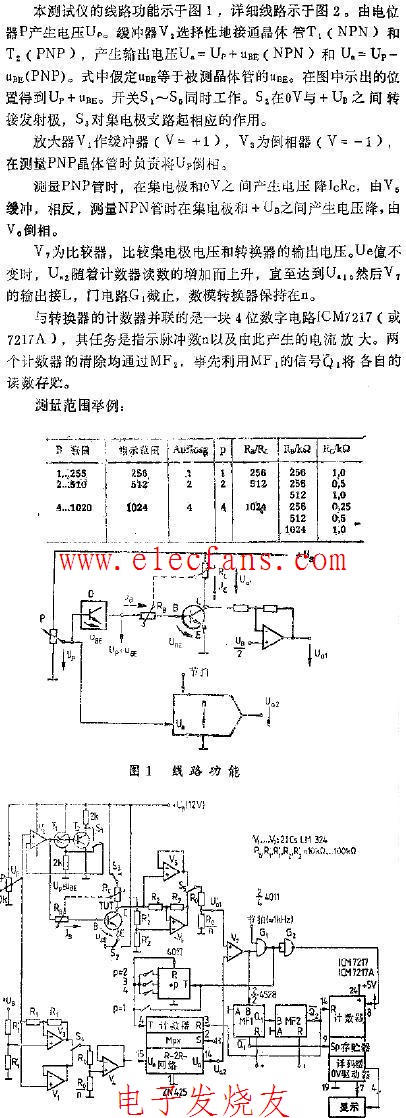

在高速設計中,如何解決信號的完整性問題?差分布線方式是如何實現的?對于只有一個輸出端的時鐘信號線,如何實現差分布線?

2009-04-15 00:26:37 3623

3623

3623

3623高速PCB布線實踐指南詳細介紹(例題分析)

高速PCB布線實踐指南詳細介紹(例題分析)

雖然印制電路板(PCB)布線在高速電路中具有關鍵的作用,但它往往是電路設計過程的最后幾個步驟之一。高速PCB布線有很多

2009-12-04 09:30:59 1006

1006

1006

1006高速電路PCB電源布線技巧

高速電路PCB電源布線技巧

PCB設計來說電源處理好壞直接關系到整個電路板的性能。下面我們分析一下高速電路PCB板的電源布線需要注意的地方和技

2010-03-21 18:29:39 3110

3110

3110

3110

高速PCB布線實踐指南

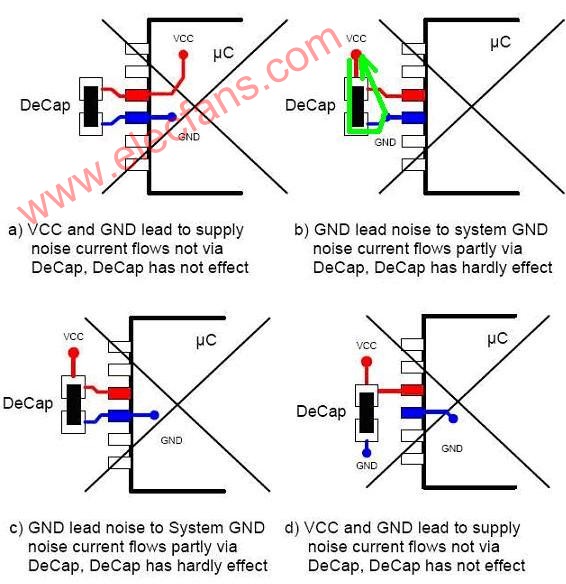

高整電路板在PCB布局時需要非常注意,稍不細心,就可能帶來電磁兼容以及干擾的問題。現在給大家介紹一些實用的布線指南。

印制電路板(PCB)布線在高

2010-12-31 18:49:15 10402

10402

10402

10402

高速PCB布局/布線的原則

層三、網格中添加過孔避免熱點四、路由高速信號135°走線彎曲五、增加瓶頸區域外的線距離六、增加菊花鏈路(避免長存根)七、差分布線原則八、正和負信號間的緊密延遲偏差

2025-05-28 19:34:36 2044

2044

2044

2044

PCB線路板關鍵信號如何去布線

要求卻可以減少高速信號對外的發射和相互間的耦合,減少信號的輻射和反射。 3. 引線越短越好 高速信號布線電路器件管腳間的引線越短越好。線路板引線越長,帶來的分布電感和分布電容值越大,對系統的高頻

2022-11-07 20:44:08

PCB設計高速差分信號的布線技巧

在pcb上靠近平行走高速差分信號線對的時候,在阻抗匹配的情況下,由于兩線的相互耦合,會帶來很多好處。但是有觀點認為這樣會增大信號的衰減,影響傳輸距離,為什么?我在一些大公司的評估板上看到高速布線有的

2012-03-03 12:37:52

PCB設計百問百答(1)——差分線路

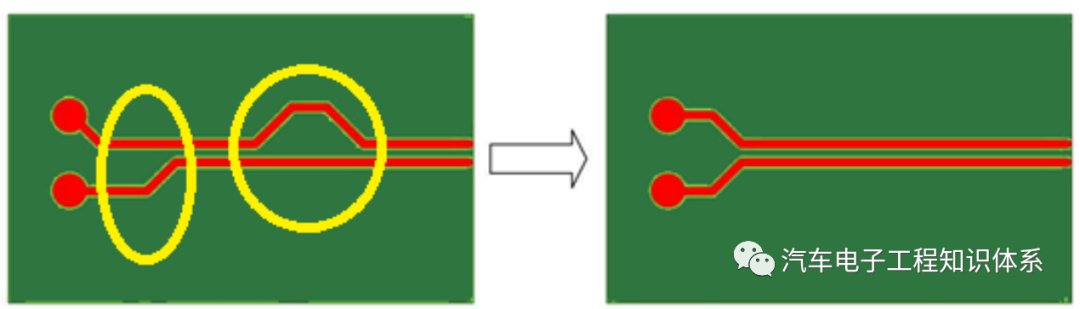

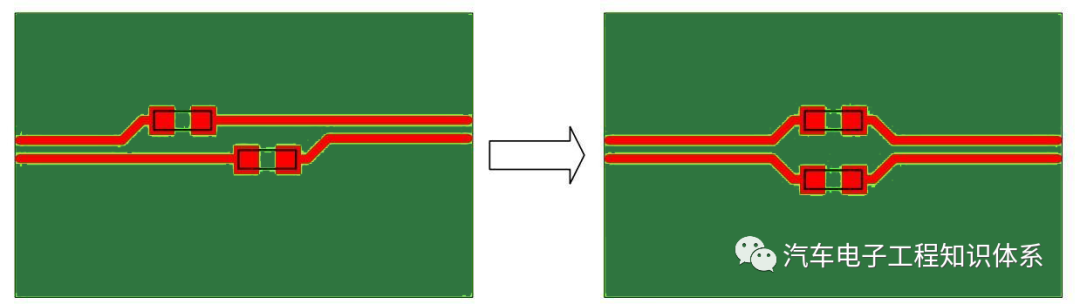

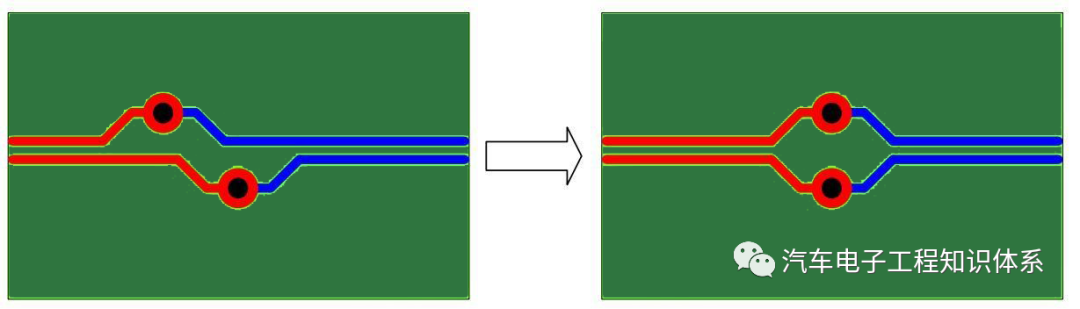

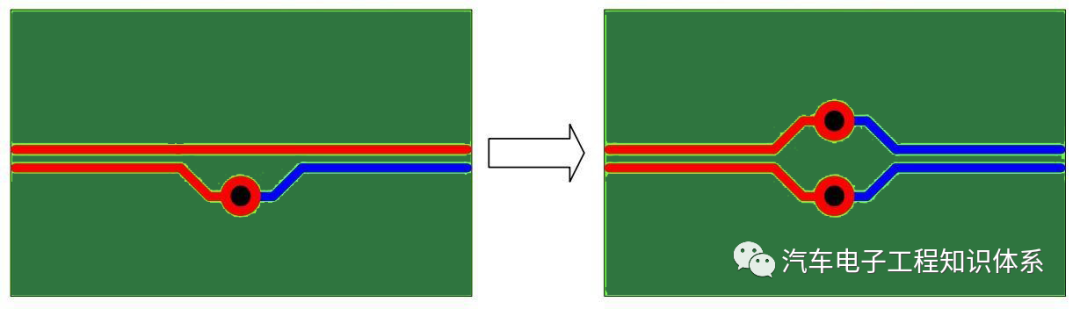

分布線方式是如何實現的? 差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩 種,一為兩條線走在同一走線層

2015-01-09 11:14:05

高速PCB布線技巧、EMI問題、設計規則

信號的特性阻抗連續規則高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。規則五、高速PCB設計的布線方向規則

2021-03-31 06:00:00

高速PCB布線技巧、EMI問題、設計規則

,不同層的走線阻抗必須連續。規則五、高速PCB設計的布線方向規則 相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串擾,增加EMI輻射。 簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以

2022-04-18 15:22:08

高速PCB信號布線的設計規范

一系列阻抗問題。 高速設計的另一個關鍵領域是差分對的布線。差分對通過以互補的方式驅動兩個信號跡線來操作。差分對提供出色的抗噪聲能力和更高的S / N比。然而,實現這些優勢有兩個限制: 1、兩條走線

2023-04-12 15:20:37

高速PCB電路板信號完整性設計之布線技巧

在高速PCB電路板的設計和制造過程中,工程師需要從布線、元件設置等方面入手,以確保這一PCB板具有良好的信號傳輸完整性。在今天的文章中,我們將會為各位新人工程師們介紹PCB信號完整性設計中常

2018-11-27 09:57:50

高速PCB設計中布線基本要求

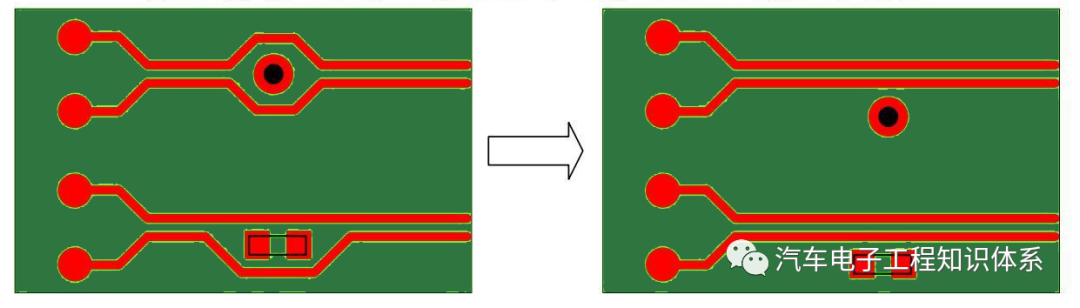

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-02-16 15:06:01

高速PCB設計中布線基本要求

` 本帖最后由 飛翔的烏龜005 于 2017-2-10 10:43 編輯

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用

2017-02-10 10:42:11

AD差分布線的方法

AD差分布線的方法,學習下推薦課程:課程名稱:PCB電磁兼容設計案例分析與仿真解析課程鏈接:http://url.elecfans.com/u/05942d9ef

2019-01-24 16:42:20

USB PCB設計建議和差分布線的原則

為了保證良好的信號質量, USB 2.0 端口數據信號線按照差分線方式走線。為了達到USB 2.0 高速 480MHz 的速度要求,建議 PCB 布線設計采用以下原則:差分數據線走線盡可能短、直,差分數據線對內走線長度嚴格等長,走線長度偏差控制在±5mil 以內。

2019-05-23 08:52:33

【轉發】[國外經驗分享]高速PCB布線實踐指南

在發此帖的同時首先要感謝原帖的作者:tanke所發的好東西[國外經驗分享]高速PCB布線實踐指南 https://bbs.elecfans.com/forum.ph ... 9442&

2013-01-13 17:06:17

不能差分布線

新人,第一次用allegro,在pcb editor里布線,設置了差分對規則,返回布線的時候,選中差分對其中的一個引腳布線,但是只拉出來了一根線,右鍵里也沒有單根走線模式可選。求解。。。。。。

2015-04-15 17:38:54

從實踐角度來探討高速電路布線問題

的可能性降至最低。需要給布線工程師的指示包括:電路功能的簡短描述?標明輸入和輸出位置的PCB略圖?PCB層疊信息?各層需要那些信號?要求重要元件的放置位置?旁路元件的確切位置?哪些印制線很重要?哪些線路

2019-12-16 09:21:50

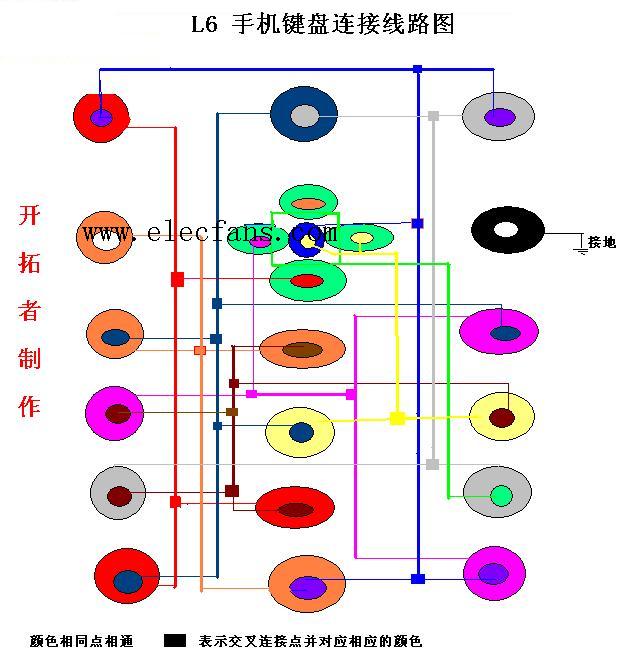

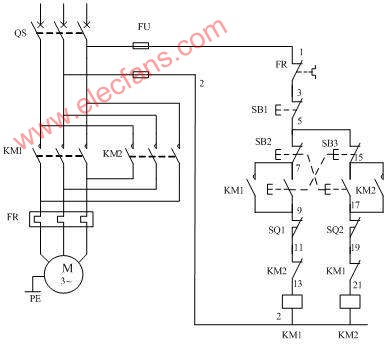

電機控制基礎線路圖大全

電機控制基礎線路圖大全脫光隨便看有圖有真相推薦課程:張飛軟硬開源:基于STM32的BLDC直流無刷電機驅動器(視頻+硬件)http://url.elecfans.com/u/73ad899cfd

2016-01-14 13:58:27

誰有服務器方面的線路圖和PCB設計相關的資料分享,萬分感謝

各位大神,誰有服務器方面的線路圖和PCB設計相關的資料分享,萬分感謝。如果滿意一定重謝。知識付費我還是懂的得。謝謝了。

2021-08-24 18:49:06

PCB | 高速BGA 封裝與PCB 差分互連結構的設計與優化

本文通過對高速BGA封裝與PCB差分互連結構的優化設計,利用CST全波電磁場仿真軟件進行3D建模,分別研究了差分布線方式、信號布局方式、信號孔/地孔比、布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串擾的具體影響。

2019-05-29 15:14:34 5060

5060

5060

5060AMD公布GPU發展的線路圖

按照傳統,AMD今天向金融分析師公布了GPU發展的線路圖。線路圖中不僅包含了去年夏天發布的Radeon RX 5700 XT RDNA,范圍還涵蓋了RDNA 2以及RDNA 3。

2020-03-06 14:59:31 3345

3345

3345

3345高速PCB布線的最佳技巧

在布線電路板時, PCB 設計人員的任務很艱巨。當涉及到高速 PCB 布線和信號時,事情就變得更加復雜。為了幫助不同的 PCB 設計人員,已列出了一系列最佳的高速 PCB 布線實踐,以幫助他們實現

2020-10-27 19:12:24 3638

3638

3638

3638PCB板差分布線操作技巧

高速串行總線的普及,使得PCB板上差分信號越來越多,那么,PCB板如何差分布線? 各類差分線的阻抗要求不同,根據設計要求,通過阻抗計算軟件計算出差分阻抗和對應的線 寬間距,并設置到約束管理器。 差

2020-12-04 11:14:51 9659

9659

9659

9659高速PCB之布線問題探討

雖然印刷電路板(PCB)布線在高速電路中具有關鍵的作用,但它往往只是電路設計過程的最后幾個步驟之一。高速PCB布線有很多方面的問題,關于這個主題已有大量的文獻可供參考。本文主要從實踐的角度來探討高速

2021-06-21 10:58:05 0

0

0

0高速BGA封裝與PCB差分互連結構設計

針對高速BGA封裝與PCB差分互連結構進行設計與優化,著重分析封裝與PCB互連區域差分布線方式,信號布局方式,信號孔/地孔比,布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串擾的具體影響。

2022-08-26 16:32:04 1161

1161

1161

1161高速PCB布線實踐指南介紹

本文主要從實踐的角度來探討高速電路的布線問題。主要目的

在于幫助新用戶當設計高速電路 PCB 布線時對需要考慮的多

種不同問題引起注意。

2022-10-21 16:09:05 0

0

0

0PCB設計差分布線要求及操作技巧

一站式PCBA智造廠家今天為大家講講PCB設計差分布線有什么要求?PCB設計差分布線要求及操作技巧。高速串行總線的普及,使得PCB板上差分信號越來越多,那么,PCB設計如何進行差分布線呢?接下來

2023-07-07 09:25:21 7692

7692

7692

7692

電子發燒友App

電子發燒友App

評論