本例程詳細介紹了如何在FPGA上實現Serial RapidIO(SRIO)通信協議,并通過Verilog語言進行編程設計。SRIO作為一種高速、低延遲的串行互連技術,在高性能計算和嵌入式系統中廣

2025-11-12 14:38:17 5408

5408

Altera公司 (NASDAQ: ALTR)今天宣布,其28 nm Stratix? V GX FPGA已經收錄在最新的PCI-SIG? Integrators名錄中,符合PCI Express? (PCIe?) 3.0規范(Gen3)要求。

2013-05-23 10:34:54 2165

2165 1. CvP 簡介 CvP(Configuration via Protocol)是一種通過協議實現 FPGA 配置的方案,Arria V,Cyclone V,Stratix V,Arria 10

2020-11-27 14:06:41 6627

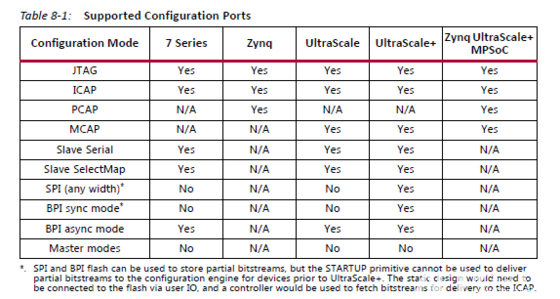

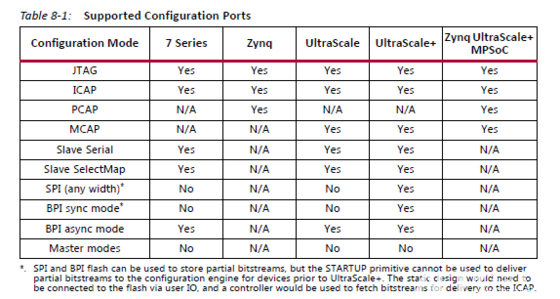

6627 芯片才能實現,具體哪些系列能實現哪種配置方式如下圖所示: 圖1 本質上來說,無論是JTAG還是ICAP或者MCAP以及其它FPGA的配置方式,目的都是配置FPGA的邏輯。MCAP是通過PCIE來實現

2021-01-03 09:20:00 5347

5347

鎖存器是個“奇葩”的器件,在FPGA邏輯設計中很避諱;在ASIC設計中,以前很喜歡(因為面積小),現在不是很喜歡了。在這里就記錄一下關于鎖存器的一些事項吧。

2022-03-15 17:34:00 7793

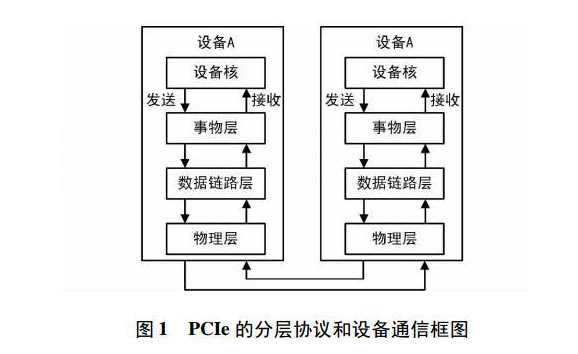

7793 本文我們將向大家介紹PCIe引腳定義以及PCIe協議層。

2023-09-26 11:39:14 25802

25802

嗨,我正在嘗試使用KC705板進行PCIE RC和端點測試。1)我將把PCIE RC控制器IP設計和FPGA PCIE PHY放在FPGA中。2)我將在FPGA中放置另一個PCIE端點控制器IP

2020-07-26 13:06:25

6678的pcie和fpga的pcie? TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

?

2018-06-21 15:49:12

寫在前面SPI協議系列文章:FPGA實現的SPI協議(一)----SPI驅動 在上篇文章,簡要介紹了SPI協議,編寫了SPI協議的FPGA驅動,但是在驗證環節,僅僅驗證了發送時序,而沒有與從機進行

2022-02-17 06:03:44

1.單單用FPGA來實現路由、MAC層協議是有可能的嗎?實現的主要困難在哪里?2.之前問過別人協議涉及大量變量,FPGA無法單獨完成,需要ARM的配合,那么如果用FPGA+ARM框架來聯合實現的復雜度大嗎?3.可不可以直接用Power PC來實現?

2018-07-25 17:49:53

TCP/IP協議:TCP/IP協議是Internet上使用的主要協議之一,它定義了數據在網絡中的傳輸方式和處理方式。FPGA可以通過實現TCP/IP協議棧來支持TCP/IP通信。PCIe協議:PCI

2023-03-27 09:01:46

我畢設需要做一個賽靈思的FPGA輸入高速信號到PCIE口,但是速率過高不能直接接入,所以買了貴公司的CH368,但是不知道FPGA和CH368之間應該怎么實現通信,有沒有verilog的例程可以參考,CH368是UART口還是普通串口呢?謝謝了!

2022-10-10 07:10:28

FPGA上的PCIe接口應用是一個復雜的任務,需要考慮多個方面的問題以確保系統的穩定性和性能。以下是在FPGA的PCIe接口應用中需要注意的關鍵問題:

硬件資源和內部架構 :

FPGA的型號和尺寸

2024-05-27 16:17:41

開發環境:windows開發平臺:QT5.11.31.PCIE上位機測試過程FPGA將數據傳到芯片中,通過pcie再將芯片算完的數傳給上位機。目標:1.實現上位機的速度測試,經測試pcie的傳輸速度

2019-12-26 10:27:19

開發環境:windows開發平臺:QT5.11.31、PCIE上位機測試過程FPGA將數據傳到芯片中,通過pcie再將芯片算完的數傳給上位機。目標:1.實現上位機的速度測試,經測試pcie的傳輸速度

2022-01-13 16:44:54

`PCIE總線的FPGA設計方法`

2015-10-30 14:30:52

本文檔旨在提供關于將PCIe接口集成到基于AMBA的片上系統(SoC)的指導。

假設PCIe接口通過基于AXI或ACE協議的互連連接到SoC的其余部分。

讀者應熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

場景:監測GPU與主機之間的PCIe通信,分析數據傳輸效率、延遲和帶寬利用率。

應用價值:優化大規模AI訓練任務的數據加載和模型參數同步,例如在多GPU系統中測試PCIe交換機的性能和穩定性。

FPGA

2025-07-25 14:09:01

大家好,我我想請問一下,在FPGA中怎樣用verilog來編寫通信協議的程序?它的步驟是怎樣的?剛接觸FPGA,好多不懂的,希望大神指點一二。。。

2014-12-06 21:19:02

功能,1、FPGA是不是可以直接通過PCIE操作DDR完成DMA操作?2、在操作過程中CPU是一個旁觀者的角色嗎?3、地址轉換,DDR接口操作等都是由CPU內部的硬件完成?CPU在FPGA操作DDR的過程中,完全不受影響的工作嗎?多謝!

2016-04-06 16:24:36

\drv\exampleProjects\PCIE_exampleProject 里面的例子

這個工程可以成功跑起來,并且在PC端通過用WinDriver可以看到設備,但是目前有一個關于例程中BAR配置

2018-06-19 00:50:13

本人想問下,FPGA的介紹中有些事說帶有PCIe硬核的,那么這個FPGA直接購買后就可以使用這個硬核完成PCIE功能了嗎?不再需要購買其他什么許可文件之類的東西了嗎? 這點不是很清楚,順便問一下帶有這中硬核的FPGA大概要多少錢呢?

2012-12-12 17:52:08

FPGA pcie dma測試

流程:金手指和電腦連接之后,先加載程序,pc重啟;

現象:pc無法開機。

FPGA pcie x8,pc x16,直接連接上去的

請問這是什么情況呀,為什么電腦開不了機呢?

2023-09-13 18:21:28

編碼后傳到FPGA中,接著利用FPGA進行信道編碼,再通過模擬調制,再發送。那么,我想問下通信協議在這里的作用是什么?或者說,如果我們想使用wifi協議,我們該如何應用wifi協議指導我們的設計?硬件

2015-01-27 18:15:35

關于這幾個協議的實現,可以看下下面的文章,其中UART中詳細介紹了RS232和UART區別。一天一個設計實例-3萬字講解UART和實例一天一個設計實例-IIC協議及FPGA實現一天一個設計實例-SPI

2022-08-19 16:32:22

查過mini pcie的信號引腳定義,有52個信號(大多引腳無用),X1 LANE 的情況,查看飛思卡爾或INTEL處理器的設計資料,關于這個應用除了主要 的差分收、發和差分時鐘信號之外還需要額外

2017-11-29 11:50:51

FPGA(資源夠用)都可以以soft IP形式實現FPGA嗎?4.個人覺得使用Megwizard和Qsys中的IP就可以實現PCIE功能了,那么什么樣的設計還需要加專用的協議芯片呢?謝謝!

2015-07-27 11:05:46

FPGA實現 PCIE 端點設備,我該如何實現這樣一個功能,PC發送一條消息(比如一個存儲器寫事務),然后FPGA用戶邏輯獲得這個事務包里的內容進行相關操作,比如把一個LED點亮。已知在設計例程中

2016-03-12 10:48:22

項目名稱:FPGA PCIe信號拆分應用領域:計算機參賽計劃:利用FPGA的并行資源,實現在不使用plx硬核芯片的情況下對PCIe信號的拆分。具體有效帶寬視開發板資源而定。使用FPGA相較于使用硬核

2021-05-12 18:05:46

技術,主要支持一致性緩存,內存和IO擴展。CXL是基于PCIe 5.0實現的連接技術,復用了很多PCIe協議的東西,這一點上與CCIX比較像,但又不完全一樣。說起CCIX和CXL,難免要相互對比。其實

2022-09-09 15:03:06

串行總線協議PCIe、ASI和sRIO之間有什么不同?

2021-05-25 07:05:09

,那就很容易把pcie協議理解徹透徹,當然這里狹義指的是上層交互的TLP協議,數據鏈路層和物理層更復雜的事情是硬核做的,用起來PCIE并不需要深入了解。

如何使用紫光PCIE,首先FPGA端需要一個

2023-11-17 14:35:30

你好,先生或女士我是中國學生。我已經研究FPGA一段時間了,我正在嘗試使用FPGA來實現FC協議。經過一番研究,我發現GTH可以達到FC1。但是我發現使用7系列FPGA收發器向導IP存在一些問題。我

2020-08-17 10:28:07

嗨!我正在研究的溝通鏈如下:PC-PCIe- 光纖與sfp +-FPGA高數據吞吐量(10Gbps)是從FPGA到PC的。我應該使用什么協議?謝謝!以上來自于谷歌翻譯以下為原文Hi

2019-02-26 09:50:19

1、在FPGA中實現串口協議的設計在FPGA中實現串口協議,通過Anlogic_FPGA開發板上的“UART2USB”口接收從計算機發來的數據。實驗設計思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

作者:王毅 管會生 劉斌彬 梅順良引言本文采用FPGA實現了IDE硬盤接口協議。系統提供兩套符合ATA-6規范的IDE接口,一個與普通IDE硬盤連接,另一個與計算機主板上的IDE接口相連。系統采用

2019-04-18 07:00:10

,基于ARINC664規范第7部分,提出符合該規范的基于FPGA的AFDX端系統協議芯片和相應AFDX端系統板卡的設計方案,并給出關鍵模塊的具體實現;通過對端系統協議芯片進行測試驗證,證明該端系統協議芯片

2010-05-13 09:09:08

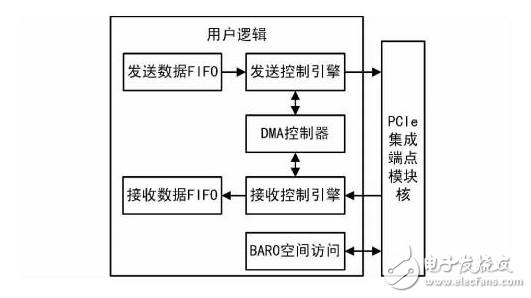

PCIe總線通信過程是怎樣的?是什么原理?如何利用PCIe DMA總線實現一個基于FPGA的PCIe 8位數據采集卡?

2021-09-17 07:16:03

嗨,我正在使用超大規模的FPGA板。我可以通過DMA子系統IP和DDR控制器IP將數據從PC傳輸到DDR。我打算在FPGA中進行一些處理,然后更新數據,以便PC可以讀取。如何通過PCIe指示PC處理

2020-05-08 09:40:04

IDE接口協議簡介用FPGA實現接口協議的方法介紹

2021-04-08 06:39:49

只有一個)。在我的設計中,我已經將FMC HPC連接器用于其他目的,我想知道我是否可以將PCIe中的MGT用于RapidIO協議,或者這個接口僅用于PCIe?提前致謝。

2019-08-29 10:33:02

一塊帶有PCIE接口的FPGA,一塊PCIE轉USB3.0板卡,想通過FPGA控制PCIE轉USB3.0板卡,實現USB3.0讀入數據,經過FPGA高速處理,不需要經過電腦CPU。請問各位專家:1.

2014-12-25 22:54:58

本人現在在做一個PCIE接口的數據采集系統,下位機是FPGA,上位機是PC,調用的Xilinx的PCIE核,DMA傳輸。現在需要在數據緩存到一定程度時(這個時候是知道的)由FPGA產生一個中斷信號通知上位機接收數據。但是不知該如何產生使用這個中斷信號,求大神幫忙解答一下,謝謝!

2016-07-19 20:04:36

/pcie-ti81xx中的代碼,使用了函數platform_get_resource_byname(),這個函數是否和我想實現的功能有關?我在PCIe.c中加

2018-05-28 01:52:49

嗨,我將從一個新項目開始。它涉及使用FPGA和GP / GPU加速PCIe板,這些板將被添加到常規計算機或服務器中。 GPU將是NVIDIA特斯拉。 FPGA板......還有待選擇。我確實看到了

2019-01-24 10:55:48

bit)是關于PCIe的5個問題,這些只要按要求去做就行了。但我們在網上看到有人講:多片C6678通過PCIe互聯通信時,發現C6678在多個方面與PCIe協議不一致!是真的嗎?如果是這樣,不但C6678

2018-08-03 08:16:10

傳輸速率是根據PCIE的協議制定的嗎?2.如果我設置的速率超過5.0Gbps可以嗎?是否會出現數據的傳輸錯誤等現象?3.不太理解PCIE中關于x1和x2的含義,文檔說PCIE是one single interface link,那么對于單個端口而言,x2的含義僅僅是代表速率是x1速率的一倍嗎?

2018-06-19 04:36:26

親關于如何使用GTX生成PIPE接口PCIE PHY的以下主題,有沒有人有答案?https://forums.xilinx.com/t5/7-Series-FPGA

2020-05-04 09:05:44

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 編輯

你好!我目前正在實現6657DSP 評估板與xilinx kintex7 FPGA之間的PCIE連接,其中DSP作為Root

2018-06-25 05:14:40

請問,那里能找到關于在FPGA中實現DDC中分數倍重采樣的資料?不是指用CIC實現,而是基于多相的結構實現。

2020-07-30 16:50:07

系列FPGA實現PCIe接口所涉及的硬件板卡參數、應用層系統方案、DMA仲裁、PCIe硬核配置與讀寫時序等內容。

2019-05-21 09:12:26

PCI總線協議的FPGA實現及驅動設計

摘要! 采用FPGA技術! 在公司的flex6000系列芯片上實現了從設備模式pci總線的簡化協議!并給出了WIndowsx 系統下的虛擬設備驅動程序

2010-03-12 14:30:27 37

37 PCIe x8 主機接口、1 個 RJ45 千兆以太網口、2 個 QSFP+ 40G 光纖接口。板卡采用復旦微高性能 9 系列 FPGA 作為 實時處理器,實現

2025-09-24 11:39:45

摘要:為了實現高速HDLC通訊協議,設計了DSP+FPGA結構的485通訊接口,接口包括DSP、FPGA、485轉換等硬件電路,以及DSP與FPGA之間的數據交換程序和FPGA內部狀態機;其中DSP用于實現數據控制,FPGA用于實現HDLC通訊協議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 將PCIE與PCI、K1.X等總線技術進行比較,分析它的技術特性和優勢,剖析數據包在各層中的流動過程。/并且詳細闡述基于FPGA的兩種盯行性實現方案,即采用第三方PHY接口器件和低成本

2011-08-31 17:42:49 156

156 Altera公司(Nasdaq: ALTR)宣布,成功實現28-nm Stratix? V GX FPGA與PLX?技術公司(Nasdaq: PLXT) ExpressLane? PCI Express? (PCIe?) Gen3的互操作

2011-12-14 09:28:09 996

996 白皮書 :采用低成本FPGA實現高效的低功耗PCIe接口 了解一個基于DDR3存儲器控制器的真實PCI Express (PCIe) Gen1x4參考設計演示高效的Cyclone V FPGA怎樣降低系統總成本,同時實現性能和功耗

2013-02-26 10:04:25 73

73 根據PCIe的協議,當設備啟動后,PCIe設備必須滿足啟動時間的要求,即上電后100ms內,完成PCIe設備的初始化。如果不能滿足PCIe設備啟動時間的要求,則lspci可能無法檢測到基于FPGA

2017-02-07 20:55:41 4308

4308

PCI Express(PCIe)是一種高性能互連協議,可應用于網絡適配、圖形加速、服務器、大數據傳輸、嵌入式系統等領域。PCIe協議在軟件層上可兼容于PCI和PCIX,但同時也有明顯的不同。在兩個

2017-10-13 10:41:03 30

30 目前,PCI Express總線的實現方式主要有兩種:基于專用接口芯片ASIC和基于IP核的可編程邏輯器件FPGA方案。前者通常采用ASIC+FPGA/DSP的組合方式,專用PCIE接口芯片(如

2018-07-25 11:01:00 1914

1914 基于UltraScale架構的FPGA實現數據傳輸機制是通過將高性能的并行專用IO接口和高速的串行收發器結合起來實現的,UltraScale架構的串行收發器傳送數據的速率能夠達到16.3Gbps

2018-06-11 08:51:00 6899

6899 根據PCIe的協議,當設備啟動后,PCIe設備必須滿足啟動時間的要求,即上電后100ms內,完成PCIe設備的初始化。如果不能滿足PCIe設備啟動時間的要求,則lspci可能無法檢測到基于FPGA

2018-06-19 10:24:00 9045

9045

大部分來自對 TCP/IP 協議數據的處理,因此 CPU 的運算性能逐漸地成為高性能網絡通信發展的瓶頸。在這一形勢下,為將 CPU 從繁重的 TCP/IP 協議處理負擔中解放出來,本論文提出了一種實現 TCP/IP 協議處理的硬件解決方案,即利用 FPGA 本身所具有的密度高、速度快、小

2019-08-16 08:00:00 32

32 對于速度和實時性能要求非常高的協議,在硬件中以專用協議MAC的形式實現實時功能。而協議的其他功能由運行在嵌入式處理器中的軟件堆棧來完成,這些處理器可以是在 Cyclone III FPGA中實現的Nios II軟核處理器。

2020-07-21 17:39:00 2245

2245

PCIe協議分析儀作為PCIe總線分析的基本工具,不僅僅用于主機,網絡,存儲系統等各種IT和通訊設備針對PCIe插卡的問題分析,同時也是PCIe/NVMe SSD分析的必備工具。 作為PCIe協議

2020-09-21 14:26:48 12438

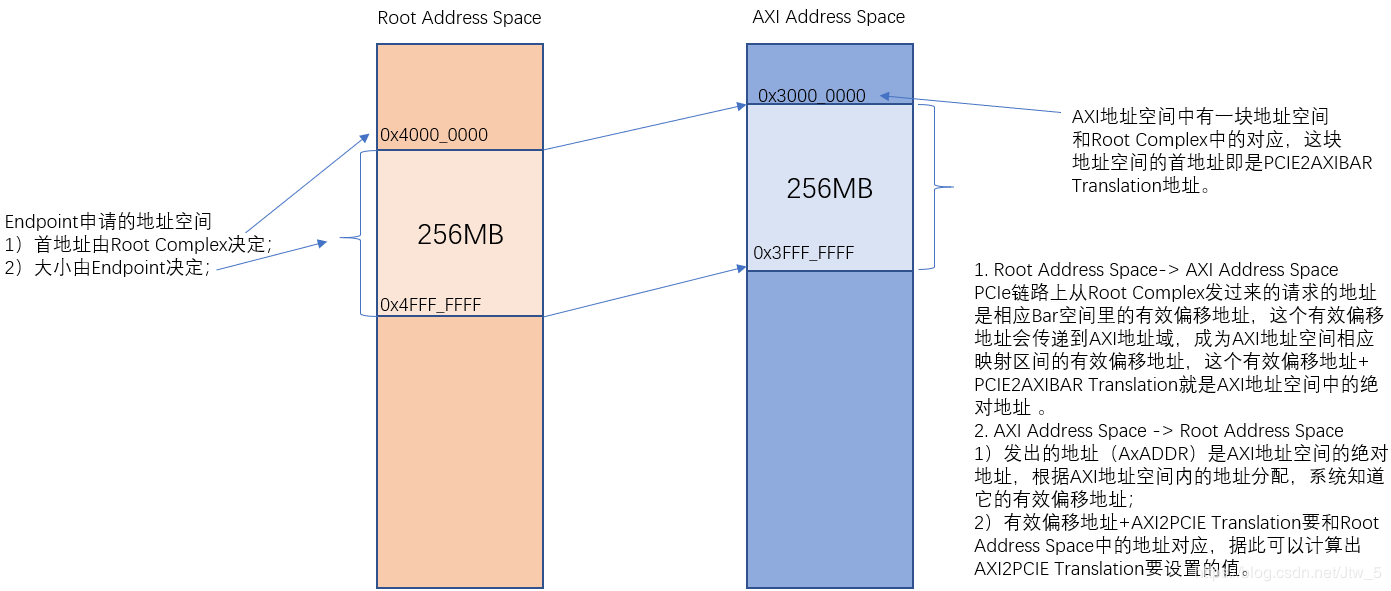

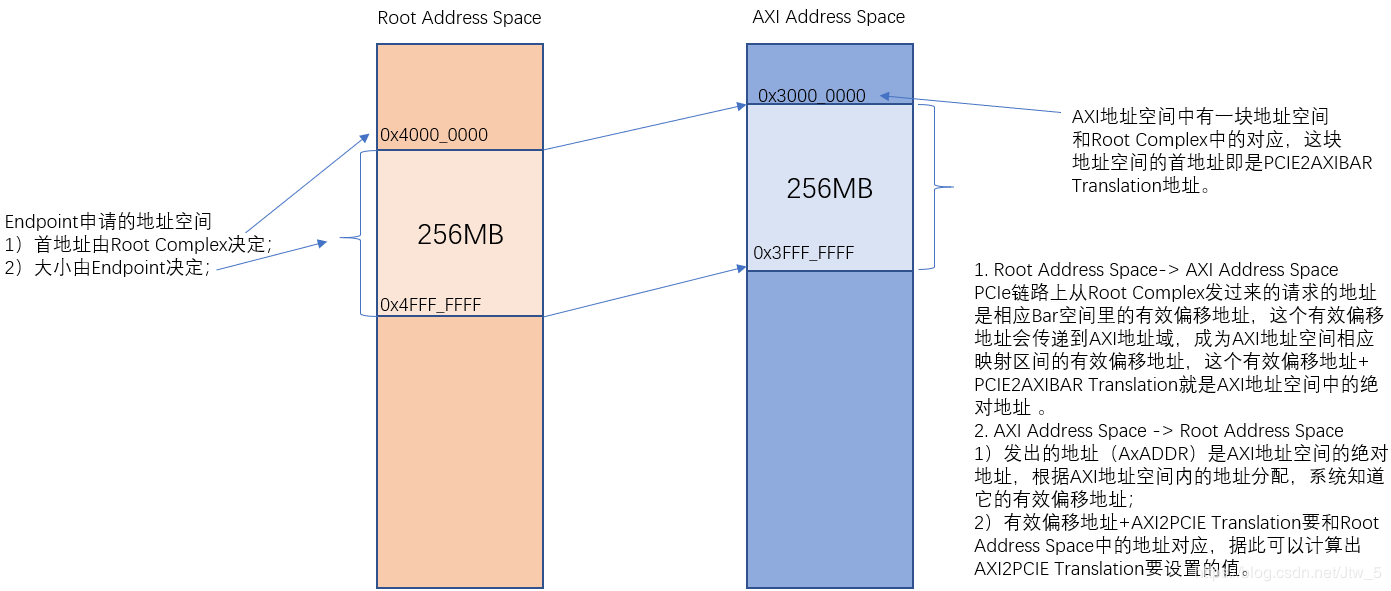

12438 背景與問題 CPU+FPGA架構,CPU做RC、FPGA做EP; FPGA邏輯(Vivado -BD - Address Editor)中如何設置PCIe to AXI Translation

2020-11-20 15:28:52 8159

8159

隨著三星980PRO PCIe4.0 SSD的正式推出,關于PCIe4.0技術和產品成為了存儲行業時下最為熱門的話題。

2020-09-29 17:37:39 4130

4130

為了實現軍航管制系統中雷達數據的可靠傳輸,根據HDLC協議的幀結構和循環冗余校驗(CRC)原理,提出了一種新型的基于并行機制的HDLC協議控制器,討論采用FPGA新技術實現HDLC協議幀的構成

2020-11-04 18:04:10 15

15 在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。

2020-12-29 17:27:22 14

14 Modbus協議是一個應用廣泛的工業現場總線協議,鑒于其簡單、開放、幀格式緊湊等優點,于2008年正式成為我國國家標準。介紹一種通過Cyclone系列FPGA實現Modbus RTU模式的方法,首先

2021-01-28 17:22:48 39

39 基于FPGA的TCP/IP協議的實現說明。

2021-04-28 11:19:47 54

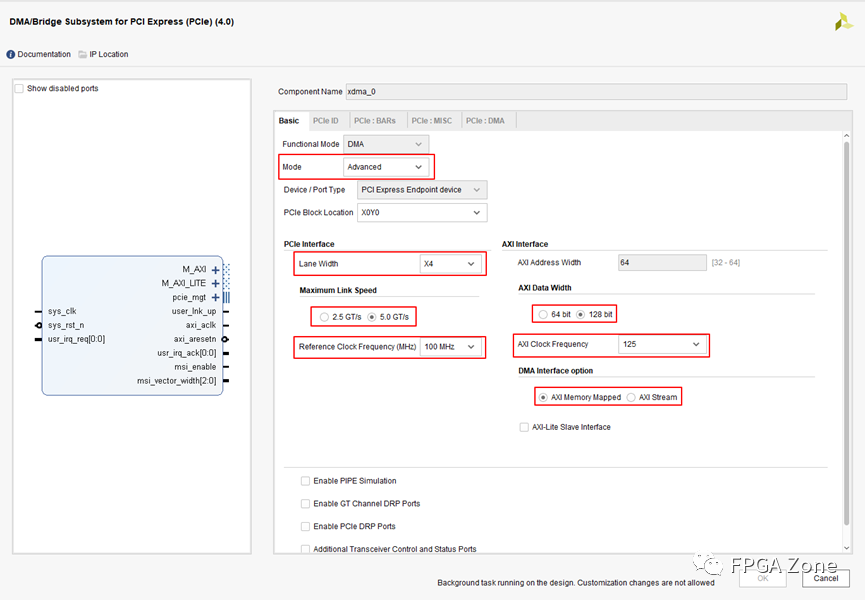

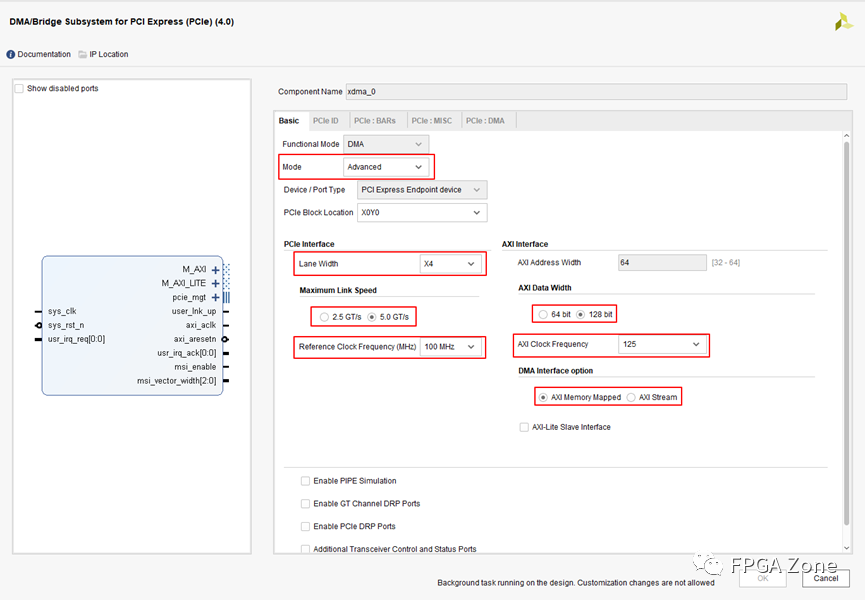

54 基于VIVADO的PCIE IP的使用 項目簡述 上一篇內容我們已經對PCIE協議進行了粗略的講解。那么不明白具體的PCIE協議,我們就不能在FPGA中使用PCIE來進行高速數據傳輸了嗎?答案是否

2021-08-09 16:22:10 15453

15453

基于FPGA的SPI協議及設計實現博主微信:flm13724054952,不懂的有疑惑的也可以加微信咨詢,歡迎大家前來投稿,謝謝!引言介紹在電子通信領域里采用的通信協議有IIC,SPI,UART

2021-11-05 19:05:59 24

24 PCIE協議5.0完整版

2022-09-13 14:32:47 0

0 FPGA實現SPI協議

2023-03-20 10:35:02 2

2 FPGA中關于SPI的使用

2023-04-12 10:13:16 1511

1511 AMD FPGA自帶PCIE硬核,實現了PCIE協議,把串行數據轉換為并行的用戶數據,以UltraScale系列FPGA為例,其支持Gen1.02.03.04.0,1~16 Lanes,如下圖所示。

2023-06-09 09:34:26 3032

3032

AMD FPGA自帶PCIE硬核,實現了PCIE協議,把串行數據轉換為并行的用戶數據

2023-07-14 15:53:40 2431

2431

本文介紹一個FPGA 開源項目:PCIE I/O控制卡。上一篇文章《FPGA優質開源項目– PCIE通信》開源了基于FPGA的PCIE通信Vivado工程,用于實現上位機通過PCIE接口訪問FPGA的DDR3以及RAM內存數據。PCIE I/O控制卡工程是在上一個工程的基礎上進行了部分模塊和參數的修改。

2023-09-01 16:18:36 5107

5107

本文介紹一個FPGA開源項目:PCIE通信。該工程圍繞Vivado軟件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的開源驅動程序,可在Windows系統或者Linux系統下使用,因此采用XDMA IP進行PCIE通信是比較簡單直接的。

2023-09-04 16:45:54 7011

7011

Hello,大家好,之前給大家分享了大約一百多個關于FPGA的開源項目,涉及PCIe、網絡、RISC-V、視頻編碼等等,這次給大家帶來的是不枯燥的娛樂項目,主要偏向老的游戲內核使用FPGA進行硬解,涉及的內核數不勝數,主要目標是高的可實現性及復現性。

2024-01-10 10:54:24 2672

2672

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,實現PCIe PHY Layer,Data Link Layer以及

2024-02-21 15:15:03 2109

2109

pcie協議

2024-05-16 09:09:35 100

100 FPGA(現場可編程門陣列)是一種高度靈活的集成電路,通過編程可以實現多種數字功能。在FPGA中實現單總線協議可以有效地簡化模塊之間的通信。單總線協議指的是所有設備或模塊共用一條通信線路(總線

2024-05-31 08:21:06 1757

1757

、網卡和聲卡等,以實現高效的數據傳輸。以下是對PCIe數據傳輸協議的介紹: 一、PCIe協議的基本概念 PCIe協議定義了一系列規范和要求,以實現在主機系統和外圍設備之間高效、可靠地進行數據通信。它采用了高速串行點對點雙通道高帶寬傳輸方式,所連接的設備分配獨享通道帶寬,不共享總線,

2024-11-26 16:12:57 5875

5875

電子發燒友App

電子發燒友App

評論