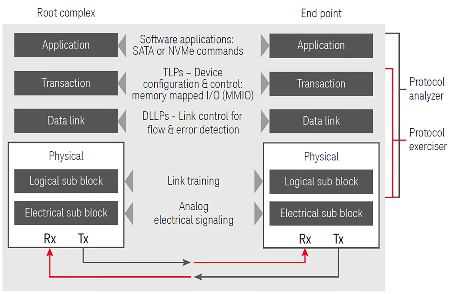

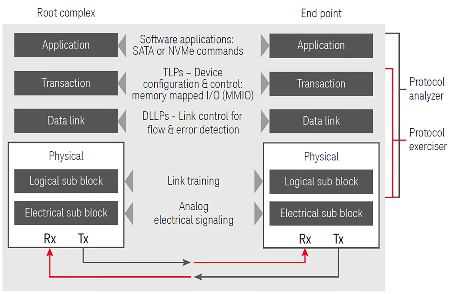

PCIe鏈路協議使用“端到端的數據傳送方式”,發送端和接收端中都含有TX(發送邏輯)和RX(接收邏輯)。

2019-06-19 17:44:44 7254

7254

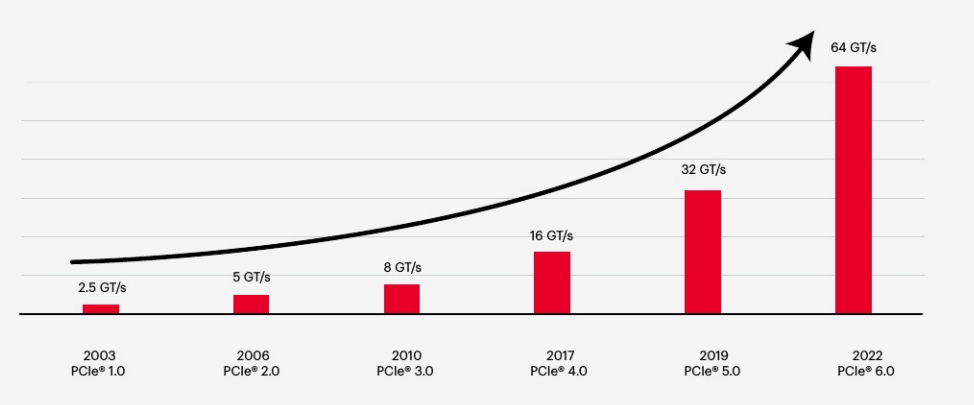

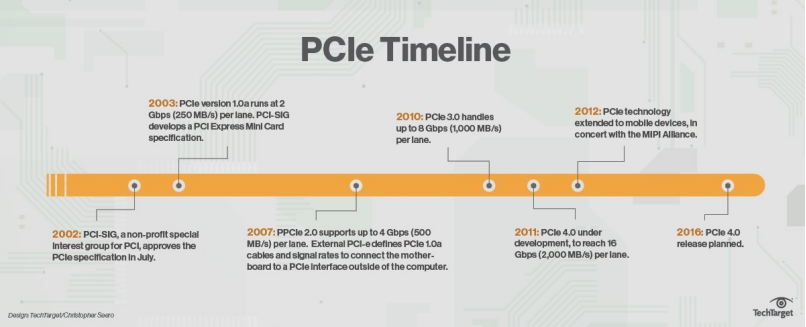

2010年,PCIe 3.0 將數據速率提高到了 8.0 GT/s ,并采用了新的 128b/130b 編碼機制,使每個引腳的帶寬比 PCIe 2.0 翻了一番。新的編碼機制通過采用三個隨機位翻轉檢測的故障模型確保了高可靠性

2023-01-04 11:17:04 13155

13155 最近幾期,我們將通過專欄的方式向大家介紹一個更加常用的高速接口——PCIe接口。"Peripheral Component Interconnect Express"(PCIe或PCI-E)是一種串行擴展總線標準,計算機利用該接口可以擴展連接一個或多個外圍設備。

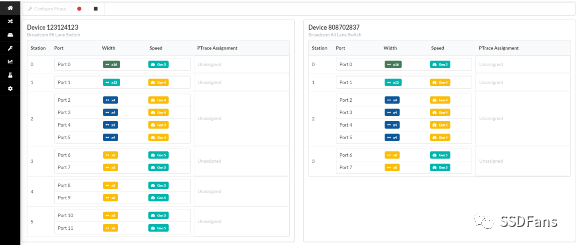

2023-09-26 11:37:37 11907

11907

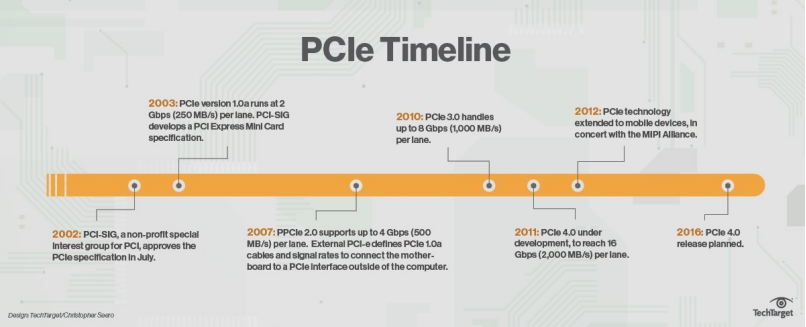

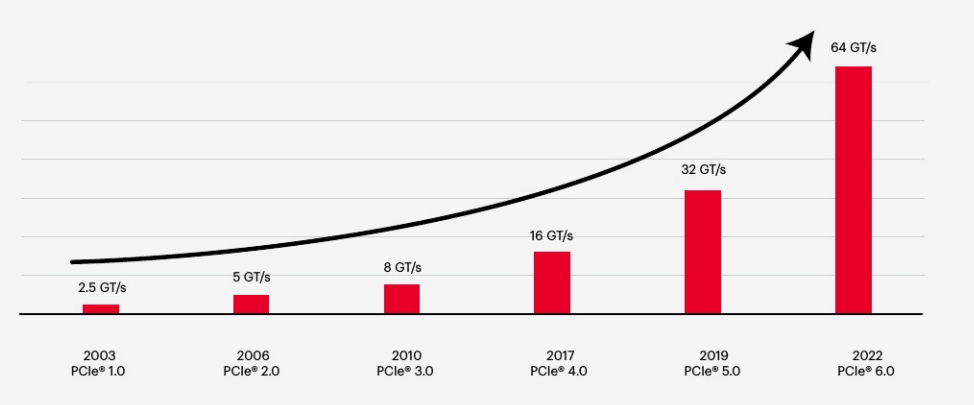

自2003年推出以來,PCIe發展至今已經從最初的1.0升級到了6.0,本文則為大家簡單介紹一下PCIe標準的演進歷史以及各代PCIe標準之間的主要差異。

2023-12-14 16:38:08 10115

10115

變化,即可能會導致該類儀器不能夠讓其進入到環回模式。具有協議使能誤碼儀將不會存在這樣的問題。 二、PCIE 3.0 進入環回(Loopback )狀態步驟 上圖所示為PCIE 3.0 的主要工作

2018-09-26 17:33:30

小弟學習K1_STK(從官網下的最新的例程keystone軟件開發包)里面的PCIE(例程),這個是例程里面RC端和EP端用的是MSI中斷。PCIE

2018-06-21 03:49:49

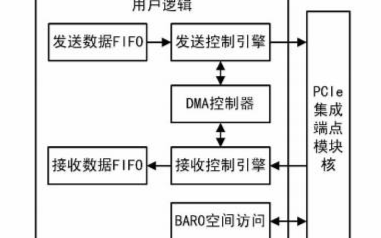

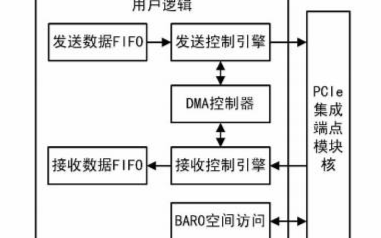

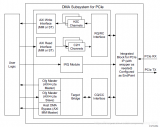

結構圖這是PCIE IP核,主要用來發送數據,發送引擎主要負責將待發送數據按照PCIE協議組織成不同類型的TLP數據包,并發送給PCIE IP核;發送DMA控制模塊主要負責把DDR3中讀取的數據轉換成

2019-12-26 10:46:09

開發環境:windows開發平臺:QT5.11.31.PCIE上位機測試過程FPGA將數據傳到芯片中,通過pcie再將芯片算完的數傳給上位機。目標:1.實現上位機的速度測試,經測試pcie的傳輸速度

2019-12-26 10:27:19

開發環境:windows開發平臺:QT5.11.31、PCIE上位機測試過程FPGA將數據傳到芯片中,通過pcie再將芯片算完的數傳給上位機。目標:1.實現上位機的速度測試,經測試pcie的傳輸速度

2022-01-13 16:44:54

PCIE-52P90H

2023-03-29 22:43:17

1 PCIE基本概念1.1 PCIE拓撲架構圖1.2 PCIE Switch內部結構圖1.3 PCIE協議結構圖2 PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓撲示例

2022-02-16 06:08:26

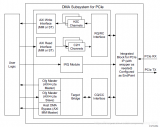

本文檔旨在提供關于將PCIe接口集成到基于AMBA的片上系統(SoC)的指導。

假設PCIe接口通過基于AXI或ACE協議的互連連接到SoC的其余部分。

讀者應熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

PCIe協議分析儀在數據中心中扮演著至關重要的角色,它通過深度解析PCIe總線的物理層、鏈路層、事務層及應用層協議,幫助運維人員、硬件工程師和系統架構師優化性能、診斷故障、驗證設計合規性,并提

2025-07-29 15:02:27

PCIe協議分析儀能測試多種依賴PCIe總線進行高速數據傳輸的設備,其測試范圍覆蓋計算、存儲、網絡及異構計算等多個領域,具體設備類型及測試場景如下:一、核心計算設備

GPU(圖形處理器)

測試

2025-07-25 14:09:01

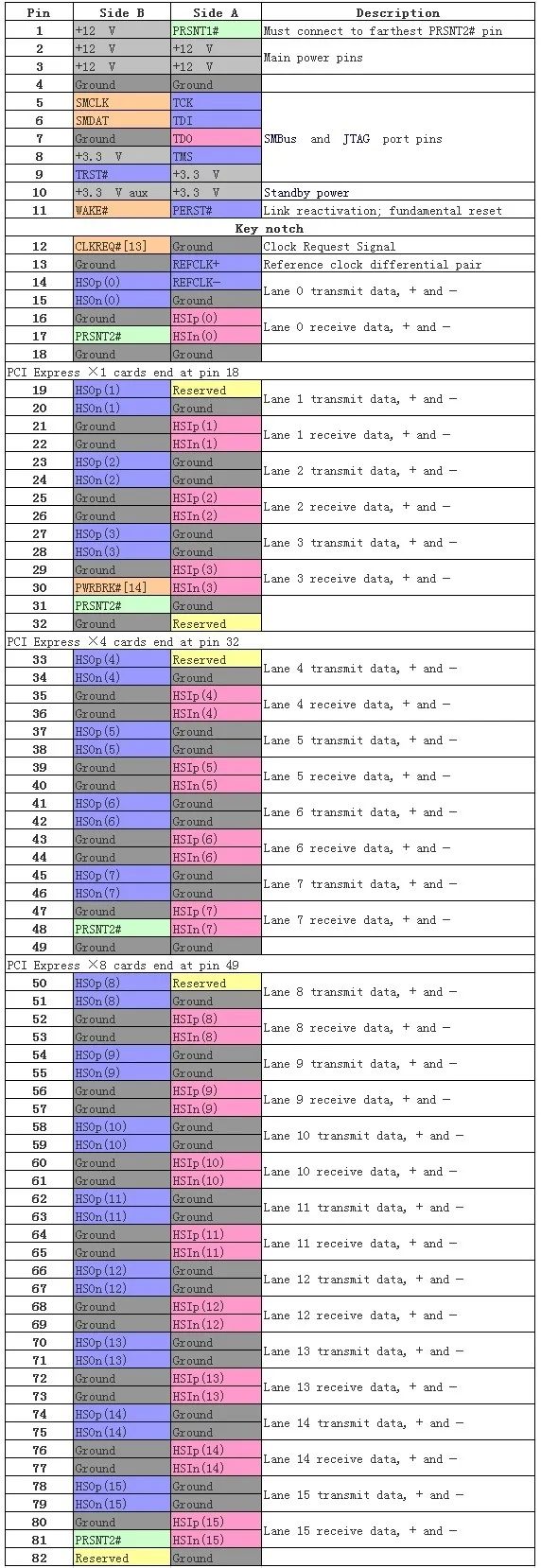

PCIe提供了一種可裁減高速串行I/O點到點的總線連接。PCIe的LAN是一個全雙工的通道,由一對接收差分對和一對發送差分對構成。PCIe的帶寬可以通過增減LANE數來調整。PCIe規范定義了x1

2019-06-03 07:09:56

了,卡和盤的界限消失了。從卡到盤的演進通過NVMe協議,SSD盤透過PCIe直連CPU,不似以往還要轉換為SAS/SATA,因而開啟了一個新時代。從技術上,在磁盤(HDD)的時代,由于磁盤屬于低速設備

2019-06-24 05:00:55

pcie虛擬化技術中,一端pcie的虛擬通道又睡指定,是通過軟件配置嗎

2019-11-11 10:34:47

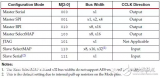

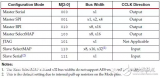

5 物理層5.1 介紹CCIX 1.1設備必須支持兩種物理層中的一種:PCIe 5.0 PHY,或者是CCIX EDR PHY。5.2 EDR25-SR電氣規范EDR25-SR電氣規范適用于

2022-08-16 15:45:06

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

PCIE BOARD 6 PORT DB-9

2023-03-22 20:41:28

MODULE CONV PCIE-SMA

2023-03-22 20:00:22

查過mini pcie的信號引腳定義,有52個信號(大多引腳無用),X1 LANE 的情況,查看飛思卡爾或INTEL處理器的設計資料,關于這個應用除了主要 的差分收、發和差分時鐘信號之外還需要額外

2017-11-29 11:50:51

FPGA(資源夠用)都可以以soft IP形式實現FPGA嗎?4.個人覺得使用Megwizard和Qsys中的IP就可以實現PCIE功能了,那么什么樣的設計還需要加專用的協議芯片呢?謝謝!

2015-07-27 11:05:46

DEV SYSTEM P4080 PCIE

2023-03-22 19:55:54

PC介紹之PCIE、總線、內存、電源PCIE降速PCI-E的總線性能目前我們所使用的顯卡是x16 走 PCIE 3.0,有些顯卡雖然插在x16的插槽上,但是速度只有x8的速度,總的來說好的顯卡目前

2021-12-28 08:10:31

DEVELOPMENTSYSTEMT4240PCIE

2023-03-22 19:56:26

你好

作為我們在 ls1028 上努力的一部分

我們通過 pcie 將自定義 fpga 連接到 M.2 連接器(通道 C/2 - j16)

相關uboot日志:

U-Boot

2023-05-09 12:00:30

,獲取其它設備的響應。

PCIe層次結構

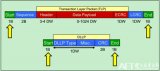

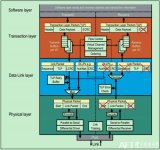

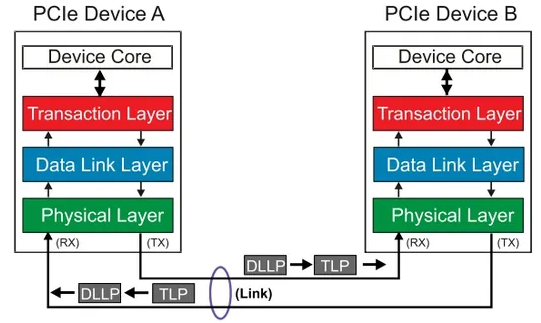

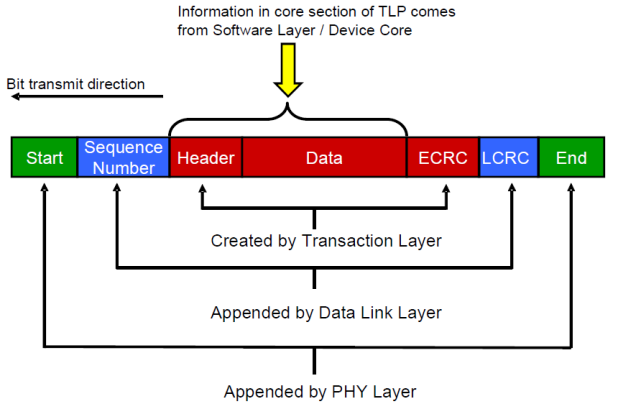

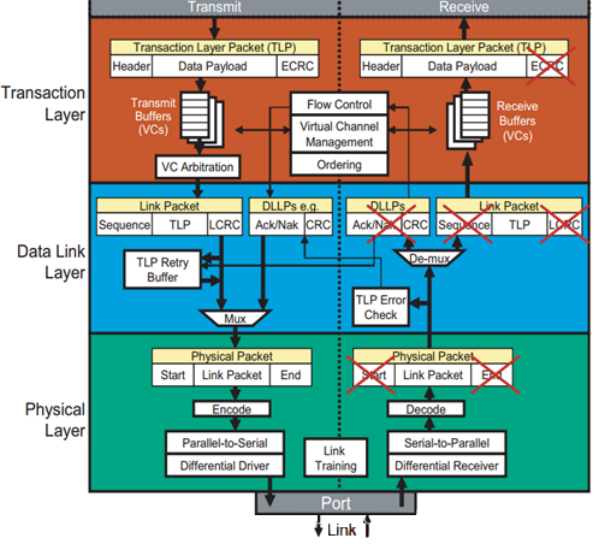

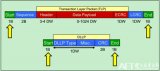

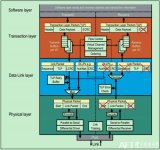

PCIe 總線是一種分層協議總線,采用數據包進行數據傳輸。數據包在收發過程中需要經過事務層、數據鏈路層和物理層三個層次的處理和轉發。PCIe總線的分層結構如圖2

2025-05-17 14:54:25

數據,Posted類型的事務請求不需要使用 完成報文。 PCIe總線協議定義了基于地址的路由、基于ID的路由和隱式路由三種TLP路由 方式。其中,存儲器讀寫和I/O讀寫TLP采用基于地址的路由,該類

2025-05-18 00:48:43

串行總線協議PCIe、ASI和sRIO之間有什么不同?

2021-05-25 07:05:09

?開發板測試:1、 安裝windrive 2、LED狀態顯示 3、測試讀寫 PCIE開發板介紹:1、原理圖介紹 PCIE TLP協議介紹:1、分析存儲器寫報文結構 2、分析存儲器讀報文結構 PCIE

2022-02-14 09:50:22

,那就很容易把pcie協議理解徹透徹,當然這里狹義指的是上層交互的TLP協議,數據鏈路層和物理層更復雜的事情是硬核做的,用起來PCIE并不需要深入了解。

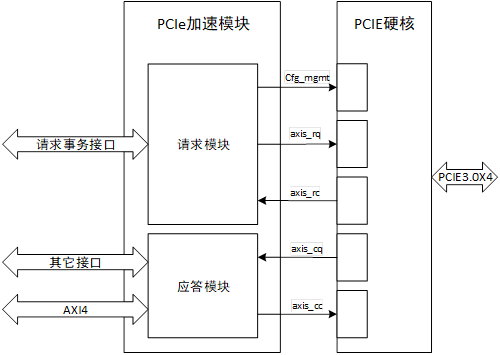

如何使用紫光PCIE,首先FPGA端需要一個

2023-11-17 14:35:30

特點: 1)主芯片采用Xilinx Virtex-5LXT FPGA。 前面板提供4路光纖接口,速率可達2.5Gbps/3.125Gbps,用戶可以選擇自定義協議或Aurora協議或工業標準協議

2012-06-18 11:40:51

) 的比特率。第 4 代的規范預計將在 2014 或 2015 年發布。表 1:各代 PCIe 的數據吞吐量隨著數據速率的提升,參考時鐘需求也在不斷提高。本文將重點介紹參考時鐘需求。PCIe 參考時鐘

2022-11-22 08:04:25

你能提供詳細信息為什么 i.MX8 QuadXPlus MEK 上的 PCIE_CTRL0_WAKE_B 總是高電平嗎? 我檢查過有一個上拉電阻,這個信號可以低嗎?您能否也讓我知道如何在來自 wifi 模塊的 PCIE 引腳上啟用喚醒?

2023-04-10 07:52:58

如何對PCIe3.0接收機物理層進行測試?

2021-05-11 06:04:51

我是一名PCIe新手,想了解以下問題:

1、如何測試PCIe?

2、如何讀寫PCIe(兩塊開發板通過PCIe線互連,分別配置為RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

PCI Express (PCIe)是嵌入式和其它系統類型的背板間通信的一個非常理想的協議。然而,在嵌入式環境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結構的PCIe時鐘分配方案就變得

2019-09-26 07:56:41

PCI Express (PCIe)是嵌入式和其它系統類型的背板間通信的一個非常理想的協議。然而,在嵌入式環境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結構的PCIe時鐘分配方案就變得

2019-08-30 06:54:47

嗨,我有一個ML605板和一塊使用RapidIO協議的DSP板。該板有兩個FMC連接器(HPC和LPC)和一個PCIe接口,我需要4個萬兆收發器(MGT),PCIe和FMC HPC都有8個(LPC

2019-08-29 10:33:02

傳輸速率是根據PCIE的協議制定的嗎?2.如果我設置的速率超過5.0Gbps可以嗎?是否會出現數據的傳輸錯誤等現象?3.不太理解PCIE中關于x1和x2的含義,文檔說PCIE是one single interface link,那么對于單個端口而言,x2的含義僅僅是代表速率是x1速率的一倍嗎?

2018-06-19 04:36:26

PCI Express是一種高性能互連協議,被廣泛應用于網絡適配、圖形加速器、網絡存儲、大數據傳輸以及嵌入式系統等領域。文中介紹了PCIe的體系結構,以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP為高帶寬應用提供高性能、多通道功能和低功耗架構。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本應

2023-04-03 19:50:56

基于PCIe2_0協議的PCS層彈性緩沖器設計_武桂林

2017-01-07 20:49:27 5

5 PCI Express(PCIe)是一種高性能互連協議,可應用于網絡適配、圖形加速、服務器、大數據傳輸、嵌入式系統等領域。PCIe協議在軟件層上可兼容于PCI和PCIX,但同時也有明顯的不同。在兩個

2017-10-13 10:41:03 30

30 與PCI總線不同,PCIe總線使用端到端的連接方式,在一條PCIe鏈路的兩端只能各連接一個設備,這兩個設備互為是數據發送端和數據接收端。PCIe總線除了總線鏈路外,還具有多個層次,發送端發送數據時將通過這些層次,而接收端接收數據時也使用這些層次。PCIe總線使用的層次結構與網絡協議棧較為類似。

2017-12-12 10:37:12 172661

172661 本文檔內容介紹了基于SIM7100-PCIE4G模塊PCIE封裝硬件資料,供參考

2018-03-15 11:26:13 137

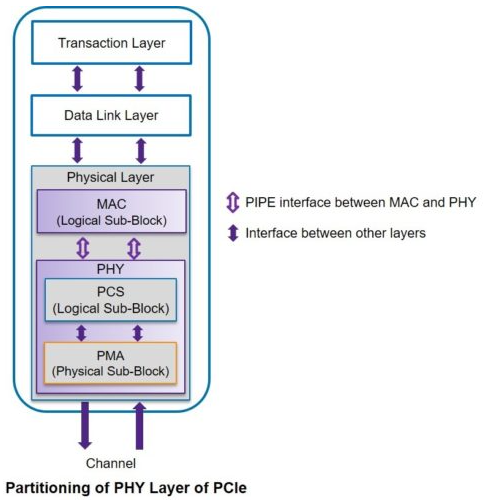

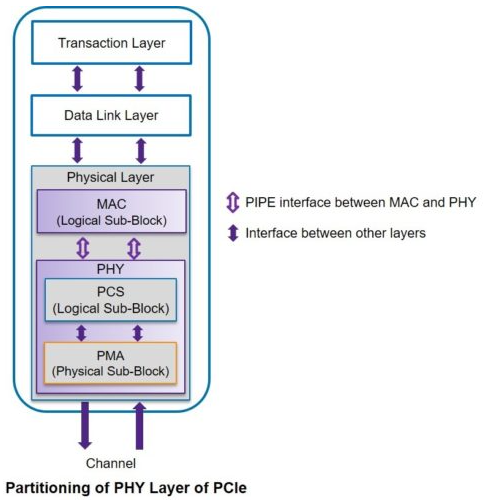

137 需要注意的是,PCIe物理層處理可以轉發LTP和DLLP之外,還可以直接發送命令集(Ordered Sets)。之所以稱其為命令集,是因為它并不是真正意義上的包(Packet),因為物理層不會為其添加起始字符(Start & End Characters)。

2018-05-02 10:06:22 11382

11382

。也就是說,廠商可以根據自己的需要和實際情況,來設計PCIe的物理層。下面將以Mindshare書中的例子來簡要的介紹PCIe的物理層邏輯部分,可能會與其他的廠商的設備的物理層實現方式有所差異,但是設計的目標和最終的功能是基本一致的。

2018-05-31 09:16:39 14447

14447

根據PCIe的協議,當設備啟動后,PCIe設備必須滿足啟動時間的要求,即上電后100ms內,完成PCIe設備的初始化。如果不能滿足PCIe設備啟動時間的要求,則lspci可能無法檢測到基于FPGA

2018-06-19 10:24:00 9045

9045

PCIe總線錯誤檢測囊括了鏈路(Link)上的錯誤以及包傳遞過程中的錯誤,如下圖所示。用戶設計的應用程序層中的錯誤不屬于鏈路傳輸中的錯誤,不應當通過PCIe的錯誤檢測與處理機制處理,一般可借助設備特殊中斷(Device Specific Interrupt)等合適的方式進行報告與處理。

2018-08-18 11:05:05 15934

15934 該信號為全局復位信號,由處理器系統提供(RC),處理器系統需要為PCIe插槽和PCIe設備提供該復位信號。PCIe設備使用該信號復位內部邏輯。當該信號有效時,PCIe設備將進行復位操作。

2018-12-22 14:45:41 24628

24628 PCIe協議分析儀作為PCIe總線分析的基本工具,不僅僅用于主機,網絡,存儲系統等各種IT和通訊設備針對PCIe插卡的問題分析,同時也是PCIe/NVMe SSD分析的必備工具。 作為PCIe協議

2020-09-21 14:26:48 12438

12438 ,M-PCIe ECN主要的改動在物理層,通過引入M-PHY,旨在獲得更低的功耗以適應嵌入式設備的低功耗要求。 M-PCIe的主要特性如下: M-PCIe的上層協議層、事務層(TL)、數據鏈

2020-11-24 14:51:48 9188

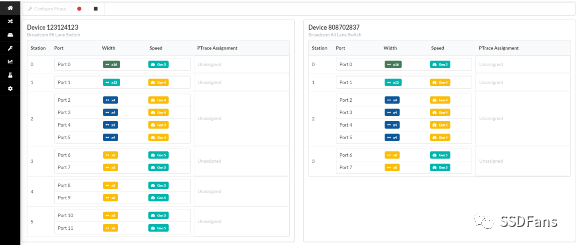

9188 SerialTek是PCIe,NVMe和SAS/SATA協議測試解決方案的全球領先提供商,今天推出的PCIe測試和分析市場的最新技術和產品BusXpertiTAP,支持Broadcom的PCIe嵌入式分析儀技術,這是Broadcom新的PEX89000 Gen5 PCIe交換芯片的一項突破性功能。

2021-04-13 15:34:21 8426

8426

(PCIE5.0 X16),增長了480倍。 PCIe 5.0 第5代PCIe技術 PCIe5.0速度是 PCIe 4.0 的兩倍,并具有向下兼容性。PCIe 5.0 協議分析儀能夠支持 32GT/秒

2021-06-19 11:04:51 44751

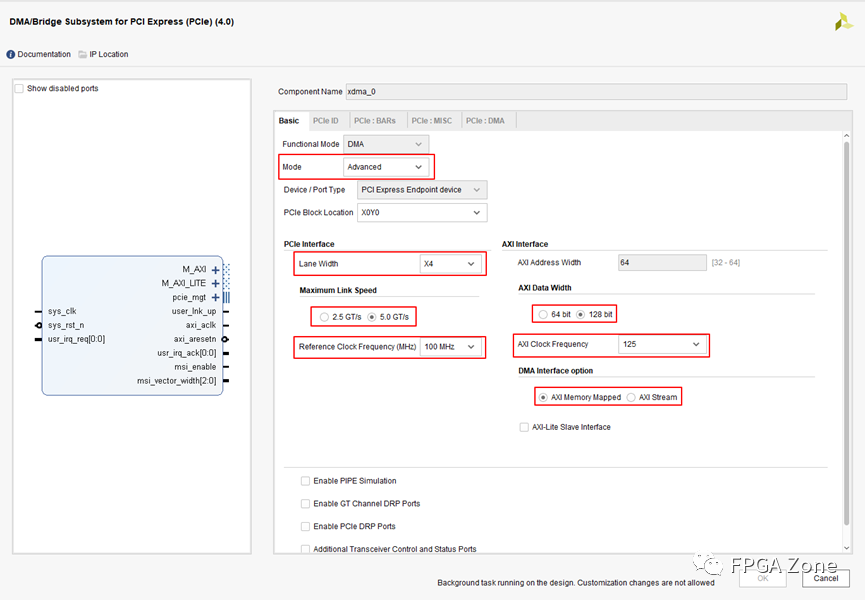

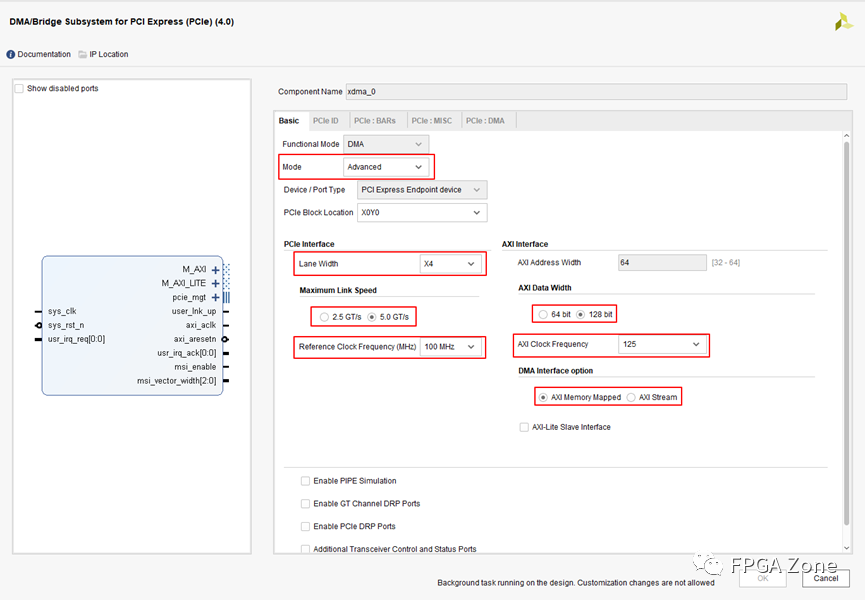

44751 基于VIVADO的PCIE IP的使用 項目簡述 上一篇內容我們已經對PCIE協議進行了粗略的講解。那么不明白具體的PCIE協議,我們就不能在FPGA中使用PCIE來進行高速數據傳輸了嗎?答案是否

2021-08-09 16:22:10 15454

15454

全面介紹PCIe總線的基礎知識

2021-12-14 11:49:33 0

0 1 PCIE基本概念1.1 PCIE拓撲架構圖1.2 PCIE Switch內部結構圖1.3 PCIE協議結構圖2 PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓撲示例

2021-12-17 18:29:51 29

29 提供PCIe5.0/6.0 從仿真到物理層到協議層的完整測試方案。

2022-04-18 11:35:35 2565

2565 在滿足所有測試以建立穩定的通信通道后,下一步是驗證PCIe 總線上的應用層(例如 NVMe)。對于 NVMe 協議測試,用戶將需要一個工具來觀察不同部分的交互方式。數據鏈路層、確認、流控制、多個隊列和多個命令需要協調。在一次 NVMe 讀取中可能需要分析數千個數據包。一個好的工具將

2022-06-19 15:44:08 3140

3140

PCIe 3.0協議支持8.0GT/s,即每一條Lane上支持每秒鐘傳輸8G個Bit。而PCIe 3.0的物理層協議中使用的是128b/130b編碼方案,即每傳輸128個Bit,需要發送130個Bit。

2022-08-29 16:09:17 4901

4901 PCIE協議5.0完整版

2022-09-13 14:32:47 0

0 電子發燒友網站提供《PCIe 9110I PCIe 9210I PCIe 9410I EMC證書.pdf》資料免費下載

2022-10-14 10:05:14 1

1 熱插拔的基本目的是要讓PCIe設備按照規定的順序、原則,從系統中移除或插入到系統中來,并能正常的工作,且不影響系統的正常運行。事實上,PCIe“熱插拔”的關鍵目的就是為前面面所提到的系統RAS服務的,是提升系統RAS能力的非常重要的手段!

2022-12-14 10:59:19 6408

6408 PCIe接口從2001年發展至今,在協議的完整性上已經建立足夠高的"護城河",重新定義一個接口協議在性能上超越PCIe,短期內一方面沒有企業會有這個動力,另一方面技術的維度,也沒有可預期的雛形創新。

2023-04-13 11:10:00 7121

7121 最近某開發嵌入式平臺的客戶到我們的協議測試Open Lab分析底層PCIe的問題。

2023-05-06 09:25:26 1855

1855

PCIe 是一種多層串行總線協議,可實現雙單工鏈路。由于其專用的點對點拓撲,它提供高速數據傳輸和低延遲。為了加快基于 PCIe 的子系統的驗證和設備開發時間,英特爾定義了 PIPE(PCI

2023-05-26 11:43:19 5983

5983

與cocotbext-pcie做記錄。 》ACK/NAK ????與TCP協議般,PCIe協議在數據鏈路層采用滑動窗口ACK/NAK協議來保證數據傳輸。對于傳輸層

2023-06-25 10:31:17 4440

4440

PCIe是一種高速串行計算機擴展總線標準,自2003年推出以來,已經成為服務器(Server)和PC上的重要接口。今天為大家簡單介紹一下PCIe的發展歷史以及它的工作原理。 一、PCIe的由來

2023-07-04 18:15:03 23558

23558 AMD FPGA自帶PCIE硬核,實現了PCIE協議,把串行數據轉換為并行的用戶數據

2023-07-14 15:53:40 2432

2432

自2003年推出以來,PCIe發展至今已經從最初的1.0升級到了6.0,在上一篇文章中為大家介紹了PCIe基礎知識:《什么是PCIe?》 ,本文則為大家簡單介紹一下 PCIe 標準的演進歷史以及各代

2023-07-26 08:05:01 2655

2655

本文介紹一個FPGA開源項目:PCIE通信。該工程圍繞Vivado軟件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的開源驅動程序,可在Windows系統或者Linux系統下使用,因此采用XDMA IP進行PCIE通信是比較簡單直接的。

2023-09-04 16:45:54 7014

7014

隨著英特爾Alder Lake CPU的發布,以及AMD 7000 Ryzen CPU的即將發布,PCIe 5.0 硬件終于成為現實。但什么是 PCIe 5.0?

2023-11-18 16:48:14 6074

6074

PCIExpress(PCIe)是一種高性能通用I/O互連協議,廣泛用于各種計算產品和通信產品。由于時延低、帶寬明顯要更高,因此業界正在融合到PCIe,作為高速串行總線標準。PCIe在

2024-01-18 08:27:39 7869

7869

什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 5102

5102 pcie協議

2024-05-16 09:09:35 100

100 PCIe 4.0和PCIe 3.0接口在多個方面實現了兼容性,PCIe 4.0和PCIe 3.0接口兼容性問題是一個廣泛討論的話題。 PCIe 4.0和PCIe 3.0的定義 PCIe

2024-07-10 10:12:09 15333

15333 ,用于串行數據傳輸總線。PCIe 的物理層 (PHY) 還支持 SATA Express (SATAe) 和非易失性存儲器規范 (NVMe)。 表 1 顯示了 PCIe 數據速率的演變,PCIe 5.0

2024-08-16 09:33:05 2909

2909

PCIe的數據鏈路層在事務層和物理層之間,用來負責鏈路管理,其主要功能是保證來自事務層的TLP在PCIe鏈路中的正確傳輸,為此數據鏈路層定義了一系列的DLLP報文,數據鏈路層使用了容錯和重傳機制保證

2024-11-05 17:06:04 1901

1901

PCI Express(PCIe)是一種高速串行計算機擴展總線標準,主要用于計算機內部硬件設備之間的連接。以下是PCIe接口的工作原理的簡要概述: 串行通信 :與傳統的并行PCI總線不同,PCIe

2024-11-06 09:19:16 5698

5698 隨著科技的快速發展,計算機硬件也在不斷地更新換代。PCI Express(PCIe)作為一種高速串行計算機擴展總線標準,廣泛應用于計算機硬件連接,如顯卡、固態硬盤等。 1. 帶寬對比 PCIe

2024-11-06 09:22:07 18938

18938 隨著數據傳輸需求的日益增長,計算機硬件接口也在不斷進化。PCIe(Peripheral Component Interconnect Express)作為連接計算機內部組件的高速串行總線標準,已經

2024-11-13 10:35:28 20174

20174 前言本文主要講述PCIe熱插拔機制,通過圖形方式方便讀者快速掌握。 一、概述 如果在PCIe設備不支持熱插拔的條件下,在不斷電的情況下插拔一塊PCIe SSD時,很可能會對主板或PCIe插槽造成損毀

2024-11-20 09:07:50 4704

4704

能有著不可忽視的影響。 PCIe延遲的定義 PCIe延遲是指數據在PCIe總線上從一個設備傳輸到另一個設備所需的時間。這個時間包括了信號的傳播延遲、設備處理延遲和隊列延遲等多個部分。傳播延遲是指信號在PCIe總線上的物理傳播時間,處理延遲是指

2024-11-26 15:14:20 3381

3381 、網卡和聲卡等,以實現高效的數據傳輸。以下是對PCIe數據傳輸協議的介紹: 一、PCIe協議的基本概念 PCIe協議定義了一系列規范和要求,以實現在主機系統和外圍設備之間高效、可靠地進行數據通信。它采用了高速串行點對點雙通道高帶寬傳輸方式,所連接的設備分配獨享通道帶寬,不共享總線,

2024-11-26 16:12:57 5876

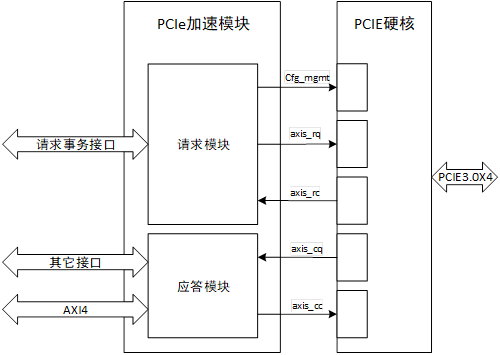

5876 PCIe加速模塊負責實現PCIe傳輸層任務的處理,同時與NVMe層進行任務交互。PCIe加速模塊按照請求發起方分為請求模塊和應答模塊。

2025-08-09 14:38:41 4629

4629

電子發燒友App

電子發燒友App

評論