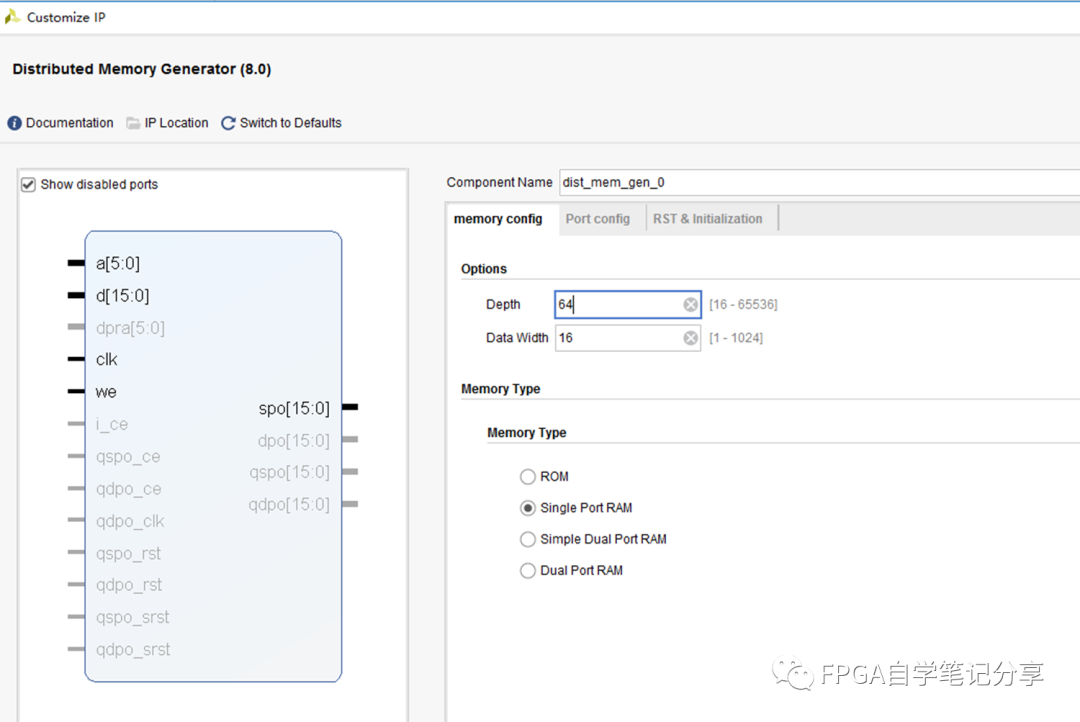

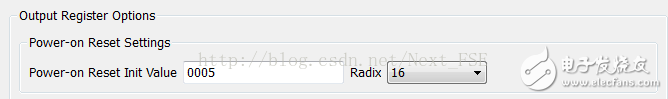

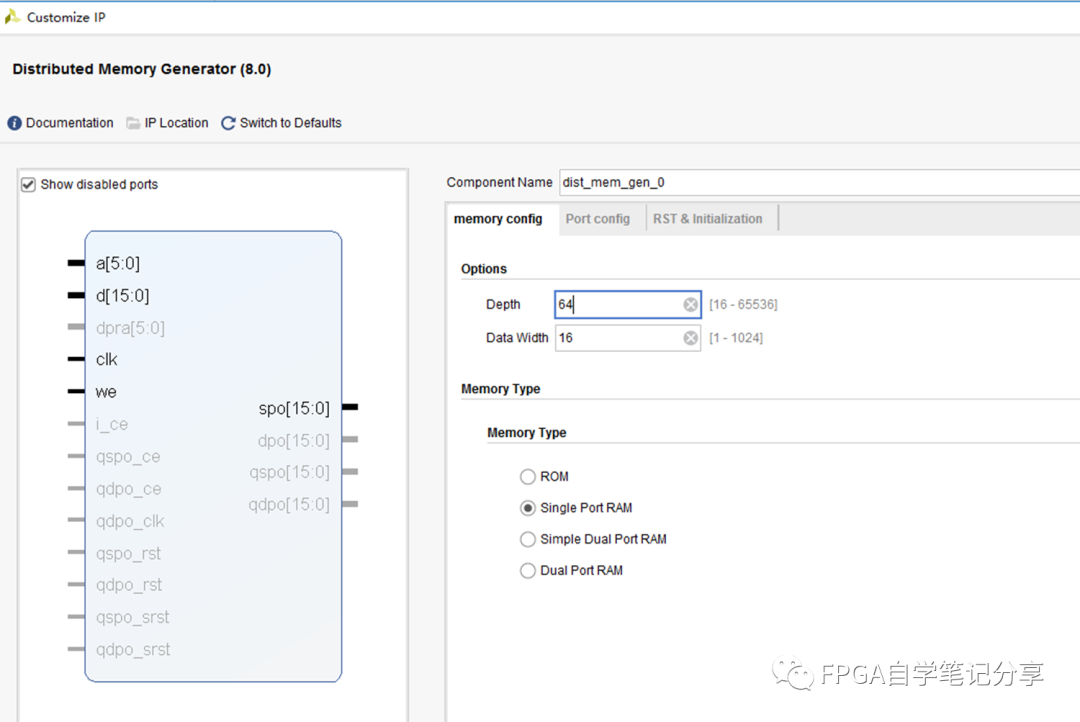

/雙端口 RAM 以及基于 SRL16 的 RAM。該IP的靈活的特性配置方式,使用戶能針對存儲(chǔ)器類型、數(shù)據(jù)寬度、存儲(chǔ)器大小、輸入/輸出選項(xiàng)和復(fù)位選項(xiàng)進(jìn)行定制。

2023-11-17 17:00:30 3410

3410

初始化時(shí)存入數(shù)據(jù)。那在IP核rom中存放大量數(shù)據(jù)對FPGA有什么影響,比如我想存65536個(gè)16位的數(shù),然后在64M或者128M的時(shí)鐘下讀出來。會(huì)不會(huì)導(dǎo)致FPGA速度過慢?

2013-01-10 17:19:11

的基礎(chǔ)上,給出了一種仿真調(diào)試方 案;利用該方案指出了其中若干邏輯錯(cuò)誤并對其進(jìn)行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結(jié)構(gòu)分析OpenCores網(wǎng)站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA嵌入8051單片機(jī) IP核編程,編寫的c語言矩陣鍵盤程序可以在stc89c54單片機(jī)上正常工作,但是下載到FPGA中8051單片機(jī)ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

本帖最后由 jf_25420317 于 2023-11-17 11:10 編輯

FPGA開發(fā)過程中,利用各種IP核,可以快速完成功能開發(fā),不需要花費(fèi)大量時(shí)間重復(fù)造輪子。

當(dāng)我們面對使用新IP核

2023-11-17 11:09:22

和性能測試。確保IP軟核能夠正常工作,并滿足項(xiàng)目的性能要求。

在驗(yàn)證過程中,可以使用仿真工具進(jìn)行模擬測試,或者使用實(shí)際的FPGA硬件進(jìn)行驗(yàn)證。

優(yōu)化和調(diào)試 :

如果在驗(yàn)證過程中發(fā)現(xiàn)問題或性能瓶頸

2024-05-27 16:13:24

有誰知道現(xiàn)在國內(nèi)外有哪些公司賣FPGA的圖像處理相關(guān)的IP核?

2015-04-28 21:34:24

是具有知識產(chǎn)權(quán)核的集成電路芯核總稱,是經(jīng)過反復(fù)驗(yàn)證過的、具有特定功能的宏模塊,與芯片制造工藝無關(guān),可以移植到不同的半導(dǎo)體工藝中。到了SOC 階段,IP 核設(shè)計(jì)已成為ASIC 電路設(shè)計(jì)公司和FPGA

2018-09-03 11:03:27

USB OTG的工作原理是什么?IP設(shè)計(jì)原理是什么?如何進(jìn)行IP模塊設(shè)計(jì)?USB OTG IP核有什么特性?如何對USB OTG IP核進(jìn)行FPGA驗(yàn)證?

2021-04-27 06:44:33

劃分為幾個(gè)主要模塊,分別介紹各個(gè)模塊的功能,用VHDL語言對其進(jìn)行描述,用FPGA實(shí)現(xiàn)并通過了仿真驗(yàn)證。該IP核具有良好的移植性,可驅(qū)動(dòng)不同規(guī)模的LCD電路。 關(guān)鍵詞:LCD;驅(qū)動(dòng)電路;IP 引言

2012-08-12 12:28:42

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一個(gè)輸入。我參考網(wǎng)上VHDL CORDIC IP核,說是將XY合并了,高位X低位Y。不知道在LabVIEW中如何將兩個(gè)值X、Y合并成一個(gè)(X、Y均為定點(diǎn)數(shù))。具體情況如下圖:

2019-09-10 20:07:07

移位寄存器 (SRL16)”第 8 章 “使用專用多路復(fù)用器”第 9 章 “使用進(jìn)位和算術(shù)邏輯”第 10 章 “使用 I/O 資源”第 11 章 “使用嵌入式乘法器”第 12 章 “使用互連”“部分 II

2013-02-27 20:20:10

USB_OTG_IP核中AMBA接口的設(shè)計(jì)與FPGA實(shí)現(xiàn)

2012-08-06 11:40:55

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

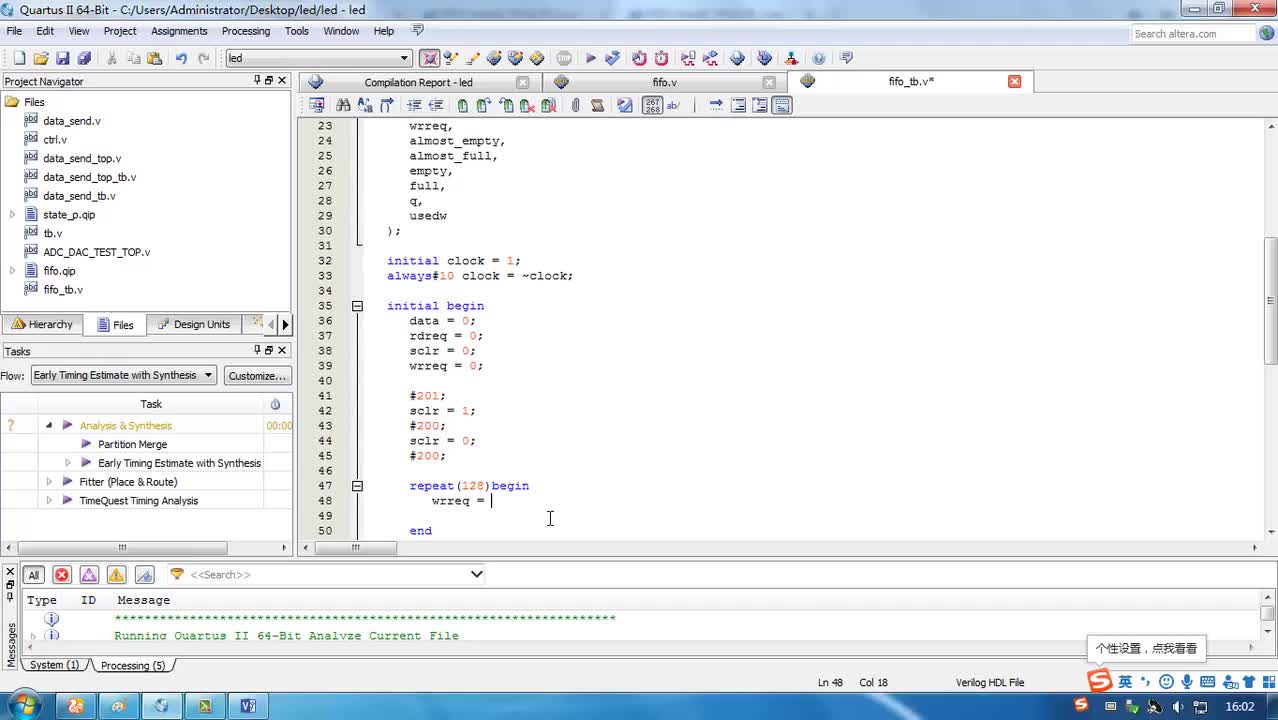

在仿真fft ip核時(shí) 輸出信號一直為0,檢查了輸入波形,應(yīng)該沒有問題,大家?guī)兔纯窗奢斎胧怯蓃om里面的mif文件產(chǎn)生的信號。

2017-11-21 10:44:53

有沒有大神可以提供xilinx FPGA的FFT IP核的調(diào)用的verilog 的參考程序,最近在學(xué)習(xí)FFT的IP核的使用,但是仿真結(jié)果有問題,所以想找些參考設(shè)計(jì),謝謝

2016-12-25 17:05:38

起來就是1001_1001,即為十進(jìn)制的153。這部分的具體應(yīng)用將在后面課程數(shù)碼管的使用一講中詳細(xì)闡述。圖5-17 兩級級聯(lián)計(jì)數(shù)值為10的計(jì)數(shù)器功能仿真波形圖至此就完成了一個(gè)基本的基本IP使用的流程。請以此為基礎(chǔ)自行設(shè)計(jì)使用其他IP核并進(jìn)行仿真以及板級驗(yàn)證。小梅哥芯航線電子工作室

2016-12-22 23:37:00

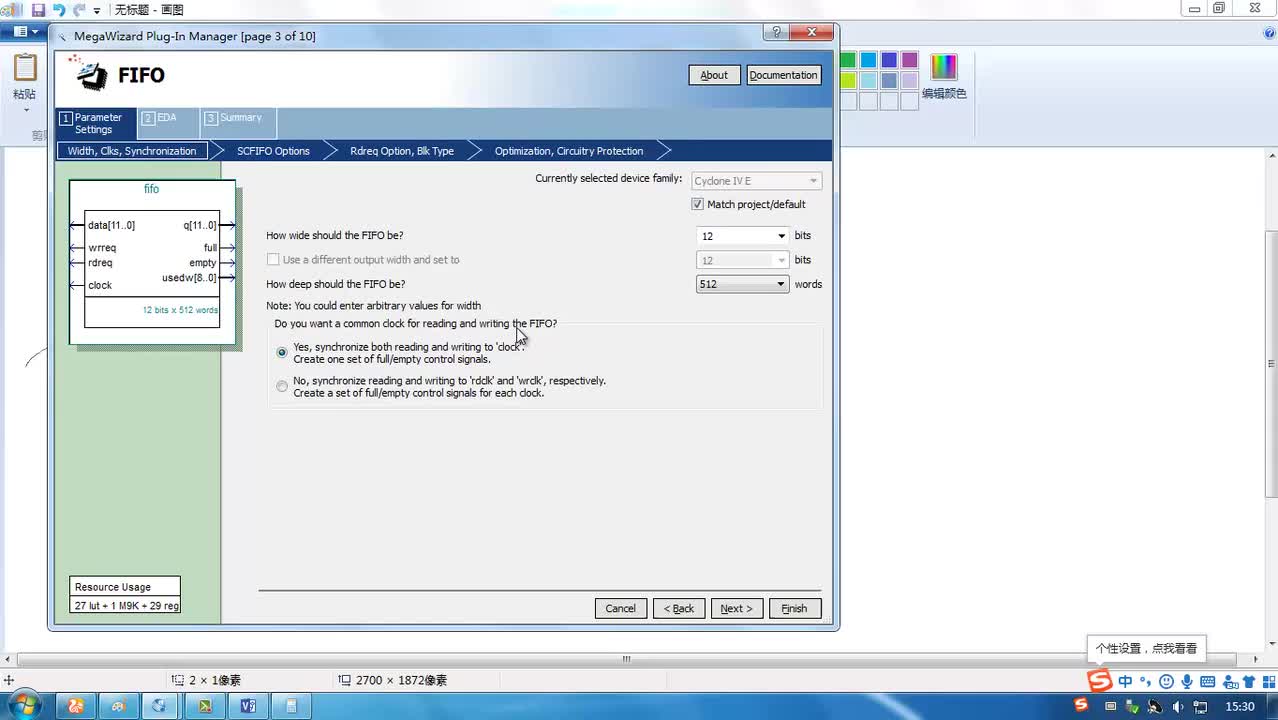

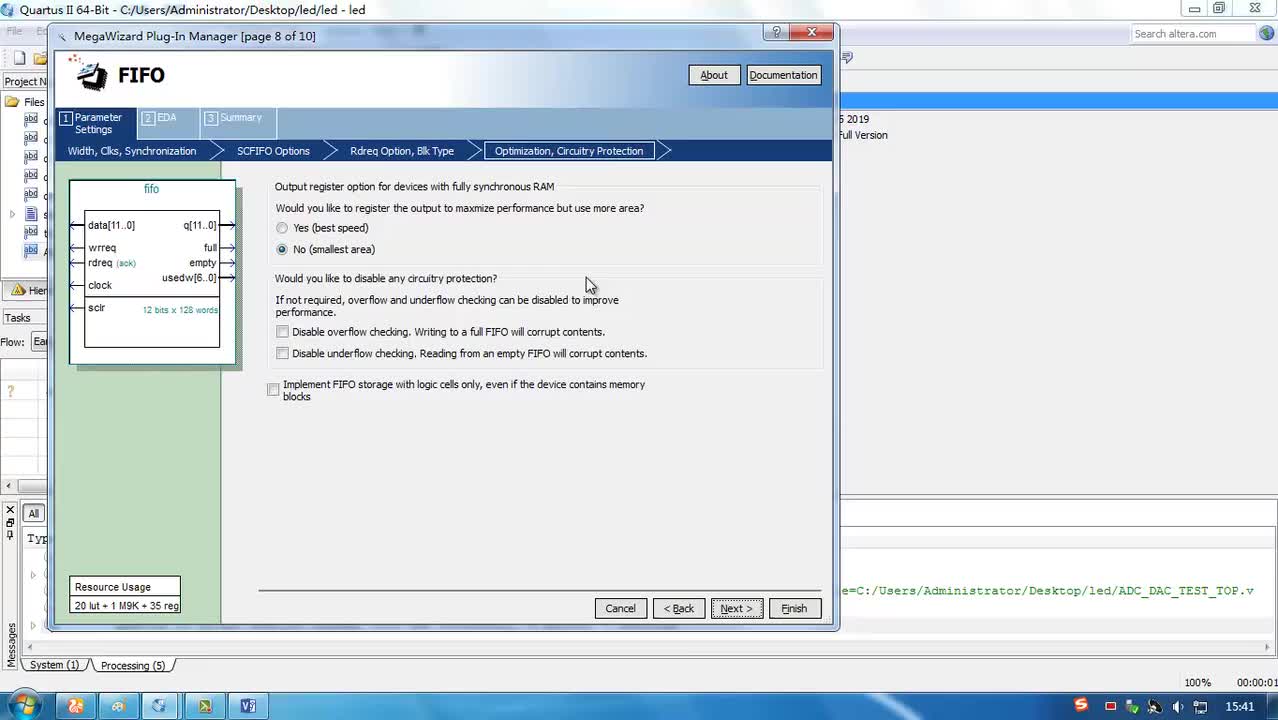

講,主要通過演示FPGA數(shù)字邏輯設(shè)計(jì)中除Verilog代碼方式設(shè)計(jì)外另外一種最常用的設(shè)計(jì)方式——使用IP核進(jìn)行系統(tǒng)設(shè)計(jì)。本教程講解了如何在Quartus II軟件中調(diào)用一個(gè)基本的免費(fèi)IP核——計(jì)數(shù)器IP核

2015-09-22 14:06:56

內(nèi)建的示波器。SignalTapⅡ的使用要新建一個(gè)仿真調(diào)試文件。SignalTapⅡ可以設(shè)定信號的觸發(fā)方式。其他請補(bǔ)充。另,FPGA的IP核并不是只有這幾種,從新建IP核的界面可以看到,IP核還有很多。

2016-10-11 22:24:16

的時(shí)鐘。首先建立一個(gè)文件在ip核目錄里搜索ALTPLL然后在工程文件的par文件里建立一個(gè)文件夾ipcore將剛剛的變化保存到文件里命名為pll_clk然后點(diǎn)擊ok就會(huì)出現(xiàn)配置過程界面FPGA系統(tǒng)晶振為

2020-01-13 18:13:48

大家好,我總是使用SRL16作為輸入同步器。但是最近我讀了這篇文章:http://forums.xilinx.com/t5/Inmplementation

2019-07-25 08:54:39

此時(shí)功能出現(xiàn)毛刺,可先不深究。圖5-12 計(jì)數(shù)值為10的功能仿真現(xiàn)在將IP核位數(shù)進(jìn)行更改為二進(jìn)制計(jì)數(shù),打開Mega Wizard插件管理器,選擇第二項(xiàng)編輯現(xiàn)有的IP核,并選擇先前生成的counter.v

2019-03-04 06:35:13

對于深入學(xué)習(xí)使用FPGA的小伙伴們,特別是一些復(fù)雜的、大規(guī)模的設(shè)計(jì)應(yīng)用,適宜的IP核對開發(fā)能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調(diào)用這些模塊

2024-04-29 21:01:16

最近進(jìn)行FPGA學(xué)習(xí),使用FIR濾波器過程中出現(xiàn)以下問題:使用FIR濾波器IP核中,輸入數(shù)據(jù)為1~256,濾波器系數(shù)為,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

在quartus II13.0版本上調(diào)用FFT IP核并進(jìn)行modelsim-altera仿真,在生成IP核時(shí),step2中勾選generate simulation model、generate

2016-10-07 22:23:33

和朋友開發(fā)了幾個(gè)基于 FPGA 的高速存儲(chǔ) IP 核,考慮到工業(yè)相機(jī)等應(yīng)用場合需要有文件系統(tǒng)以方便做數(shù)據(jù)管理,所以將 NVMe 和 exFAT 兩大IP核集成一起,可以實(shí)現(xiàn)將數(shù)據(jù)寫入SSD后,拔下

2022-06-03 11:35:06

基于FPGA的16位數(shù)據(jù)路徑的AESIP核提出一種基于FPGA 的16位數(shù)據(jù)路徑的高級加密標(biāo)準(zhǔn)AES IP核設(shè)計(jì)方案。該方案采用有限狀態(tài)機(jī)實(shí)現(xiàn),支持密鑰擴(kuò)展、加密和解密。密鑰擴(kuò)展采用非并行密鑰擴(kuò)展

2012-08-11 11:53:10

基于FPGA的IP核8051上實(shí)現(xiàn)TCPIP的設(shè)計(jì)

2012-08-06 12:18:28

我畢業(yè)設(shè)計(jì)要做一個(gè)基于FPGA的IP核的DDS信號發(fā)生器,但是我不會(huì)用DDS的IP核,有沒有好人能發(fā)我一份資料如何用IP核的呀。我的瀏覽器下載不了網(wǎng)站上的資料,所以只能發(fā)帖求幫忙了。

2015-03-10 11:46:40

Implement頁面中,可以對FPGA存儲(chǔ)器或乘法器相關(guān)的資源進(jìn)行選擇配置。在配置頁面左側(cè),可以查看IP接口(IP Symbol)、實(shí)現(xiàn)信號位寬細(xì)節(jié)(ImplementationDetails

2019-08-10 14:30:03

產(chǎn)生一組1000個(gè)點(diǎn)的余弦數(shù)據(jù),存放在time_domain_cos.txt文件中,這組數(shù)據(jù)將作為FPGA的仿真輸入激勵(lì),經(jīng)過FIR濾波器進(jìn)行濾波處理。clc;clear `all;closeall

2019-07-16 17:24:22

受到業(yè)內(nèi)人士的青睞。本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯(cuò)誤并對其進(jìn)行修改,最終完成了修改后IP核的FPGA下載測試。

2019-07-04 06:02:19

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進(jìn)行修改和定制,以提高設(shè)計(jì)效率[3]。本文研究了基于FPGA的數(shù)據(jù)采集控制器IP 核的設(shè)計(jì)方案和實(shí)現(xiàn)方法,該IP核既可以應(yīng)用在獨(dú)立IC芯片上,還可作為合成系統(tǒng)的子模塊直接調(diào)用,實(shí)現(xiàn)IP核的復(fù)用。

2019-07-09 07:23:09

核的分類和特點(diǎn)是什么?基于IP核的FPGA設(shè)計(jì)方法是什么?

2021-05-08 07:07:01

【摘要】:Viterbi譯碼器在通信系統(tǒng)中應(yīng)用非常普遍,針對采用DSP只能進(jìn)行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實(shí)現(xiàn)高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

如何仿真IP核(建立modelsim仿真庫完整解析)

2012-08-15 13:16:12

FPGA 架構(gòu)中的 SRL16 和觸發(fā)器是通過 GWE(全局寫使能)信號來釋放的,該信號允許這些同步元件在配置完成后改變狀態(tài)。GWE 是緊接配置后啟動(dòng)過程的一部分。

2019-09-03 08:10:58

本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯(cuò)誤并對其進(jìn)行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

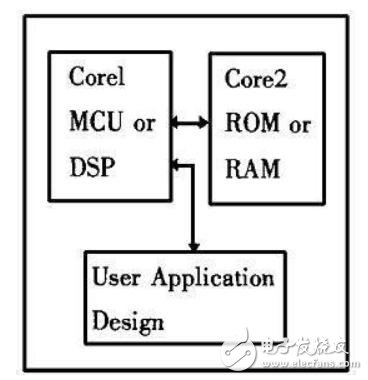

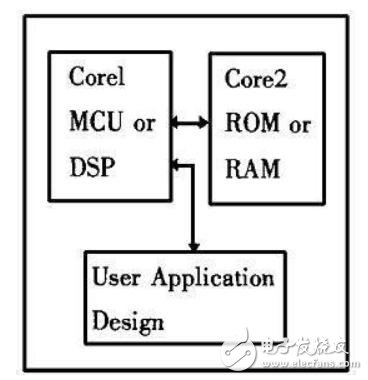

的其它設(shè)計(jì)部分盡量不相關(guān)。為了滿足上述的要求, 在FPGA中嵌入一個(gè)比較理想的選擇, 而這個(gè)即通用又控制簡單的IP核最好選擇8051微處理器。

2019-08-26 06:27:15

(InputData Width)和數(shù)據(jù)輸出順序(OutputOrdering)等。第三個(gè)Detailed Implement頁面中,可以對FPGA存儲(chǔ)器或乘法器相關(guān)的資源進(jìn)行選擇配置。在配置頁面左側(cè),可以查看

2020-01-07 09:33:53

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一個(gè)問題。比如說:某個(gè)IP,用于計(jì)算sin函數(shù),使用了流水線機(jī)制,所有從輸入到輸出需要20個(gè)時(shí)鐘周期的延時(shí)。另外,還有一個(gè)IP,從輸入到輸出需要1

2021-06-19 11:06:07

(Intellectual Property)核。IP核由相應(yīng)領(lǐng)域的專業(yè)人員設(shè)計(jì),并經(jīng)反復(fù)驗(yàn)證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設(shè)計(jì)者只需做很少設(shè)計(jì)就可實(shí)現(xiàn)所需系統(tǒng)。基于IP核的模塊化設(shè)計(jì)可縮短

2019-07-29 08:33:45

本文設(shè)計(jì)了一種基于 FPGA 的UART 核,該核符合串行通信協(xié)議,具有模塊化、兼容性和可配置性,適合于SoC 應(yīng)用。設(shè)計(jì)中使用Verilog HDL 硬件描述語言在Xilinx ISE 環(huán)境下進(jìn)行設(shè)計(jì)、仿真,

2009-11-27 15:48:51 20

20 用硬件實(shí)現(xiàn)數(shù)據(jù)加密已成為信息安全的主流方向。本文提出了一種基于FPGA 的低成本的AES IP核的實(shí)現(xiàn)方案。該方案輪內(nèi)部系統(tǒng)資源共用,減少了系統(tǒng)資源的占用。輸入密鑰與輸入數(shù)據(jù)

2010-01-06 15:11:03 11

11 USB設(shè)備接口IP核的設(shè)計(jì):討論了用Verilog硬件描述語言來實(shí)現(xiàn)USB設(shè)備接口IP核的方法,并進(jìn)行了FPGA的驗(yàn)證。簡要介紹USB系統(tǒng)的體系結(jié)構(gòu),重點(diǎn)描述USB設(shè)備接口IP核的結(jié)構(gòu)劃分和各模塊的

2010-01-08 18:15:38 22

22 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設(shè)計(jì),給出了該IP核的系統(tǒng)結(jié)構(gòu)以及各個(gè)子模塊的詳細(xì)設(shè)計(jì)方法,并對該IP核進(jìn)行了功能仿真、FPGA原型驗(yàn)證,可測性設(shè)計(jì)以

2010-07-17 16:20:22 21

21 本文主要介紹了一種利用FPGA IP核設(shè)計(jì)線性調(diào)頻信號脈沖壓縮的方法,通過各種仿真與實(shí)際測試表明脈沖壓縮結(jié)果正確。這種基于IP核的模塊化設(shè)計(jì)方法非常靈活,參數(shù)的設(shè)置和修改方便

2011-06-29 10:40:20 14238

14238

FPGA架構(gòu)中的 SRL16 和觸發(fā)器是通過 GWE(全局寫使能)信號來釋放的,該信號允許這些同步元件在配置完成后改變狀態(tài)。GWE 是緊接配置后啟動(dòng)過程的一部分。

2011-12-09 15:43:27 1283

1283 The SRL16E was introduced in the Virtex FPGA architecture and is included in allvariants

2012-02-17 15:03:32 0

0 以Altera公司的Quartus Ⅱ 7.2作為開發(fā)工具,研究了基于FPGA的DDS IP核設(shè)計(jì),并給出基于Signal Tap II嵌入式邏輯分析儀的仿真測試結(jié)果。將設(shè)計(jì)的DDS IP核封裝成為SOPC Builder自定義的組件,結(jié)合

2012-04-05 16:04:34 85

85 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實(shí)用挺不錯(cuò)的資料

2015-11-30 17:36:15 12

12 FPGA的IP核設(shè)計(jì)技術(shù)的系列資料,大家可以收集看下,這些都是我看過過濾后留下的,感覺不錯(cuò),希望對大家有幫助

2015-11-30 17:49:01 6

6 MC8051_IP核簡單指令的仿真步驟。

2016-05-06 11:47:41 0

0 利用FPGA的IP核設(shè)計(jì)和實(shí)現(xiàn)FFT算法

2016-05-24 14:14:47 37

37 Xilinx FPGA工程例子源碼:PCI Express IP核應(yīng)用參考設(shè)計(jì)

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 引入IP核的三維FPGA結(jié)構(gòu)研

2017-01-07 20:32:20 2

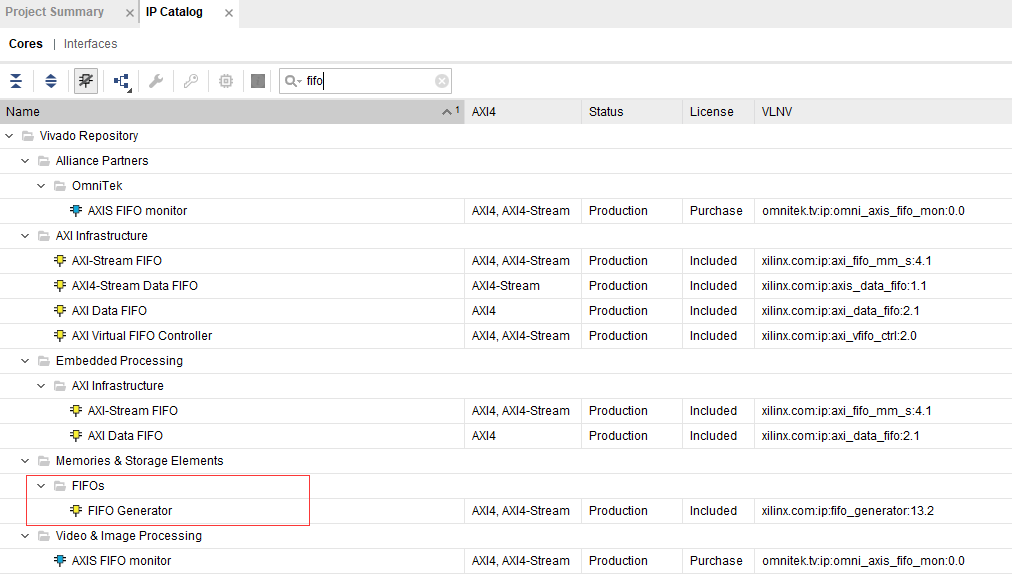

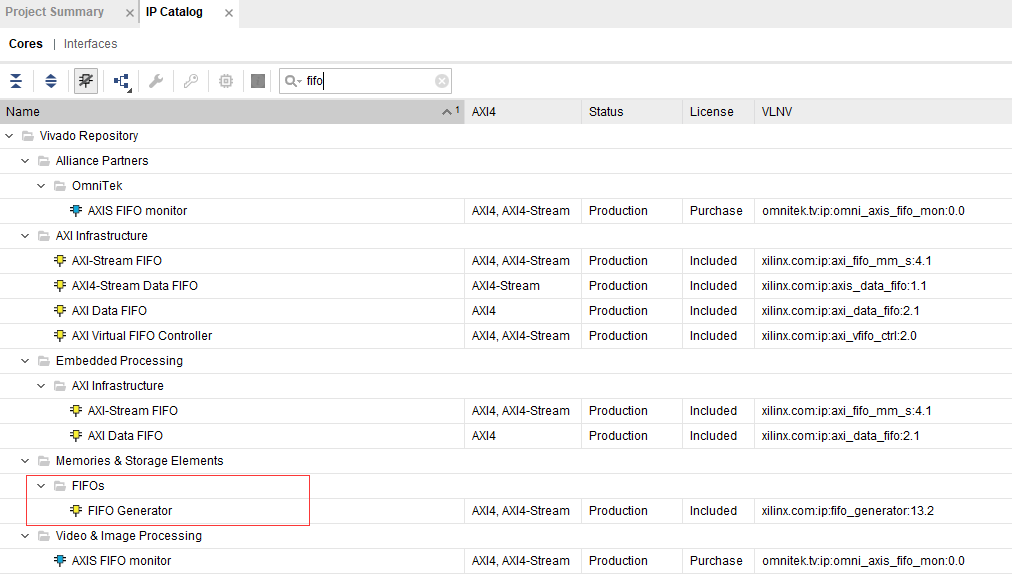

2 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言

2017-11-15 11:19:14 10744

10744 基于SRL16的分布式RAM不再支持V5、S6和V6等器件,但是SRL16是所有XIlinx器件都支持的,并且在設(shè)計(jì)中應(yīng)用非常頻繁,因此可通過調(diào)用原語的方法來調(diào)用SRL16E甚至SRL32E來實(shí)現(xiàn)原來ISE分布式RAM IP核的設(shè)計(jì)。

2018-05-05 10:38:00 7848

7848 對于IP核輸出數(shù)據(jù)的解析最好的工具就是其自帶的仿真文件,里面既將接收的數(shù)據(jù)進(jìn)行了解析,又將發(fā)送給IP核的數(shù)據(jù)進(jìn)行了封裝,這對于了解數(shù)據(jù)結(jié)構(gòu)和協(xié)議是十分有幫助的,以太網(wǎng)如此,pcie、ram、fifo等其它IP也如此,我們只需將ip自帶的仿真文件改為我們自己的邏輯即可,接口連接并不變。

2018-07-09 14:07:00 4234

4234 大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來聊一聊使用matlab和ISE 創(chuàng)建并仿真ROM IP核。本人想使用簡單的中值濾波進(jìn)行verilog相關(guān)算法的硬件實(shí)現(xiàn),由于HDL設(shè)計(jì)軟件不能直接處理圖像

2018-10-25 20:20:35 4559

4559

介紹了在大型工業(yè)模擬仿真系統(tǒng)中,利用FPGA和軟IP核實(shí)現(xiàn)數(shù)據(jù)采集及收發(fā)控制的方案,并對其進(jìn)行設(shè)計(jì)實(shí)現(xiàn)。重點(diǎn)闡述了在發(fā)送指令和采集接收兩種數(shù)據(jù)流模式下.該IP核的控制處理邏輯及工作狀態(tài)機(jī)的設(shè)計(jì)及實(shí)現(xiàn)

2018-11-07 11:14:19 20

20 , 用戶綜合出的網(wǎng)表和設(shè)計(jì)約束文件一起輸入給FPGA 布局布線工具, 完成FPGA 的最后實(shí)現(xiàn), 并產(chǎn)生時(shí)序文件用于時(shí)序仿真和功能驗(yàn)證。

2019-06-02 10:45:31 4182

4182

? Xilinx公司的FPGA中有著很多的有用且對整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 OpenCores網(wǎng)站提供的OC8051 IP核與8051的系統(tǒng)結(jié)構(gòu)相同,如圖1所示。該IP核兼容所有8051指令系統(tǒng),內(nèi)部資源包括:8位CPU,尋址能力達(dá)2×64K;4 KB的ROM和128字節(jié)

2020-09-28 23:35:52 2272

2272

SRL(移位寄存器)資源,在FPGA中都有,不過是叫不同的名字。Xilinx FPGA內(nèi)部的LUT有個(gè)特殊功能,就是可以配置成可變長度SRL。

2020-12-31 16:45:35 9

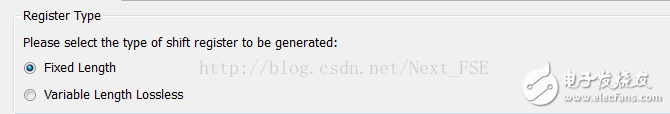

9 FPGA開發(fā)過程中是免不了要用到移位寄存器的,傳統(tǒng)的移位寄存器是通過寄存器(或者叫觸發(fā)器)實(shí)現(xiàn)的,占用的是FPGA內(nèi)部的邏輯資源,當(dāng)要移位的次數(shù)過多時(shí),自然會(huì)耗費(fèi)更多資源。但是如果用LUT(look

2020-12-31 16:45:34 20

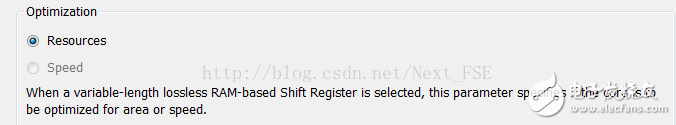

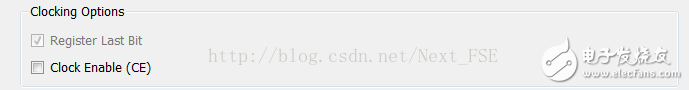

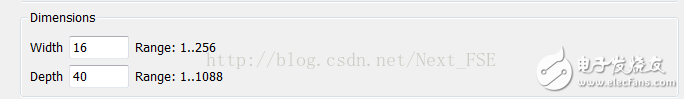

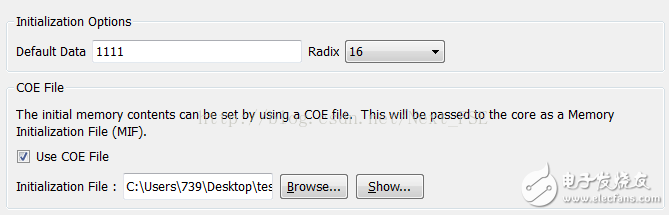

20 這個(gè)參數(shù)確定的是移位寄存器的移位時(shí)鐘個(gè)數(shù)。這個(gè)時(shí)鐘個(gè)數(shù)取決于后面的Depth參數(shù)。其中第一個(gè)參數(shù)Fixed Length 指的是移位周期數(shù)是固定的(后面的Depth指定)。第二個(gè)參數(shù)指的是可變長度的,也就是說移位寄存器的移位長度是可變的,至于長度究竟是多少,那就得看下面的參數(shù)Depth了,這個(gè)Depth代表的是移位寄存器的最大移位長度(因?yàn)槭强勺兊模绻x擇這一項(xiàng)的話就意味著會(huì)啟用一個(gè)外接寄存器來控制移位的真正長度,也就是A[]寄存器,這個(gè)輸

2020-12-31 16:45:00 10

10 IP即產(chǎn)權(quán),包含產(chǎn)品、工藝、技術(shù)及軟件等受到專利版權(quán)及商業(yè)機(jī)密等的保護(hù)IP核類型軟核通常是用HDL文本形式提交給用戶,它經(jīng)過RT級設(shè)計(jì)優(yōu)化和功能驗(yàn)證,但其中不含任何具體的物理據(jù)軟核,用戶可以綜合

2021-01-20 16:27:59 17

17 前年,發(fā)表了一篇文章《VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時(shí)遇到的一些問題及解決方案,發(fā)表之后經(jīng)過一年多操作上也有

2021-03-22 10:31:16 5360

5360 IP核目前的IP設(shè)計(jì)已成為目前FPGA設(shè)計(jì)的主流方法之一,應(yīng)用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數(shù)據(jù)塊。IP核在SoC中的集成方式及應(yīng)用場景,芯片設(shè)計(jì)中的IP核具有特定功能的可復(fù)用的標(biāo)準(zhǔn)性和可交易性,已經(jīng)成為集成電路設(shè)計(jì)技術(shù)的核心與精華。

2021-10-01 09:08:00 3100

3100 ARTIX-xlinx 版本FPGA 串口通信模塊(含IP核)

2022-06-20 11:07:28 16

16 前年,發(fā)表了一篇文章《VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時(shí)遇到的一些問題及解決方案,發(fā)表之后經(jīng)過一年多操作上也有些許改進(jìn),所以寫這篇文章補(bǔ)充下。

2022-08-29 14:41:55 4676

4676 今天介紹的是vivado的三種常用IP核:時(shí)鐘倍頻(Clocking Wizard),實(shí)時(shí)仿真(ILA),ROM調(diào)用(Block Memory)。

2023-02-02 10:14:01 5002

5002 使用VCS仿真Vivado里面的IP核時(shí),如果Vivado的IP核的仿真文件只有VHDL時(shí),仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 3576

3576

在仿真Vivado IP核時(shí)分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

的不同模塊進(jìn)行實(shí)體/塊的仿真。前文回顧如何測試與驗(yàn)證復(fù)雜的FPGA設(shè)計(jì)(1)——面向?qū)嶓w或塊的仿真在本篇文章中,我們將介紹如何在虹科IP核中執(zhí)行面向全局的仿真,而這也是測

2022-06-15 17:31:20 1373

1373

FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復(fù)用的設(shè)計(jì)模塊或功能片段。它們是預(yù)先編寫好的硬件設(shè)計(jì)代碼,可以在FPGA芯片上實(shí)現(xiàn)特定的功能。

2023-07-03 17:13:28 8969

8969 FPGA開發(fā)過程中,利用各種IP核,可以快速完成功能開發(fā),不需要花費(fèi)大量時(shí)間重復(fù)造輪子。

2023-08-07 15:43:19 1992

1992

,一旦寫入不能再修改或刪除,斷電不丟失。我們知道FPGA只有RAM,因此事實(shí)上在 FPGA 中通過 IP 核生成的 ROM 或 RAM掉電內(nèi)容都會(huì)丟失。用 IP 核生成的 ROM 模塊只是提前添加

2023-08-22 15:06:38 7616

7616

Xilinx公司的FPGA中有著很多的有用且對整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的時(shí)候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

本文介紹了Vidado中FFT IP核的使用,具體內(nèi)容為:調(diào)用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數(shù)據(jù)>>測試verilogHDL>>TestBench仿真>>結(jié)果驗(yàn)證>>FFT運(yùn)算。

2024-11-06 09:51:43 5640

5640

電子發(fā)燒友App

電子發(fā)燒友App

評論