Distributed Memory Generator IP 核采用 LUT RAM 資源創建各種不同的存儲器結構。IP可用來創建只讀存儲器 (ROM)、單端口隨機存取存儲器 (RAM) 和簡單雙/雙端口 RAM 以及基于 SRL16 的 RAM。該IP的靈活的特性配置方式,使用戶能針對存儲器類型、數據寬度、存儲器大小、輸入/輸出選項和復位選項進行定制。

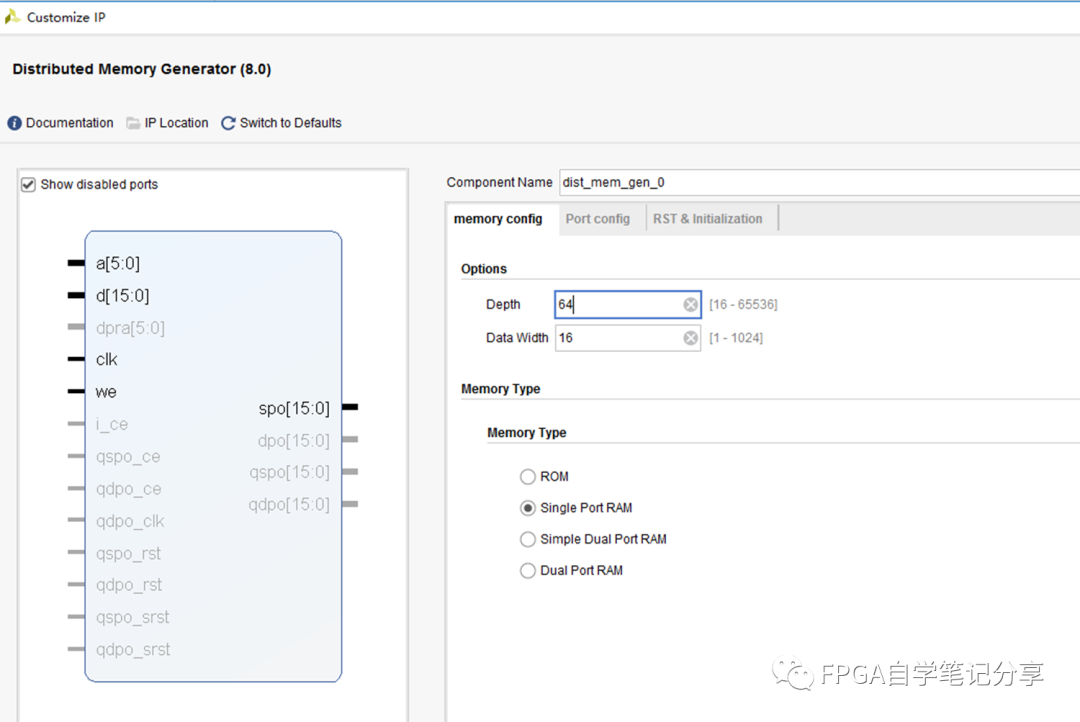

Distributed Memory Generator IP GUI界面如下:

該IP的主要特性為:

- 生成只讀存儲器 (ROM)、單、簡單雙和雙端口隨機存取存儲器 (RAM)以及基于SRL16 的 RAM;

- 支持 16 到 65536 的數據深度;

- 支持1 到 1024 之間的數據寬度;

- 可選的寄存輸入和輸出;

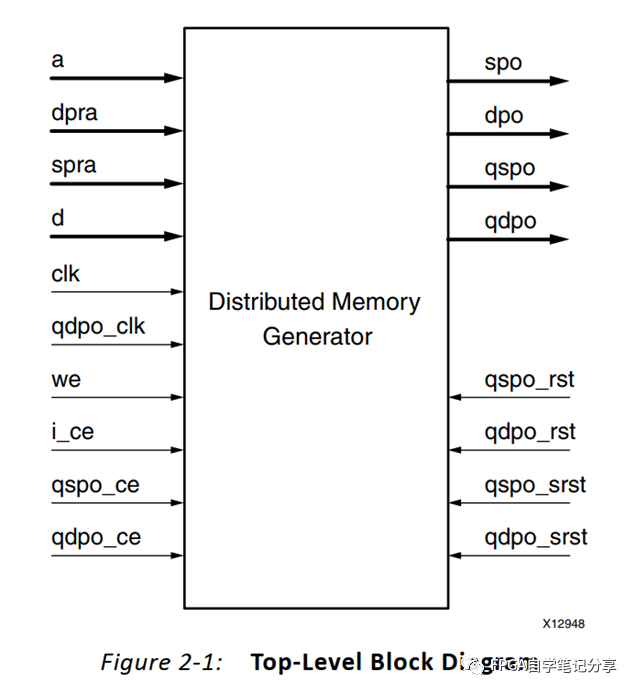

這個IP的端口如下圖所示:

輸入:

a:地址輸入;

Dpra:雙端口時的讀地址;

d:數據輸入;

Clk:時鐘

Qdpo_clk:雙端口模式下的第二個時鐘

We:寫使能

i_ce:輸入時鐘使能;

Qspo_ce:輸出時鐘使能;

Qdpo_ce:第二個端口的輸出時鐘使能;

輸出:

Spo:非寄存器模式下第一個端口的輸出數據

Dpo:非寄存器模式下第二個端口的輸出數據

Qspo:寄存器模式下第一個端口的輸出數據

Qdpo:寄存器模式下第二個端口的輸出數據

復位:

qspo_rst :寄存器模式下第一個端口的異步復位

qdpo_rst :寄存器模式下第二個端口的異步復位

qspo_srst:寄存器模式下第一個端口的同步復位

qdpo_srst :寄存器模式下第二個端口的同步復位

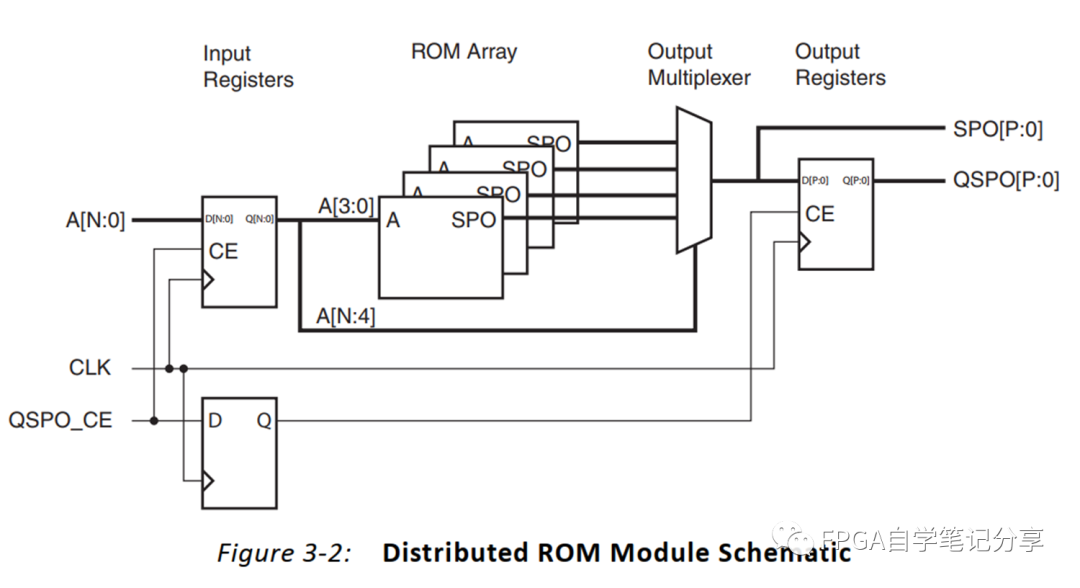

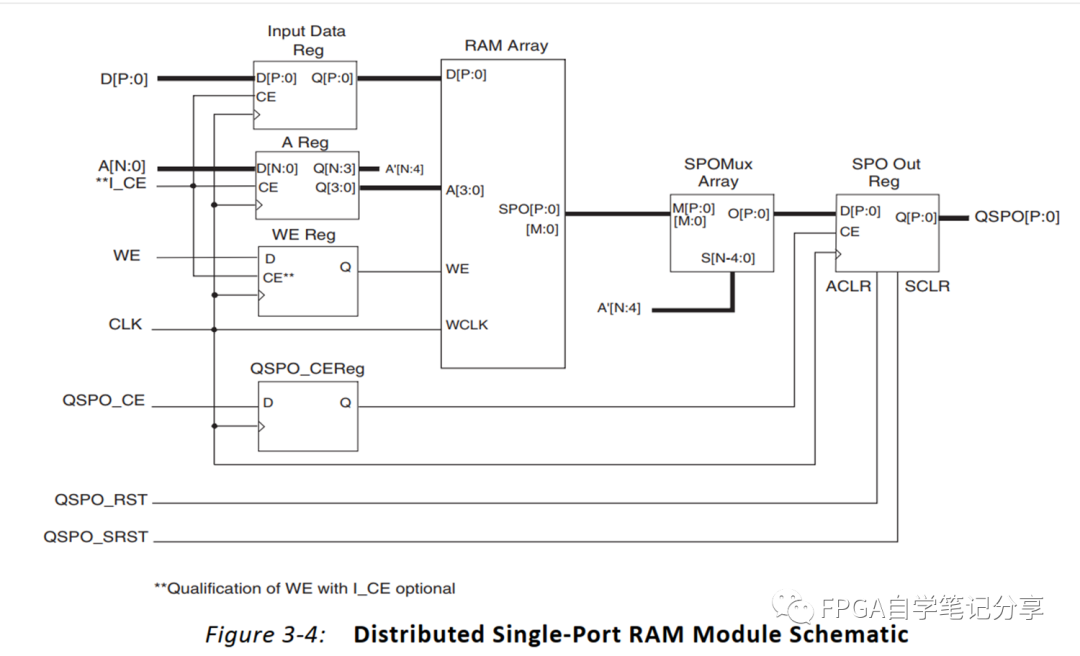

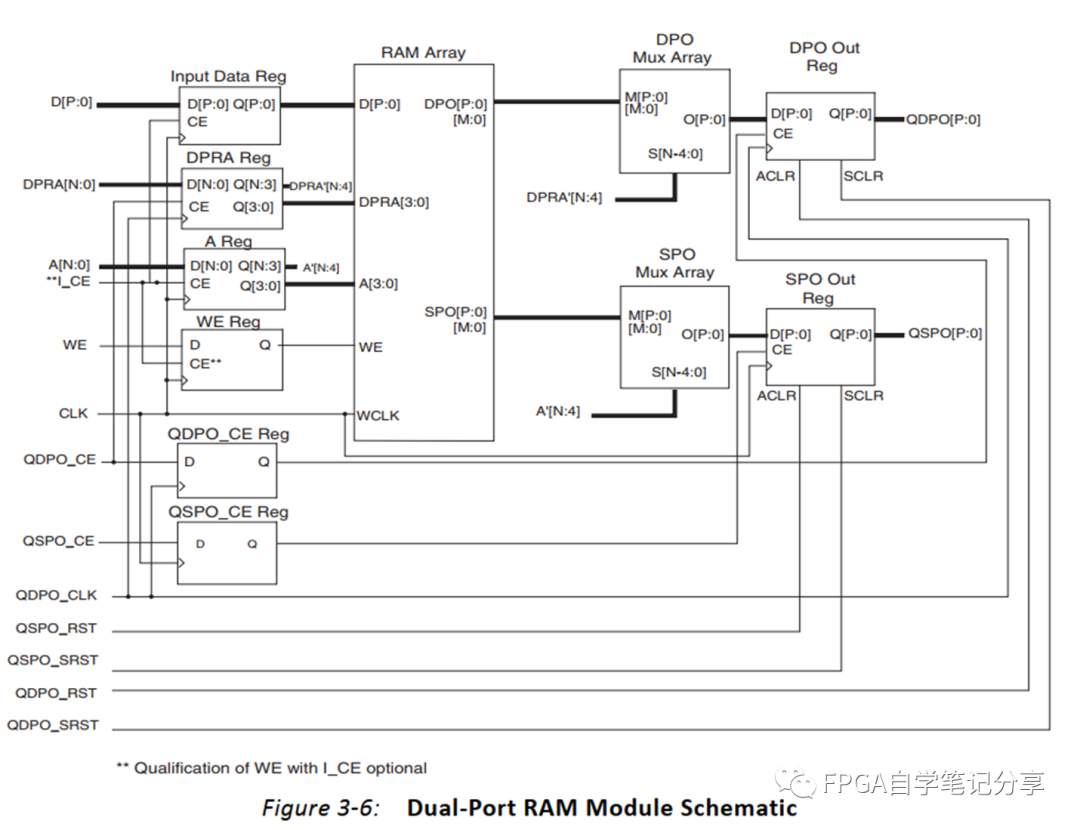

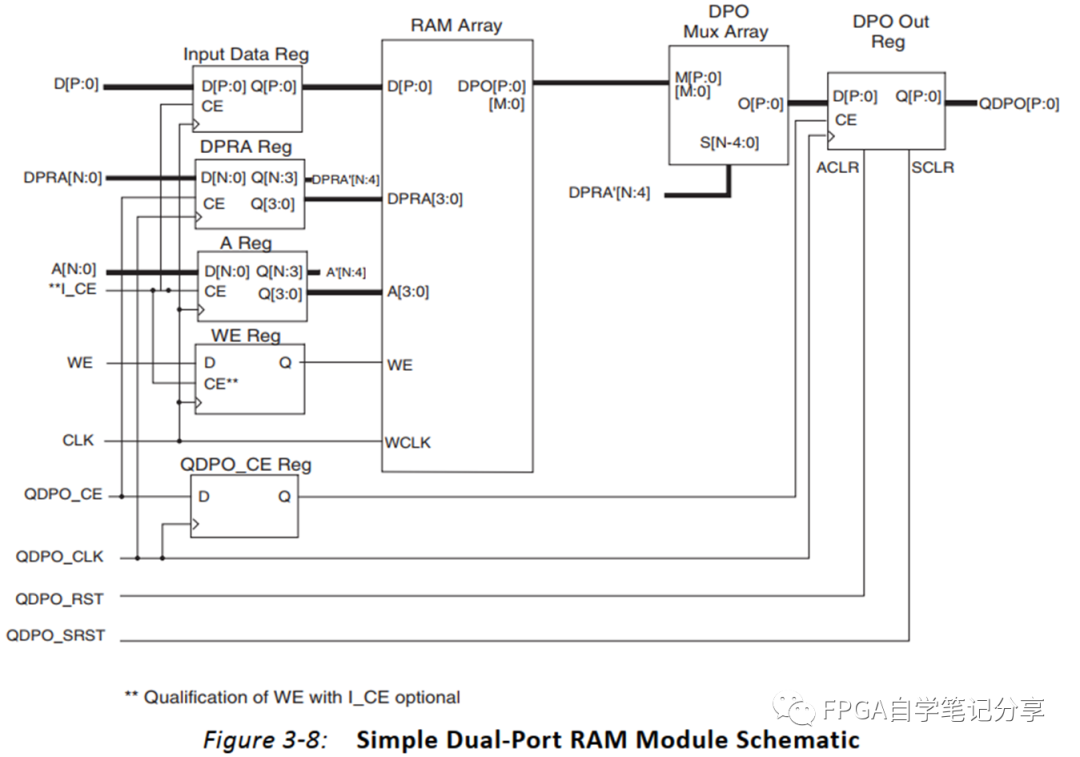

Distributed Memory在不同工作模式下的內部情況如下圖所示:

ROM模式:

單端口RAM模式:

雙端口RAM模式:

簡單雙端口模式:

一般情況下常用簡單雙端口模式進行跨時鐘域,簡單緩存的操作。用簡單雙端口實現一個簡單的跨時鐘域代碼如下:

// ============================================================

// File Name: tb_dist_mem_gen

// VERSION : V1.0

// DATA : 2023/8/18

// Author : FPGA干貨分享

// ============================================================

// 功能:xilinx Distributed Memory Generator ip 代碼仿真

// 使用簡單雙端口實現一個簡單的跨時鐘域

// delay :

// ============================================================

`timescale 1ns/100ps

module tb_dist_mem_gen ;

reg clka = 'd0 ;

reg ena = 'd1 ;

reg [0 : 0] wea = 'd1 ;

reg [5 : 0] addra = 'd0 ;

reg [15 : 0] dina = 'd0 ;

reg clkb = 'd1 ;

reg enb = 'd1 ;

reg [5 : 0] addrb = 'd0 ;

wire [15 : 0] doutb ;

reg [2:0] S_addr_a_flag ='d0 ;

reg S_a_flag ='d0 ;

reg [2:0] S_a_flag_2_b ='d0 ;

reg S_b_flag ='d0 ;

reg [2:0] S_clk_cnt8 ='d3 ;

always #1 clka = ~clka;

always #1 clkb = ~clkb;

//----------- clk_a ---//

always @(posedge clka)

if(ena && wea)

begin

addra <= addra + 'd1;

dina <= dina + 'd1;

end

always @(posedge clka)

S_addr_a_flag[0] <= (addra == 6'd10);

always @(posedge clka)

S_addr_a_flag[2:1] <= S_addr_a_flag[1:0] ;

always @(posedge clka)

S_a_flag <= |S_addr_a_flag ;

//----------- clk_b ---//

always @(posedge clkb)

S_a_flag_2_b <= {S_a_flag_2_b[1:0],S_a_flag} ;

always @(posedge clkb)

S_b_flag <= (!S_a_flag_2_b[2])&& S_a_flag_2_b[1] ;

always @(posedge clkb)

if((S_clk_cnt8 > 3'd2)&&S_b_flag)

S_clk_cnt8 <= 3'd2;

else

S_clk_cnt8 <= S_clk_cnt8 + 'd1;

always @(posedge clkb)

if(S_clk_cnt8 == 3'd1)

addrb <= 'd0;

else

addrb <= addrb + 'd1;

dist_mem_gen_0 dist_mem_gen_0 (

.a (addra ), // input wire [5 : 0] a

.d (dina ), // input wire [15 : 0] d

.dpra (addrb ), // input wire [5 : 0] dpra

.clk (clka ), // input wire clk

.we (wea ), // input wire we

.qdpo_clk (clkb ), // input wire qdpo_clk

.qdpo (doutb ) // output wire [15 : 0] dpo

);

endmodule

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636233 -

存儲器

+關注

關注

39文章

7738瀏覽量

171650 -

RAM

+關注

關注

8文章

1399瀏覽量

120546 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131123 -

IP核

+關注

關注

4文章

344瀏覽量

51945

發布評論請先 登錄

相關推薦

熱點推薦

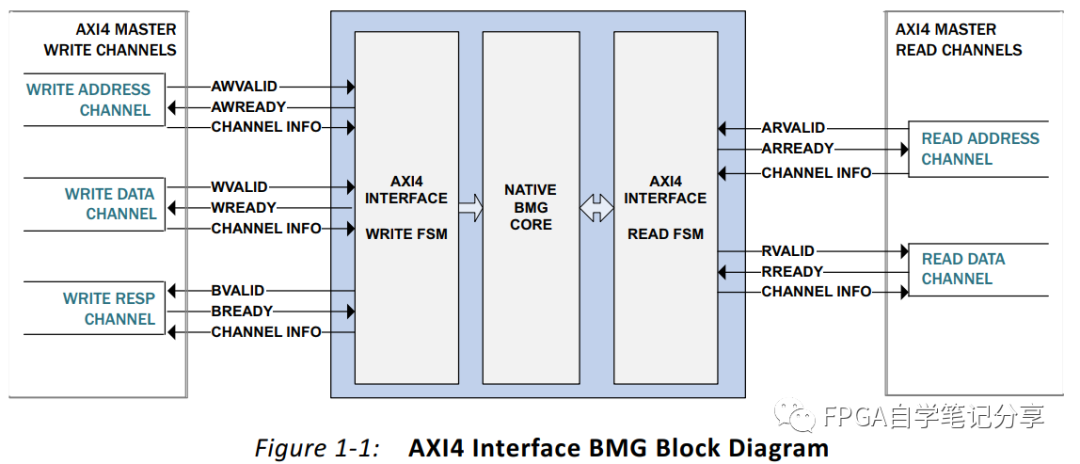

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

Xilinx FPGA IP之Block Memory Generator AXI接口說明

之前的文章對Block Memory Generator的原生接口做了說明和仿真,本文對AXI接口進行說明。

VDMA IP核簡介

;

S_AXIS_MM2S:IP核的FIFO生成視頻流(AXI STREAM)輸出到后端;

S_AXI_S2MM:IP核的FIFO中的像素數據存入

發表于 10-28 06:14

ISE不能生成IP核

'.Failed executing Tcl generator.然后我新建工程,添加IPcore時也是這個錯誤,現在添加IP核時都是這個錯誤。我百度有個人有同樣的問題,他說解決了,但說的我不是很明白

發表于 09-07 12:21

ARM embedded memory ip的產生,couldn't run spreadsheet generator to fetch results

如題,在Linux下,產生memory,使用的是ARM的 memory IP 工具,無法產生,提示:couldn't run spreadsheet generator to fetc

發表于 08-15 15:56

如何使用System Generator來創建自己的IP核

嗨,我正在嘗試學習如何使用System Generator來創建自己的IP核。首先,我在DocNav中找到了一個ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“

發表于 05-22 07:22

ARM memory_compiler sram ip生成問題怎么解決呢

ARM memory_compiler ip的產生,couldn't run spreadsheet generator to fetch results,這類問題怎么解決呢?????

發表于 09-28 10:22

如何在ISE中更新老版本的IP核

the selected IP Block_Memory_Generator v3.1 to a more recent version.

發表于 02-11 10:58

?4819次閱讀

如何將IP模塊整合到System Generator for DSP中

了解如何將Vivado HLS設計作為IP模塊整合到System Generator for DSP中。

了解如何將Vivado HLS設計保存為IP模塊,并了解如何將此IP輕松整合

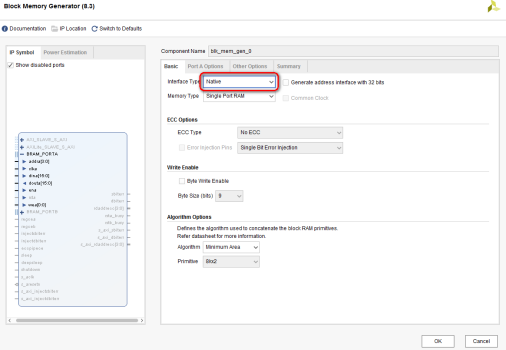

Vivado中xilinx_BRAM IP核使用

Vivado2017.2 中BRAM版本為 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5種類型:Single-p

發表于 03-10 06:15

?19次下載

FPGA應用之vivado三種常用IP核的調用

今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

發表于 02-02 10:14

?5075次閱讀

Distributed Memory Generator IP核簡介

Distributed Memory Generator IP核簡介

評論