FPGA(現場可編程門陣列)技術的理論研究和實際應用正越來越受到人們的重視。FPGA 技術常常使一些原來比較難解決的技術瓶頸得以輕松實現,從而使產品的開發周期大為縮短,性能價格比大幅提高。運算器作為計算機的加工處理部件,是CPU(中央處理器)的重要組成部分。作為典型的PC機一般都至少具有一個定點運算器。在586 之前的機型中,由于當時硬件條件和工藝的限制,浮點運算器一般以協處理器的形式出現。進入20 世紀90 年代后,隨著工藝水平的提高,一個芯片上集成度不斷提高,如今浮點運算所要求的一些硬件已可以集成到CPU 中,因此,作為浮點運算器的代表的協處理器也逐漸被集成度很高的CPU 中的一部分所代替。

浮點運算

定點運算器主要是用于實現對定點整數和定點小數的算術運算、對邏輯數據的邏輯運算以及對主存的地址計算等。

浮點數比定點數的表述范圍寬,有效精度高,更適合于科學計算與工程計算。浮點運算可分為兩類:非規格化和規格化浮點運算。非規格化浮點運算,不要求操作數是規格化數,對運算結果也不要求規格化處理。而規格化浮點運算只能對規格化的浮點數進行操作,并且要求對運算結果加以規格化處理。由于規格化浮點數具有惟一的表示形式,而且在計算機中尾數能獲得最大的有效數字,所以在一般的計算機中一般選用規格化浮點運算。

浮點加、減運算

浮點加減法運算規則

設有兩個浮點數x 和y,分別為

其中Ex 和Ey 分別為數x 和y 的階碼,Mx 和My 分別是數x 和y 的尾數。

兩浮點數進行加減的運算規則是

浮點加減法運算步驟

完成兩個浮點數加法或減法運算,需要以下幾個步驟完成。

(1) 對階:兩浮點數進行加減,必須使它們的階碼相等,這個過程稱為對階。對階的第1 步是求階差:

對階的規則是小階向大階看齊,即使階碼小的尾數向右移位,每右移一位階碼加1,直至兩數的階碼相等( E=0)為

止。右移的位數等于階差| E|。當然尾數右移也會發生數碼丟失,但這時丟失的僅僅是尾數的低位部分,誤差較小,而且

可以通過舍入方法來控制誤差。

(2)求和或求差:按定點加減的規則求兩尾數的和或差。這個過程中所使用運算邏輯單元與定點運算邏輯單元類似。

(3)規格化:求和之后得到的數可能不是規格化的數,為了增加有效數字的位數,提高運算精度,必須將求和的結果規

格化。

當尾數用二進制表示時,浮點規格化的定義是尾數M 應滿足:

(4)溢出判斷:在進行運算時,可能出現階碼溢出的情況。當階碼超出上限時,稱為階碼上溢,它表示浮點數的絕對值超出表述范圍。當階碼小于下限時,稱為階碼下溢,它表示浮點數的絕對值已在浮點數表示的分辨率之下。通常階碼上溢時要進行相應的處理,階碼下溢時要當作機械零處理。

浮點乘、除運算

浮點乘除法運算規則

兩浮點數乘法的運算規則是

即兩浮點數相乘,其乘積的階碼為相乘兩數的階碼之和,其乘積的尾數為相乘兩數尾數之積。

兩浮點數除法的運算規則是

即兩浮點數相除,商的階碼為被除數的階碼減去除數的階碼所得到的差,尾數為被除數的尾數除以除數的尾數所得

的商。

浮點乘除法運算步驟

兩個浮點數乘除運算步驟為: 完成兩浮點數階碼的加減運算,并判斷結果是否溢出; 完成兩浮點數尾數的乘除運

算; 根據結果的階碼判斷溢出,如果上溢則置溢出標志。

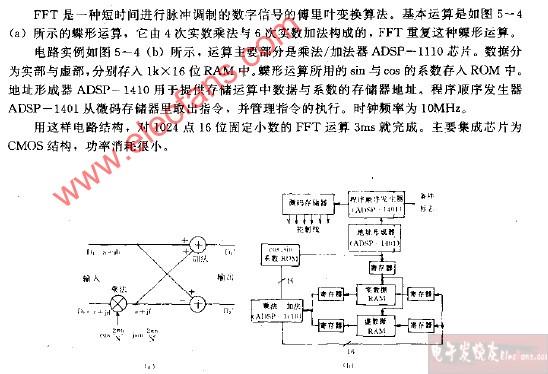

浮點運算器的設計與實現

硬件平臺

浮點運算器的設計與實現都是在開發的多功能EDA 實驗臺上完成的。該EDA 實驗臺采用FPGA-XC4010EPC84、

62256CPLD 和其它外圍芯片(例如74LS244,74LS275)組成。XILINX 公司XC4000 系列是高容量、高成本的FPGA,能夠進行無限次重新編程,配合公司的相應軟件FOUNDATION 3.1,用戶可以設計和調試出具有相當功能的控制邏輯。根據不同的要求,規劃不同控制邏輯,通過把控制邏輯下載到FPGA 芯片中構成自己的硬件平臺。

基于VHDL 語言方式

VHDL 語言具有極強的描述覆蓋能力,在使用VHDL 語言實現的過程中,我們采用自頂向下的方法來實現浮點運算

器。步驟如下:

(1)分析系統的內部結構并進行系統劃分,確定各個模塊的功能和接口。

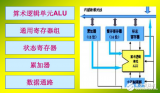

在設計中,根據浮點運算器的功能,將其劃分為時序產生模塊、浮點數輸入模塊、浮點運算模塊和結果輸出模塊4 個模

塊來實現。浮點運算器邏輯框圖如圖1 所示。

將這4 個模塊組合成頂層設計float_alu,該頂層設計的端口定義分別為

(2)根據浮點運算器各模塊的功能,分別編寫程序,輸入VHDL 代碼,并將其編譯成標準的VHDL 文件。

時序產生模塊:該模塊功能是對系統時鐘進行分頻產生相應的時鐘信號。本模塊中使用計數器級連的方法實現分頻。

浮點數輸入模塊:開關sel_1 和sel_2 為輸入數據的觸發信號。多功能EDA 實驗臺上其余開關對應于8 位尾數和4 位階碼輸入。當sel_1 開關按下,即sel_1=‘1’時,輸入開關中的數據作為第1 組輸入數的8 位尾數和4 位階碼;當sel_2 開關按

下,即sel_2=‘1’時,輸入開關中的數據作為第2 組輸入數的8位尾數和4 位階碼。在該模塊中用進程process (sel_1)和process(sel_2)來實現。

浮點運算模塊:該模塊主要完成各種浮點運算,是整個系統的核心部分。根據輸入功能選擇按鍵,在start_clk 信號上升

沿的觸發下,對輸入的兩組浮點數進行運算。浮點運算模塊的流程圖如圖2 所示。規格化浮點數加減運算流程圖如圖3

所示,規格化浮點數乘除運算流程圖如圖4 所示。

結果輸出模塊:該模塊的功能是將浮點運算的結果輸出至多功能EDA 實驗臺相應的發光二極管,以供觀測。

(3)VHDL 源代碼進行綜合優化處理。經過上述分析后,用VHDL 語言對各個模塊進行描述和實現,最后對VHDL 源

代碼進行綜合優化處理。

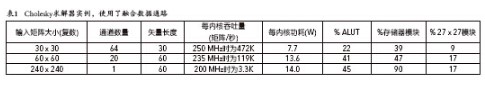

(4)仿真與配置。設計的正確性可以通過仿真來驗證。圖5 是浮點減法的時序仿真圖。圖5 中的信號定義如表1 所

示。其它各種運算的時序仿真方法相同,在此不再描述。

綜合優化處理后的VHDL程序經仿真正確后再將生成的位流(bit)文件配置到到FPGA 的邏輯單元陣列,以定義器件

內的邏輯功能塊和其互連的功能。

(5)下載驗證。將步驟(4)得到的器件編程文件下載到目標芯片中,進行硬件的測試。浮點運算的結果顯示在多功能

EDA實驗臺相應的發光二極管上,通過觀測,可以證實所設計的浮點運算器是正確的。

基于原理圖方式

采用原理圖方式設計一個浮點運算器,首先必須分析出運算器的組成,然后使用基本的邏輯門和觸發器來實現。

根據前面的分析可知,浮點四則運算比起定點運算來要復雜一些。在浮點運算中,階碼和尾數是分別進行運算的,并

且都是定點數(階碼為定點整數,尾數為定點小數)。因此,可以說,浮點運算器是定點運算器的擴充和強化。一般浮點運算器都至少具有兩個定點數邏輯運算單元,一個用于階碼的比較和運算,另一個用于尾數的運算。從運算器結構來講,不但要有尾數運算器,而且還要有階碼運算器。階碼運算器用來求階差、修改階碼等操作,一般只進行加減運算。而尾數部件不但有加法器用以求和,還應有左移和右移線路,以實現對尾數的操作。

我們設計的浮點運算器以尾數為8 位,階碼為4 位的浮點數為例,根據實驗開發平臺資源,其組成如圖6 所示。

由于XILINX 公司FOUNDATION 3.1 軟件本身提供的器件相當豐富,小到邏輯門,大到全加器,類型豐富,所以我們開

發軟件選用XILINX 公司的FOUNDATION 3.1。在FOUNDATION3.1 原理圖編輯環境中設計出如圖5 所示浮點運算器的

具體原理電路,規定器件的輸入/輸出,并定義好相應的網絡名稱和總線名稱。在整個浮點運算器的設計過程中,核心部

件是加法器、移位寄存器和計數器。

計數器選擇Foundation3.1 的標準庫中CB4CLED(4-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear)。移位寄存器選擇Foundation3.1的標準庫中SR8CLED(8-Bit Shift Register with Clock Enable and Asynchronous Clear)。

計數器開始工作后,根據相應的計數器輸出信號,分別對移位寄存器進行操作。當功能選擇的是加法或減法時,對階的結果是為了移位,在實現過程中,我們假定為浮點數1大于浮點數2,則對浮點數2 的尾數進行右移。當計數器中的階碼差減為0 時,表示右移結束,接下去便是兩浮點數的尾數相加或相減。當功能選擇的是乘法或除法時,計數器的初始值是字長的值,在這里是8。開始計數過程前,乘法累計器被清零。計數開始后,乘法累加器、乘數寄存器和被乘數寄存器分別根據前面所說的定點數相乘所規定的操作進行運作。當計數器計數結束后,乘法結果分別存放于乘法累加器(高8 位)和乘數寄存器中。

當尾數計算和階碼計算都結束后,分別把結果的階碼、尾數和溢出標志送往EDA 實驗臺上的發光二極管。

與其它電路不同,浮點運算器在實現過程中必須注意時序問題。時序仿真是考慮了各個門的時延,設計出相應的邏輯。經過仿真和測試,其方法同VHDL 語言方式,確認相應的邏輯正確無誤后,生成BIT 流文件,經下載板下載到實驗系統上。

結論

在計算機應用、儀器儀表等領域的電子系統設計中,FPGA 技術的含量正以驚人的速度增加。浮點運算器是現代計算機中一個重要組成部分,利用FPGA 技術,能方便靈活地設計出浮點運算器。

電子發燒友App

電子發燒友App

評論