時鐘使能電路是同步設計的重要基本電路,在很多設計中,雖然內部不同模塊的處理速度不同,但是由于這些時鐘是同源的,可以將它們轉化為單一的時鐘電路處理。在FPGA的設計中,分頻時鐘和源時鐘的skew不容易控制,難以保證分頻時鐘和源時鐘同相。故此推薦采用使用時鐘使能的方法,通過使用時鐘使能可以避免時鐘“滿天飛”的情況,進而避免了不必要的亞穩態發生,在降低設計復雜度的同時也提高了設計的可靠性。

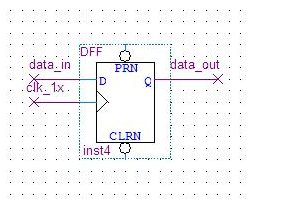

我們可以利用帶有使能端的D觸發器來實現時鐘使能的功能。

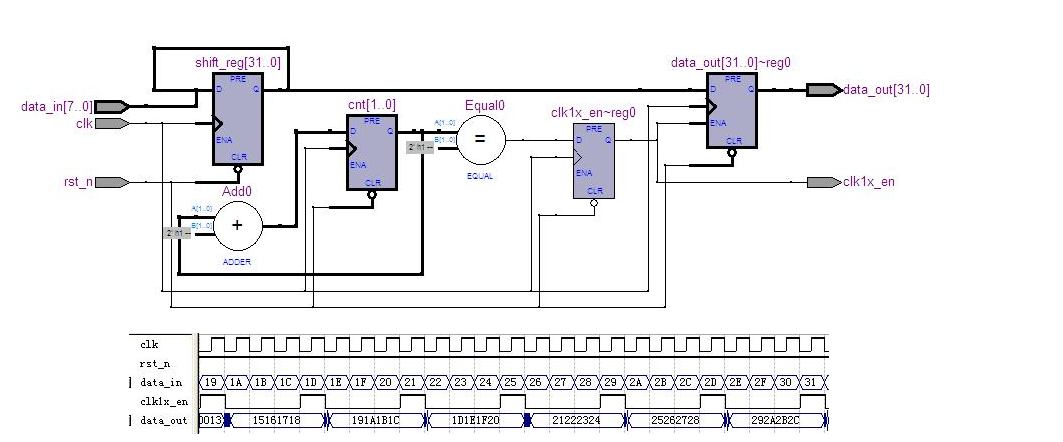

在上圖中clk1x是CLK的四分頻后產生的時鐘,clk1x_en是與clk1x同頻的時鐘使能信號,用clk1x_en作為DFF的使能端,D端的數據只有在clk1x_en有效地時候才能打入D觸發器,從而在不引入新時鐘的前提,完成了下圖電路一致的邏輯功能。

在某系統中,前級數據輸入位寬為8,而后級的數據輸出位寬32,我們需要將8bit的數據轉換成32bit的數據,因此后級處理的時鐘頻率為前級的1/4,若不使用時鐘時能,則就要將前級時鐘進行4分頻來作為后級處理的時鐘,這種設計方法會引入新的時鐘域,為了避免這種情況,我們采用了時鐘時能的方法來減少設計的復雜度。

module gray

(

input clk,

input rst_n,

input [7:0] data_in,

output reg [31:0] data_out,

output reg clk1x_en

);

reg [1:0] cnt;

reg [31:0] shift_reg;

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

cnt <= 2'b0;

else

cnt <= cnt +1'b1;

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

clk1x_en <= 1'b0;

else if(cnt ==2'b01)

clk1x_en <= 1'b1;

else

clk1x_en <= 1'b0;

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

shift_reg <= 32'b0;

else

shift_reg <= {shift_reg[23:0],data_in};

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

data_out<= 32'b0;

else if(clk1x_en==1'b1)//僅在clk1x_en為1時才將shift_reg的值賦給data_out

data_out<=shift_reg;

end

endmodule

編輯:hfy

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636279 -

D觸發器

+關注

關注

3文章

181瀏覽量

49737 -

時鐘電路

+關注

關注

10文章

247瀏覽量

53733

發布評論請先 登錄

相關推薦

熱點推薦

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

IDELAYCTRL 是 Xilinx FPGA(特別是支持高速 I/O 的系列,如 Virtex-5/6/7、Kintex-7、Artix-7、Spartan-6/7 等)中用于管理和校準輸入延遲模塊(IDELAYE2/IDELAYE3)的必須存在的參考時鐘控制模塊。

如何使能cw32f030看門狗復位?

= 0xFFF;

IWDT_Init( IWDT_InitStruct);

IWDT_Cmd();

while(!CW_IWDT->SR_f.RUN);

IWDT_Refresh();

還需要使能時鐘信號

__RCC_IWDT_CLK_ENABLE();

發表于 01-23 07:01

數字IC/FPGA設計中的時序優化方法

在數字IC/FPGA設計的過程中,對PPA的優化是無處不在的,也是芯片設計工程師的使命所在。此節主要將介紹performance性能的優化,如何對時序路徑進行優化,提高工作時鐘頻率。

NVIC中斷使能與禁止使能

ARM?Cortex-M0+ 處理器支持最多 32 個外部中斷源,分別對應中斷使能設置寄存器 NIVC_ISER 的 32 個使能位,和中斷使

發表于 11-13 07:14

時鐘移項電路加速模塊的設計

FPGA引腳中,在基于邏輯的邊沿變化采集時并不能對準數據穩定的時刻,而不能正確采集到數據。為了在時鐘跳變時能對準數據的穩定時刻,通常在設計時可以采用以下方法:專用IP核延遲、鎖相環移相和門電路

發表于 10-29 07:38

PLL技術在FPGA中的動態調頻與展頻功能應用

隨著現代電子系統的不斷發展,時鐘管理成為影響系統性能、穩定性和電磁兼容性(EMI)的關鍵因素之一。在FPGA設計中,PLL因其高精度、靈活性和可編程性而得到廣泛應用,本文將深入探討PLL技術在

Leadway電源模塊的使能信號是如何作用的

在電機控制系統中,Leadway電源模塊的使能信號(Enable Signal)是協調電源啟停與電機驅動的核心控制邏輯之一。其作用不僅限于簡單的通斷控制,更涉及系統安全、能耗管理及多設備協同。

發表于 05-15 09:38

電容在時鐘電路中的應用有哪些

在時鐘電路精密的運行體系中,電容器扮演著不可或缺的角色。從凈化信號到穩定傳輸,從調節頻率到優化電源,電容以其獨特的電氣特性,在不同環節發揮關鍵作用。本文將深入解析電容在時鐘

時鐘電路與晶振電路兩者的區別有哪些

在數字電子系統設計中,時鐘電路與晶振電路是兩個高頻出現的概念。雖然二者緊密相關且常被協同討論,但從功能定位、電路構成到應用場景都存在本質差異

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

Ultrascale是賽靈思開發的支持包含步進功能的增強型FPGA架構,相比7系列的28nm工藝,Ultrascale采用20nm的工藝,主要有2個系列:Kintex和Virtex

FPGA時序約束之設置時鐘組

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析

stm32h7s78 rcc pll2時鐘使能失敗的原因?

調用了 systemclock update 函數,然后對 sdmmc 進行了初始化,看到在使能 sdmmc 時鐘時, pll2 相應的時鐘輸出位沒有被成功置 1,但同樣設置 ltdc

發表于 03-14 10:33

FPGA的設計中的時鐘使能電路

FPGA的設計中的時鐘使能電路

評論