如何實現高速時鐘信號的差分布線

在高速設計中,如何解決信號的完整性問題?差分布線方式是如何實現的?對于只有一個輸出端的時鐘信號線,如何實現差分布線?

2009-04-15 00:26:37 3623

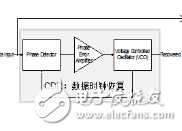

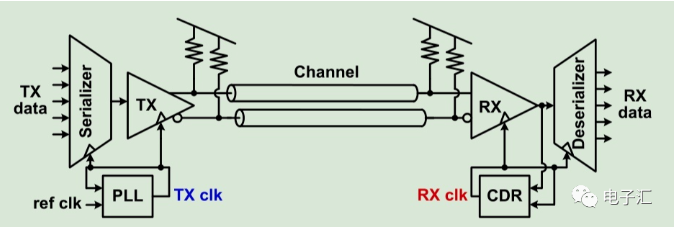

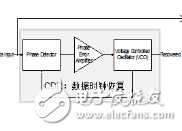

3623 可以通過不同架構實現時鐘恢復,測量設備中最常用的是基于鎖相環(PLL)的方法。根據在數據中看到的跳變,使用恢復電路導出與輸入數據同步的時鐘,這取決于看到數據中的跳變。

2011-01-24 08:55:50 2416

2416

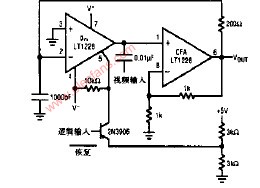

通過使用 OPA615 高帶寬、直流恢復電路,此參考設計可為各種應用提供高帶寬、高精度采樣保持電路。該電路具有整套設計指南支持,可以針對給定應用方便地調整。

2013-11-20 11:26:29 4697

4697

)的時鐘資料恢復電路,從而取得突破性的進展:在具有RS-FEC誤碼校正和使用OM4光纖的條件下,傳輸距離達400米,在沒有RS-FEC條件下則達300米,并已通過多重檢驗測試,再次彰顯昂納在行內領先位置

2017-12-12 11:21:20 7626

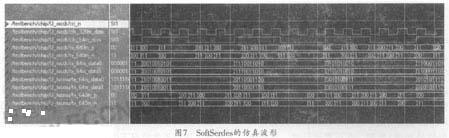

7626 SERDES恢復出的數據進入FPGA有一個解復用和時鐘域轉換的問題,Stratix GX包含了專用電路可以完成8/10bit數據到8/10/20bit數據的Mux/Demux,另外SERDES收端到FPGA內部通用邏輯資源之間還有FIFO可以完成數據接口同步,其電路結構如圖所示。

2018-04-08 08:46:50 10439

10439 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 1443

1443

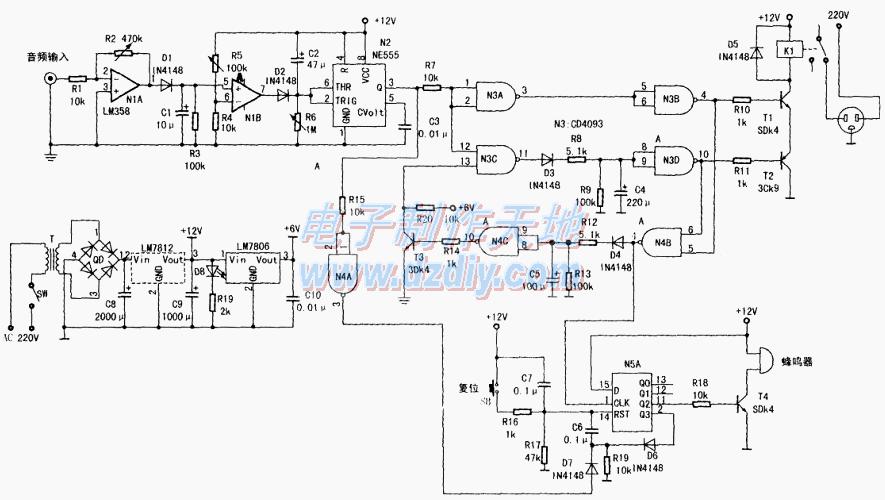

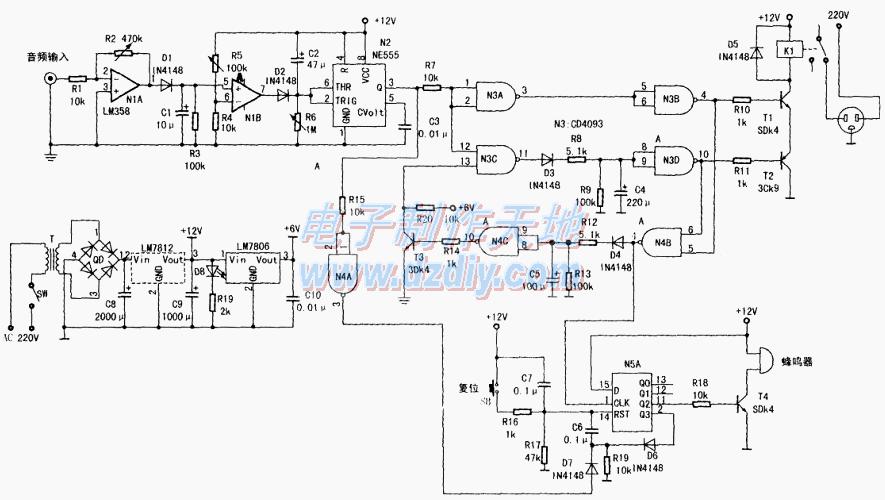

求三次延時芯片我們設計中以前用到的是無限次延時恢復電路,用的NE555的芯片,現在想把無限次延時改為三次延時(只延時恢復三次,第四次就不再恢復),只想換個芯片,不想改動原先的線路,請問大俠能做到嗎?

2009-12-13 09:43:25

靈思All Programmable FPGA 和 SoC 實現高速無線電設計( Enabling High-Speed Radio Designs with Xilinx All

2017-02-10 17:10:32

流水方式對復數數據實現了加窗、FFT、求模平方三種運算。整個設計采用流水與并行方式盡量避免瓶頸的出現,提高系統時鐘頻率,達到高速處理。實驗表明此處理器既有專用ASIC電路的快速性,又有DSP器件的靈活性的特點,適合用于高速數字信號處理。

2012-08-12 11:49:01

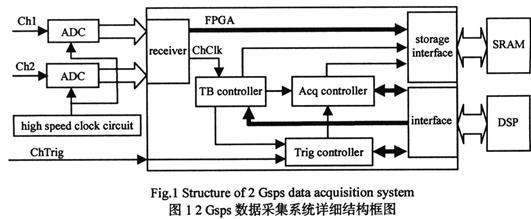

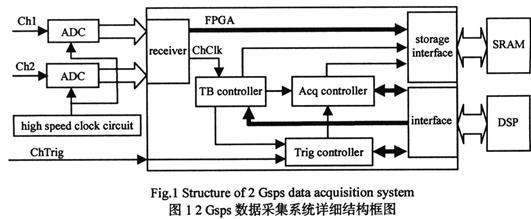

在高速數據采集方面,FPGA有單片機和DSP無法比擬的優勢。FPGA的時鐘頻率高,內部時延小,全部控制邏輯都可由硬件完成,而且速度快,組成形式靈活,并可以集成外圍控制、譯碼和接口電路。更最主要

2019-11-01 07:40:10

恢復電腦出廠設置后丟失的圖片

2024-04-04 22:39:16

高速專用GFP處理器的FPGA實現采用 實現了非標準用戶數據接入 網絡時,進行數據 封裝和解封裝的處理器電路在處理器電路中引入了緩沖區管理器,使得電路能夠有效處理突發到達 瞬時速率較高的客戶數據

2012-08-11 11:51:11

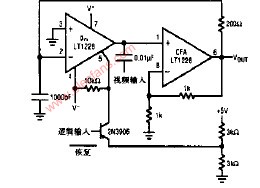

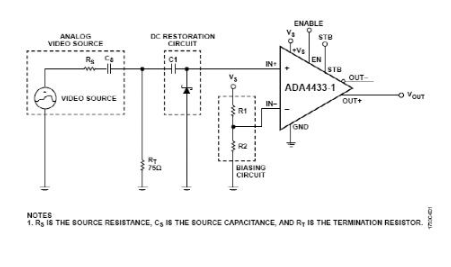

的Board Layout。直流恢復系統使用圖615和圖41恢復兩個系統。圖41實現了作為單位增益放大器的直流恢復功能。從它的名字可以預期,這個直流恢復電路不提供任何放大。在需要放大的應用中,考慮使用圖40

2020-10-20 15:58:35

視頻信號(包括數據與時鐘,其中數據位寬16位,時鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時鐘相對于數據的延時,也就是信號的建立與保持時間在經過FPGA后出現偏移。造成后端的DA不能正確的采集到數據。

2014-02-10 16:08:02

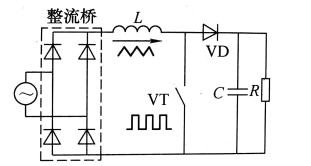

以AC/DC Boost開關電源為例,如圖1所示,主電路中輸人整流橋二極管產生的反向恢復電流的di/dt遠比輸出二極管D反向恢復電流的|di/dt|要小得多。圖2是圖1開關電源中輸人整流橋二極管

2021-06-30 16:37:09

`例說FPGA連載17:時鐘與復位電路設計特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc FPGA的時鐘輸入都有專用引腳,通過這些專用

2016-08-08 17:31:40

文獻說該圖是可變增益主放大器主要由極零相消電路、微分電路、2 級積分放大電路,1 級跟隨放大和基線恢復電路組成,其原理圖如圖

2017-04-06 17:10:08

的電壓輸出信號進一步放大,并維持在一個正確的范圍,以為后續的時鐘恢復和數據裁決電路服務。主放大器要求能處理高速信號,并且具有高增益和較大的動態輸入范圍。 判決器和時鐘恢復電路對信號進行再生。在發送端

2022-04-15 21:01:49

、野外試驗以及生產應用,證明結合FPGA技術,時鐘恢復和系統同步技術在地震勘探儀器中具有獨到的優勢,其精度可達us級,而且穩定,實現方便。地震勘探儀器是一個高度集成的網絡采集系統,在這些地震勘探儀器中

2019-06-18 08:15:35

輸出,或通過FPGA的端口LVDS循環存儲于高速緩存中,再由低速接口輸出。其中,FPGA主要完成對外接口管理、高速緩存的控制和管理。時鐘控制電路對A/D數據轉換器和可編程門陣列FPGA起同步和均衡作用

2018-12-18 10:22:18

目前,在數據采集系統的硬件設計方案中,有采用通用單片機和USB相結合的方案,也有采用DSP和USB相結合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數據采集系統對速度要求;后者雖然可以實現

2019-09-05 07:22:57

AD接口:時鐘對齊、根據幀同步實現串轉并數據對齊.本人非常熟悉Virtex-5/Virtex-6/7 Series FPGA的內置SERDES模塊,包括ISERDES,OSERDES,IODELAY

2014-03-01 18:47:47

描述 通過使用 OPA615 高帶寬、直流恢復電路,此參考設計可為各種應用提供高帶寬、高精度采樣保持電路。該電路具有整套設計指南支持,可以針對給定應用方便地調整。

2019-07-23 08:15:29

基線恢復電路經過電容c32后脈沖信號消失,我模擬的經過電容后信號無太大變化

2017-08-03 11:58:01

基線恢復電路后原本放大5倍的信號,又減小到了放大之前。本來應該是信號幅度相差不多的

2017-11-30 19:39:35

高速連續數據采集系統的背景及功能是什么?如何利用FPGA實現高速連續數據采集系統設計?FPGA在高速連續數據采集系統中的應用有哪些?

2021-04-08 06:19:37

本文利用時鐘切換的方法,在低端AlteraEP2C5T144C6上實現了204.8MHZ的時鐘數據恢復電路,并通過了硬件驗證。

2021-04-30 07:00:16

的射頻標簽由于工作距離遠,天線尺寸小等優點越來越受到重視。射頻標簽芯片的射頻接口模塊包括電源恢復電路、穩壓電路和解調整形電路。射頻接口的設計直接影響到射頻標簽的關鍵性能指標。本文對射頻標簽能量供應原理進行了詳細的理論分析,并完成了電源恢復電路、穩壓電路和解調整形電路的設計。

2019-07-26 06:33:08

本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數傳系統中得到應用。

2021-04-29 06:04:42

的解調電路很復雜,本系統為了使解調電路簡單化,采取基帶信號速率與擴頻碼元周期同步同速的特殊措施,省去了解調電路中復雜的載波恢復電路。1 本擴頻系統的調頻解調原理本系統的載波,PN碼和基帶信號的速率

2019-08-07 06:41:58

:PRBS或自定義等格式),信號調理前端(輸出電平控制等),時鐘信號前端(輸出時鐘電平控制等)。2)誤碼接收機:包括:時鐘恢復電路(有的BERT沒有CDR),碼型判決電路(從信號中判斷出碼型數據),錯誤碼

2019-07-01 06:06:01

試題,學員可通過高壓電工模擬考試題庫全真模擬,進行高壓電工自測。1、【單選題】 配電裝置中,電氣設備的網狀遮欄高度不低于()m,底部離地不應超過0.1m。(B)A、1.3B、1.7C、1.52、【單選題】 電路中負荷為()時,觸頭間恢復電壓等于電源電壓,有利于電弧熄滅。(C...

2021-09-02 06:52:27

本文介紹了負偏壓溫度不穩定性的恢復電路和恢復方法。

2021-05-07 06:32:09

的控制核心。但利用中低端FPGA還沒有可以達到100MHz以上的時鐘數據恢復電路。由于上面的原因,許多利用FPGA實現的高速通信系統中必須使用額外的專用時鐘數據恢復IC,這樣不僅增加了成本,而且裸露

2009-10-24 08:38:08

采用一種新的時鐘增強方案并配合雙區折射率耦合激光器實現非歸零碼信號的全光時鐘恢復,通過數學仿真研究了此時鐘恢復系統在64 Gb/s非歸零碼系統中的性能表現。仿真結果表

2009-03-04 10:38:27 19

19 SY87700L是MICREL公司推出的一種完整的、可將數據速率從32-175Mbps的NRZ數據流中進行恢復的反相不歸零時鐘恢復和數據重定時電路芯片,可廣泛應用于SONET/SDH/ATM、高速英特網和其它所

2009-04-25 15:51:45 28

28 精密參考時鐘在時鐘與數據恢復電路中的應用

2009-05-04 13:36:44 35

35 采用IL2E2 TDI CCD 做為傳感器,與計算機構成了成像系統,并在計算機CRT 上顯示出圖像。主要介紹高速CCD 相機的工作時鐘產生電路的設計,采用大規模集成電路FPGA 實現了該工作時鐘驅動

2009-07-04 16:02:55 44

44 本文介紹了一種應用FPGA 器件完成高速數字傳輸的方法,利用這種方法實現無線收發芯片nRF2401A 的高速數據接口。為進一步提高信息的傳輸速率,這里還對待傳輸的數據進行了壓縮處

2009-08-04 09:16:20 9

9 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 本文設計了一種以 FPGA 為數據壓縮和數據緩存單元的高速數據采集系統,其主要特點是對高速采集的數據進行實時壓縮,再將壓縮后的數據進行緩沖存儲。該設計利用數據比較模

2009-11-30 15:32:36 20

20 10Gbps XFP光模塊系統數字診斷功能需要進行信號丟失(LOS)監控。通過監控光功率是否過低,可探測到導致誤碼率劣化的系統故障。MAX3991限幅放大器IC時鐘和數據恢復電路針對XFP模塊

2009-12-09 16:26:29 22

22 10Gb/s時鐘數據恢復電路行為級模型研究:研究了超高速(10Gb/s) NRZ 碼時鐘數據恢復電路的行為級建模,并采用TSMC 0.18μm CMOS 工藝進行了電路級仿真。關鍵詞: 時鐘數據恢復;鎖

2009-12-14 09:25:19 18

18 摘要:通過鎖定檢測器控制,初期極性相位判決算法對載波進行頻率上的快速鎖定,隨后帶加權的DD算法減少頻率抖動并最終實現相位恢復。通過Matlab仿真驗證,對于64QAM電路在5000個

2010-05-13 09:06:25 19

19 隨著技術的發展, 往往需要在不同的系統之間實現高速通信, 現介紹了一種基于LVDS的高速數據傳輸的接口LinkPort , 給出了在Xilinx 的FPGA 中實現該接口的原理以及關鍵設計, 并成功

2010-09-22 08:26:14 98

98 應用于鎖相環的脈寬調整電路的設計

前言

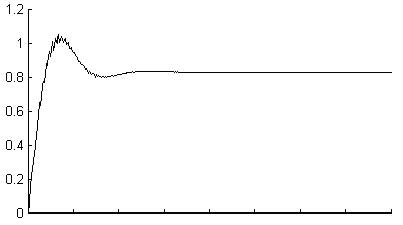

在鎖相環PLL、DLL和時鐘數據恢復電路CDR等電路的應用中,人們普遍要求輸出時鐘信號有50%的占空比,以便在時鐘上升及下

2008-10-16 08:59:42 1504

1504

Applications for clock data recovery (CDR) abound in telecommunications, optical transceivers, data and storage area networks, and wireless products. The benefits of CDR technology are increasingly important as designs require much greater

2009-04-22 10:25:00 1371

1371

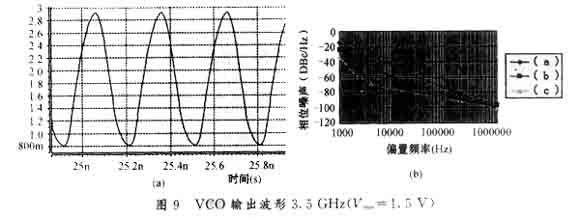

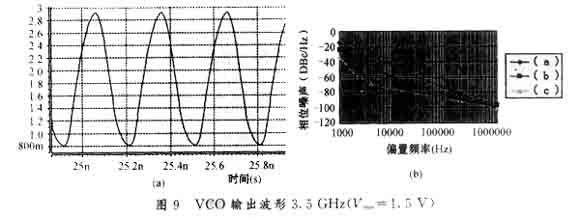

壓控振蕩器已經成為當今時鐘恢復電路和頻率合成電路中不可缺少的組成部分。本文分別從壓控振蕩器的振蕩頻率和相位噪聲兩個角度,詳細闡述影響VCO性能的因素,并提出相應

2009-05-09 12:29:42 3061

3061

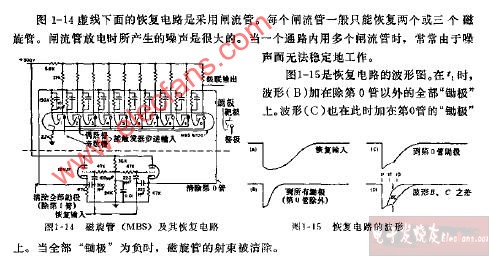

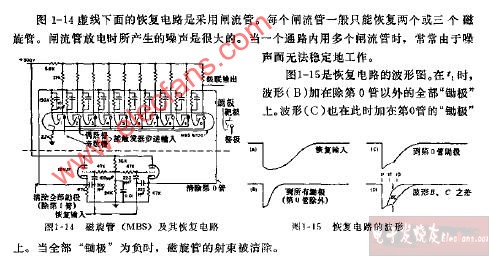

恢復電路的波形電路圖

2009-06-20 11:09:55 599

599

高頻有增益的直流恢復電路圖

2009-06-23 11:46:47 562

562

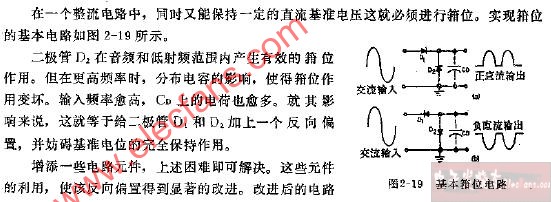

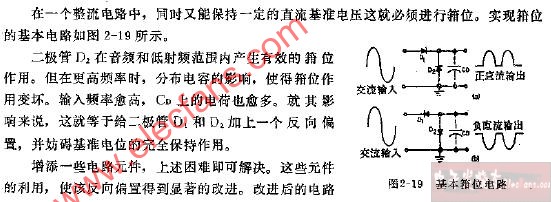

圖像信號的直流恢復電路

本電路在每次水平掃描開始時都講黑白組

2009-10-10 15:45:18 1272

1272

大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 827

827

基于FPGA的SoftSerdes設計與實現

0 引言

在高速源同步應用中,時鐘數據恢復是基本的方法。最普遍的時鐘恢復方法是利用數字時鐘模塊(DCM)

2009-12-28 09:23:40 1175

1175

FPGA芯片在高速數據采集緩存系統中的應用

概 述在高速數據采集方面,FPGA有單片機和DSP無法比擬的優勢。FPGA的時鐘頻率高,內部時延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 1179

1179

FPGA設計的高速FIFO電路技術

本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量

2010-05-27 09:58:59 2978

2978

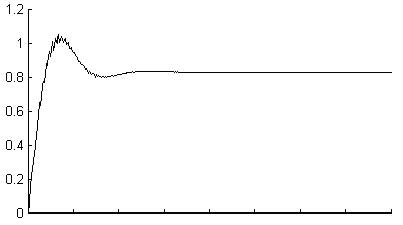

為利用簡單的線纜收發器,實現中等數據率的串行數據傳輸,提出了一種基于電荷泵式PLL的時鐘數據恢復的方法。鑒相器由FPGA實現,用固定延時單元構成一條等間隔的延時鏈,將輸入信號經過每級延時單元后的多個輸出用本地的VCO時鐘鎖存,輸入信號的沿變在延時鏈

2011-03-15 12:39:34 90

90 本內容提供了反相恢復電路

2011-05-19 17:18:55 49

49 在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 184

184 MAX14972雙超高速USB 3.0均衡器/轉接驅動器采用可編程輸入均衡和輸出去加重,以減少決定性抖動和恢復電路板或信號電纜損耗所造成的信號損失

2012-04-26 11:38:00 2001

2001

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1591

1591

一種5Gb_s雙信道并行時鐘數據恢復電路_李志貞

2017-01-08 10:18:57 0

0 6_25Gb_s快速鎖定時鐘數據恢復電路_鐘威

2017-01-08 10:24:07 0

0 DSP與FPGA高速的數據傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現場可編程邏輯門陣列) 設計 FIFO的接口電路,即可實現高速互聯。

2017-02-11 14:16:10 2950

2950

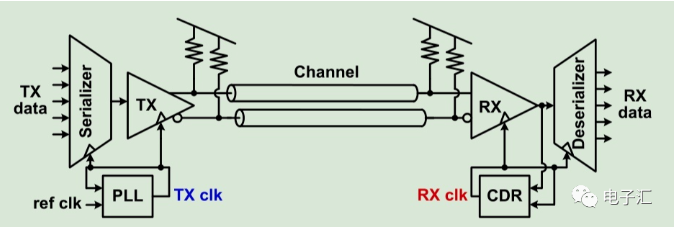

對于高速的串行總線來說,一般情況下都是通過數據編碼把時鐘信息嵌入到傳輸的數據流里,然后在接收端通過時鐘恢復把時鐘信息提取出來,并用這個恢復出來的時鐘對數據進行采樣,因此時鐘恢復電路對于高速串行信號

2017-11-16 01:01:29 22840

22840

介紹一種采用FPGA(現場可編程門陣列電路)實現SDH(同步數字體系)設備時鐘芯片設計技術,硬件主要由1 個FPGA 和1 個高精度溫補時鐘組成.通過該技術,可以在FPGA 中實現需要專用芯片才能實現的時鐘芯片各種功能,而且輸入時鐘數量對比專用芯片更加靈活,實現該功能的成本降低三分之一.

2017-11-21 09:59:00 2653

2653

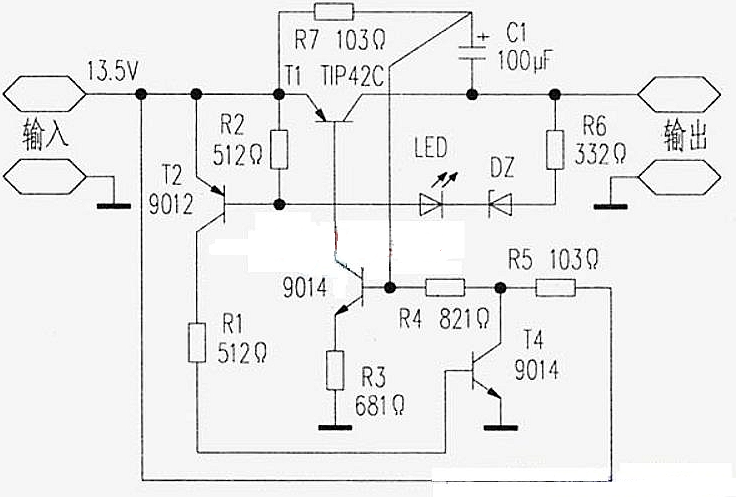

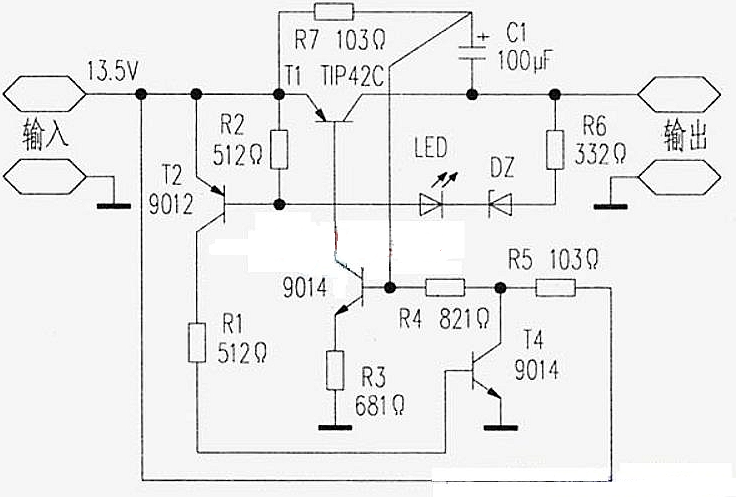

本文主要介紹了過流保護自恢復電路圖大全(六款模擬電路設計原理圖詳解)。具有自恢復功能的過流保護電路這款無電流取樣的過流保護電路具有短路點撤除后能自動恢復輸出的特點,保護時較工作時電流要小得多,即使長時間短路,也不會損壞電源。

2018-02-01 14:58:10 154860

154860

本文設計了一種新穎的單片集成、適用于高速串行通信接口接收端和數據恢復電路的等間距高精度五相時鐘發生電路.基于負反饋動態調整原理和數字化的模擬電路設計技術,電路采用TSMC( Taiwan

2018-03-15 16:44:13 8

8 文中基于2.5 GB/s的高速型數據收發器模型,采用SMIC 0.18 um雙半速率CMOS時鐘進行數據的恢復處理。設計CMOS時鐘主要包含:提供數據恢復所需等相位間隔參考時鐘的1.25 GHz

2018-04-09 11:04:02 2

2 電子發燒友網為你提供TI(ti)opa615相關產品參數、數據手冊,更有opa615的引腳圖、接線圖、封裝手冊、中文資料、英文資料,opa615真值表,opa615管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-08-17 15:44:46

本文采用ADC+高頻時鐘電路+FPGA+DSP的結構模式,設計了一種實時采樣率為2 Gsps的數字存儲示波器數據采集系統,為國內高速高分辨率的數據采集系統的研制提供了一個參考方案。

2019-05-03 09:19:00 7263

7263

該電路采取先切斷接收機供電電源再通電的方法,使衛星接收機自動恢復正常工作,整個處理過程不需要人工干預。

2018-09-27 14:54:00 3980

3980

介紹了一種用FPGA實現對高速A/D轉換芯片的控制電路,討論了這一控制電路設計思想,提出了更好地解決高速A/D采樣與較慢速的單片機數據處理間矛盾的鏈接方法。

2018-09-21 17:00:29 27

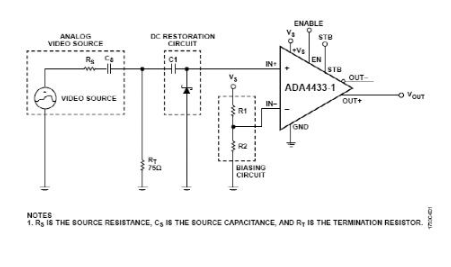

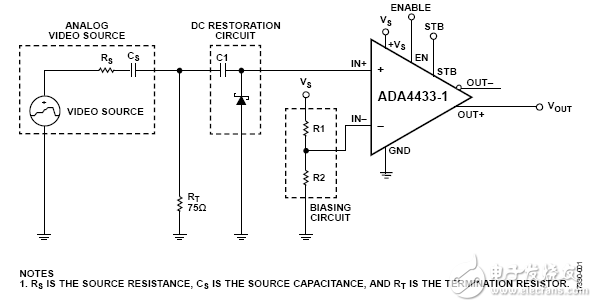

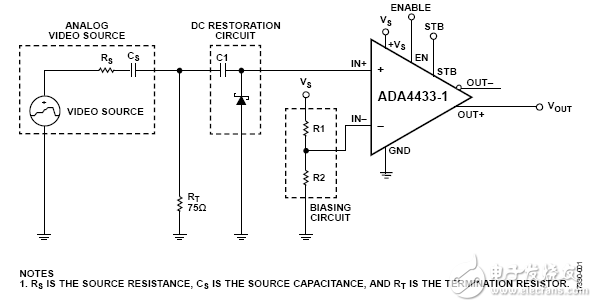

27 本應用筆記說明恢復復合視頻信號的正確直流電平的方法。

2019-08-21 11:45:58 2240

2240

驅動電路是典型的交流耦合信號,以對器件提供隔直處理。視頻信號的直流電平代表黑色的顯示等級,該電平必須恒定才能適應視頻處理電路。 本應用筆記說明恢復復合視頻信號的正確直流電平的方法。 圖 1. 使用 ADA4433-1 的直流恢復電路原理圖 復合視頻信號說明 復合視頻信號也

2019-08-22 12:53:31 3937

3937

介紹了一種基于四相關器結構的2.5gb/s 15 mW時鐘恢復電路的設計。該電路采用鑒相和鑒頻相結合的方法,將微分、全波整流、混頻等高速運算結合在一起,降低了功耗。此外,采用兩級壓控振蕩器,該振蕩器

2020-06-29 08:00:00 1

1 由于工作距離遠,天線尺寸小等優點越來越受到重視。射頻標簽芯片的射頻接口模塊包括電源恢復電路、穩壓電路和解調整形電路。射頻接口的設計直接影響到射頻標簽的關鍵性能指標。本文對射頻標簽能量供應原理進行了詳細的理論分析,并完成了電源恢復電路、穩壓電路和

2020-07-28 18:54:00 0

0 將寬禁帶半導體器件SiC肖特基二極管引入到直流開關電源的PFC電路中,可以在不改變電路拓撲和工作方式的情況下,有效解決硅二極管反向恢復電流給電路帶來的許多問題,極大地改善電路的工作品質。

2020-10-02 16:11:00 10337

10337

無源 UHF RFID 芯片的設計難點是圍繞著如何提高芯片的讀寫距離、降低標簽的制造成本展開的。因此,提高電源恢復電路 的效率,降低整體芯片的功耗,并且工作可靠仍然是 RFID 標簽芯片設計主要的挑戰。

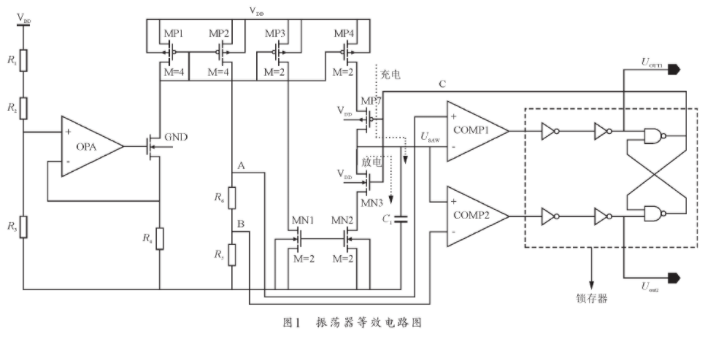

2020-12-29 18:47:29 25

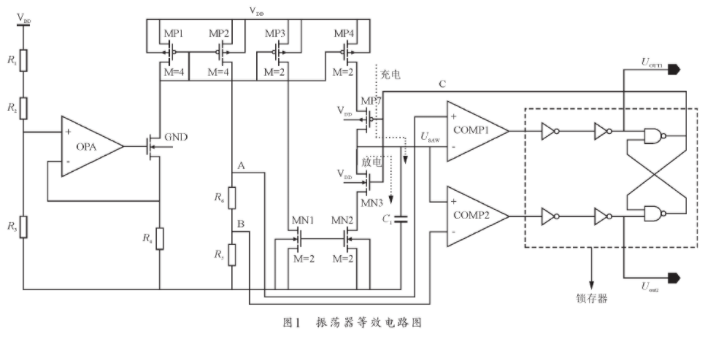

25 振蕩器作為現代電子系統的重要組成部分,被廣泛應用于時鐘同步電路、無線通信收發器中的頻率綜合器、光通信中的時鐘恢復電路(CRC,clock recovery circuit),以及多相位采樣電路中。振蕩器按實現電路元件分為RC振蕩器、LC振蕩器和石英晶體振蕩器。

2020-12-07 08:46:00 2139

2139

介紹一種基于Actel公司Fusion StartKit FPGA的線陣CCD圖像數據采集系統。以FPGA作為圖像數據的控制和處理核心,通過采用高速A/D、異步FIFO、UART以及電平轉換、放大

2021-02-02 17:12:32 8

8 EDA技術使得電子線路的設計人員能在計算機上完成電路的功能設計、邏輯設計、時序測試直至印刷電路板的自動設計。本文介紹了以 VHDL 語言和硬件電路為表達方式,以 Quartus II 軟件為設計工具,最終通過 FPGA 器件實現數字時鐘的設計過程。

2021-05-25 16:28:10 40

40 對于高速的串行總線來說,一般情況下都是通過數據編碼把時鐘信息嵌入到傳輸的數據流里,然后在接收端通過時鐘恢復把時鐘信息提取出來,并用這個恢復出來的時鐘對數據進行采樣,因此時鐘恢復電路對于高速串行信號的傳輸和接收至關重要。

2022-02-09 10:43:43 6

6 對于高速的串行總線來說,一般情況下都是通過數據編碼把時鐘信息嵌入到傳輸的數據流里,然后在接收端通過時鐘恢復把時鐘信息提取出來,并用這個恢復出來的時鐘對數據進行采樣,因此時鐘恢復電路對于高速串行信號

2022-02-11 15:05:26 17

17 本文討論從GSM到OC-192及更高版本的高速串行通信的時鐘數據恢復(CRD)。它解釋了如何通過典型鏈接轉換和重新捕獲數據。本文還研究了不同的CDR方案以及參考振蕩器在通信鏈路發射端和接收端的作用。

2023-06-10 14:49:44 2453

2453

Xilinx公司的許多FPGA已經內置了一個或多個MGT(Multi-Gigabit Transceiver)收發器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收發器內部包括高速串并轉換電路、時鐘數據恢復電路、數據編解碼電路、時鐘糾正和通道綁定電路

2023-07-29 16:47:04 1734

1734

時,由于時鐘頻率不同,所以可能會產生元件的不穩定情況,導致傳輸數據的錯誤。此時我們需要采取一些特殊的措施,來保證跨時鐘域傳輸的正確性。 FPGA跨時鐘域通信的基本實現方法是通過FPGA內部專門的邏輯元件進行數據傳輸。發送方用一個邏輯電路

2023-10-18 15:23:51 1901

1901 器件損壞。為了保護二極管不受反向擊穿的影響,可以使用二極管反向恢復電路。 二極管反向恢復電路是一種用于減小反向恢復電流的電路,通常由二極管和電感器構成。當二極管處于正向導通狀態時,電感器存儲了能量;當二極管從導

2023-12-18 11:23:57 4138

4138 FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在當今高速發展的通信技術中,時鐘恢復已成為實現高速串行數據傳輸的關鍵。這項技術廣泛應用于以太網、PCI Express、Aurora等通信協議中,成為這些系統達到高帶寬傳輸不可或缺的一部分。本文將

2024-09-10 10:38:43 2587

2587

電子發燒友網站提供《信號和時鐘恢復比較器電路.pdf》資料免費下載

2024-09-23 12:16:33 0

0

電子發燒友App

電子發燒友App

評論