引言:晶振是數(shù)字電路設(shè)計(jì)中非常重要的器件,時(shí)鐘的相位噪聲、頻率穩(wěn)定性等特性對(duì)產(chǎn)品性能影響很大。本文基于可編程晶振SI570,就Xilinx FPGA收發(fā)器輸入?yún)⒖紩r(shí)鐘的硬件設(shè)計(jì)及FPGA軟件設(shè)計(jì)給出設(shè)計(jì)案例,供大家參考。通過(guò)本文,可以了解到:

Xilinx FPGA收發(fā)器參考時(shí)鐘設(shè)計(jì)要點(diǎn)

可編程晶振SI570設(shè)計(jì)方法

1.Xilinx FPGA收發(fā)器參考時(shí)鐘設(shè)計(jì)要求

1.1參考時(shí)鐘接口要求

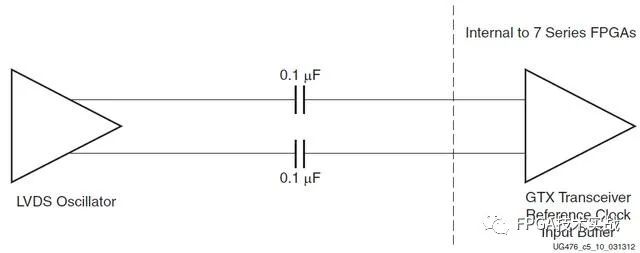

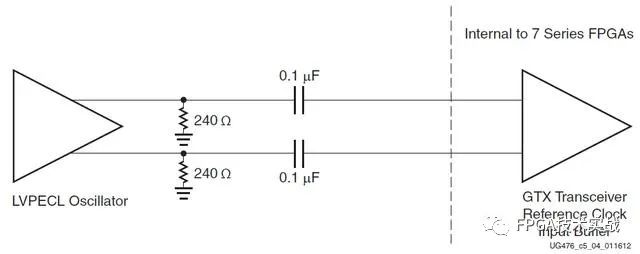

FPGA收發(fā)器GTX/GTH參考時(shí)鐘接口提供兩種連接方式:LVDS(如圖1所示)和LVPECL(如圖2所示)。我們?cè)谶x擇晶振時(shí),至少要支持其中一種接口輸出電平標(biāo)準(zhǔn)。圖2所示的電阻值為一般推薦值,實(shí)際偏置電阻值需要參考晶振手冊(cè)。圖1和圖2中交流AC耦合電容作用:1)阻斷外部晶振和GTX/GTH收發(fā)器Quad專用時(shí)鐘輸入管腳之間的DC電流,降低功耗;2)AC耦合電容和參考時(shí)鐘輸入端接構(gòu)成高通濾波器,衰減參考時(shí)鐘偏移;3)保持耦合電容兩側(cè)共模電壓獨(dú)立,互不干擾。

圖1、LVDS晶振和7系列FPGA收發(fā)器參考時(shí)鐘輸入接口

圖2、LVPECL晶振和7系列FPGA收發(fā)器參考時(shí)鐘輸入接口

1.2參考時(shí)鐘電氣特性要求

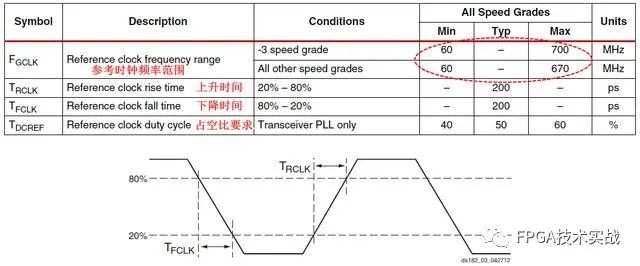

FPGA收發(fā)器參考時(shí)鐘開(kāi)關(guān)特性和DC特性要求分別如圖3和圖4所示。

圖3、FPGA收發(fā)器參考時(shí)鐘開(kāi)關(guān)特性要求

圖4、FPGA收發(fā)器參考時(shí)鐘DC特性要求

2.硬件電路設(shè)計(jì)

2.1晶振選型

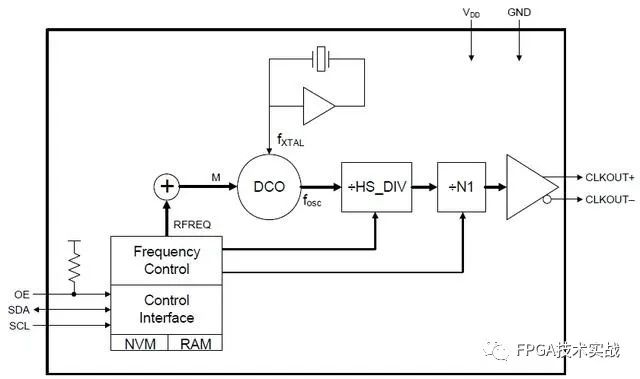

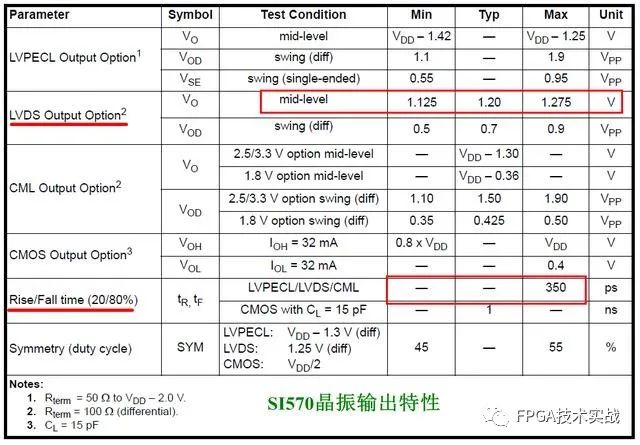

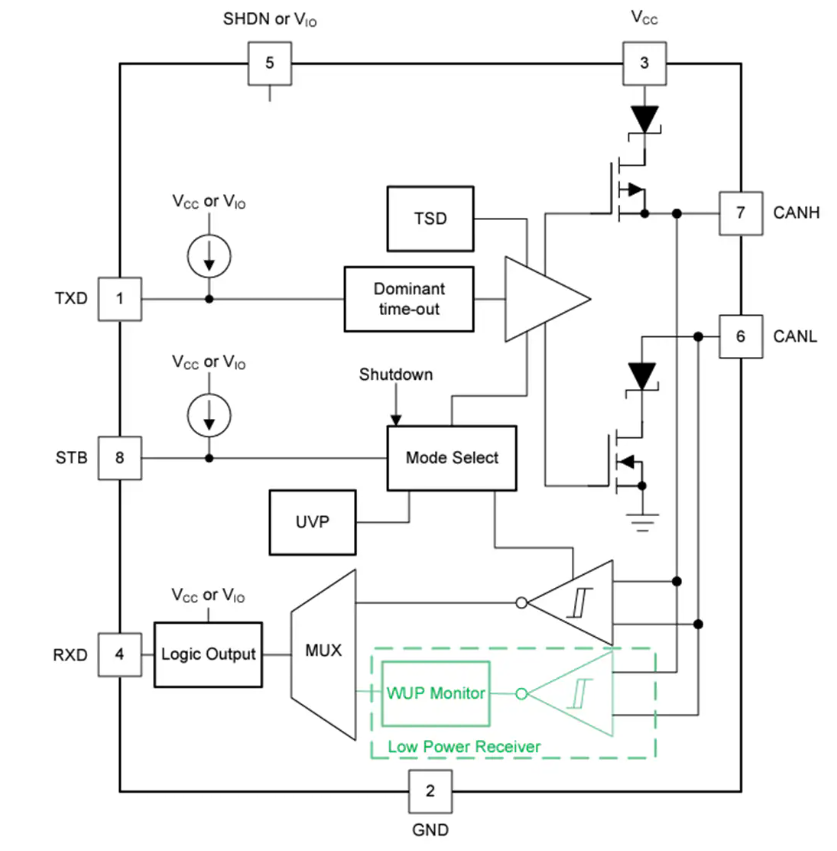

按照章節(jié)1中FPGA收發(fā)器參考時(shí)鐘要求,我們選擇Silicon labs公司的si570系列可編程晶振,該晶振典型應(yīng)用SONET/SDH、10G以太網(wǎng)通信、時(shí)鐘恢復(fù)等場(chǎng)合。該晶振輸出特性如圖6所示。

圖5、SI570晶振內(nèi)部功能框圖

圖6、SI570晶振輸出特性

2.2原理圖設(shè)計(jì)

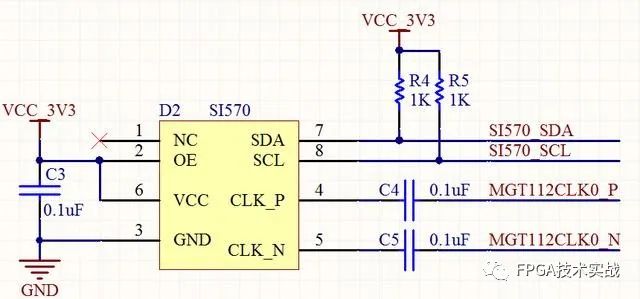

FPGA收發(fā)器參考時(shí)鐘晶振SI570原理圖設(shè)計(jì)如圖7所示。

圖7、SI570原理圖設(shè)計(jì)

3.SI570 FPGA軟件配置及結(jié)果測(cè)試

3.1 SI570晶振配置方法

從圖5中,可看到SI570控制接口采用I2C接口。我們?cè)谂渲迷摼д駮r(shí)要按照以下操作步驟進(jìn)行:

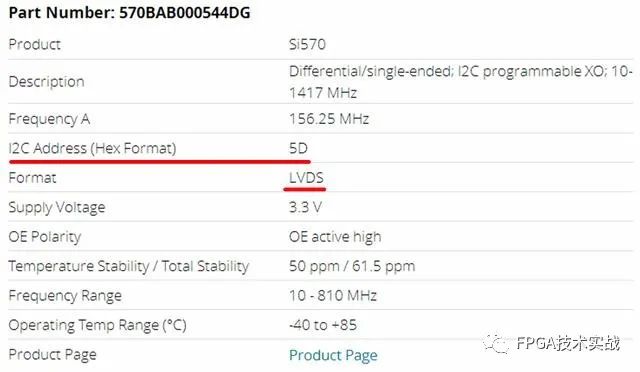

1.SI570根據(jù)家族類別,器件地址都不同,故首先需要去Silicon官網(wǎng)查找項(xiàng)目選型的晶振型號(hào)對(duì)應(yīng)的器件地址。舉例SI570晶振型號(hào):570BAB000544DG,該型號(hào)參數(shù)如圖8所示。在該圖中,我們可以得到可編程晶振的重要參數(shù),如器件的I2C地址(0x5D),出廠默認(rèn)輸出頻率(156.25MHz),頻率范圍等等。

圖8、SI570出廠參數(shù)信息

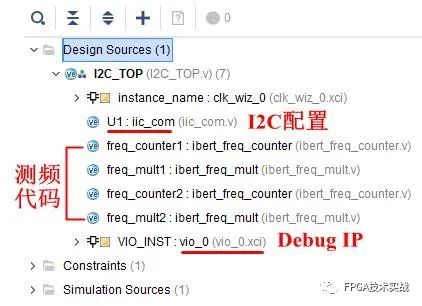

2.編寫FPGA軟件,讀出晶振SI570內(nèi)部出廠默認(rèn)寄存器配置字。FPGA實(shí)例工程如圖9所示。

圖9、SI570測(cè)試?yán)坦こ?/p>

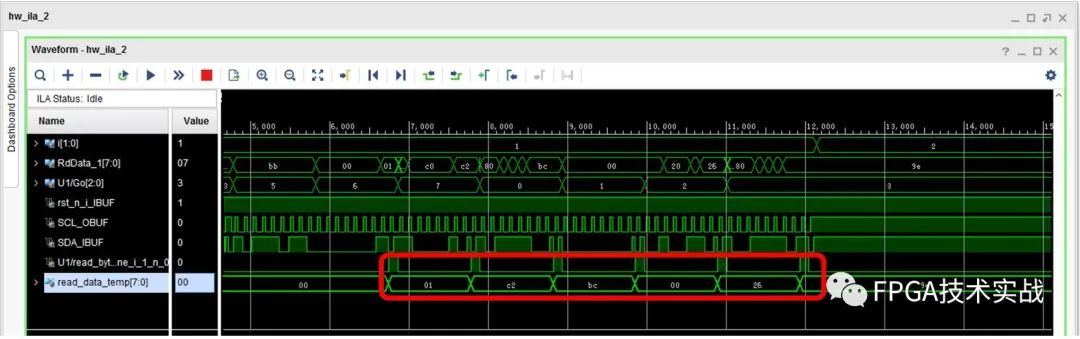

3.根據(jù)讀出的SI570內(nèi)部寄存器默認(rèn)配置值,F(xiàn)PGA I2C總線讀時(shí)序圖如圖10所示。

圖10、FPGA I2C總線讀時(shí)序圖

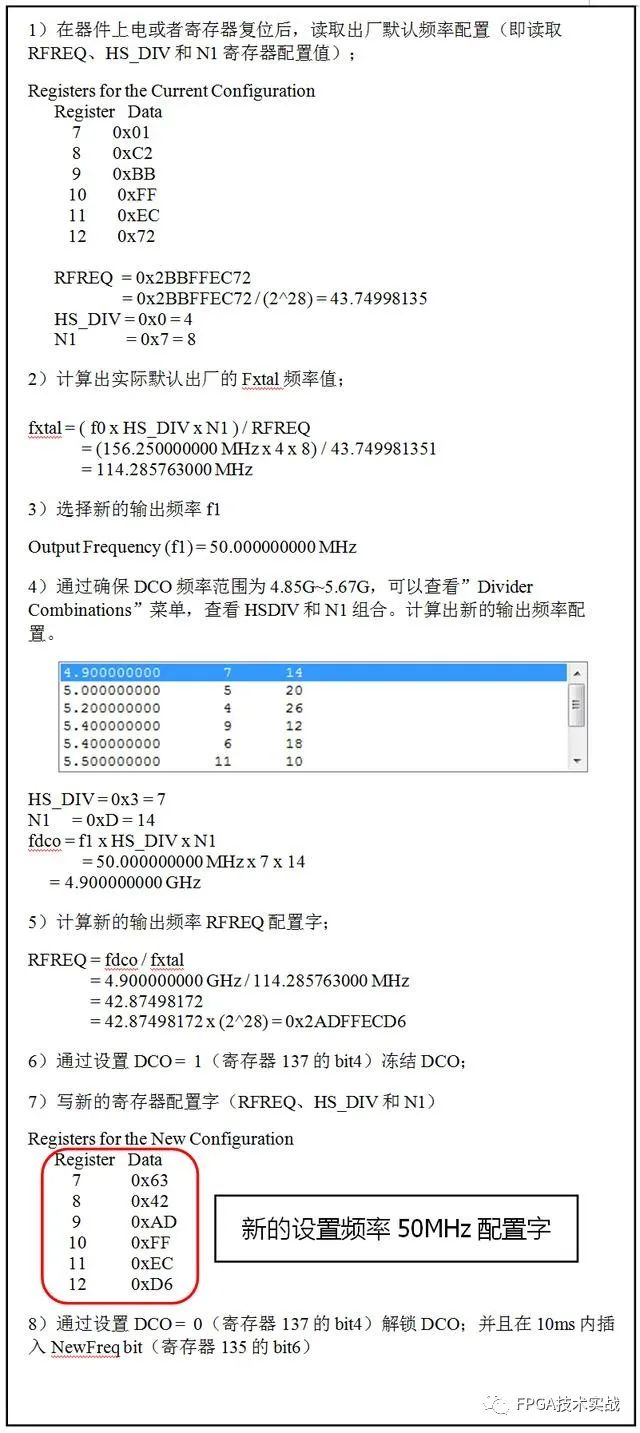

4.利用Silicon官方Programmable Oscillator Calculator軟件計(jì)算出要求出頻率所需的配置寄存器值。如圖11所示,本設(shè)計(jì)將SI570輸出頻率設(shè)置為50MHz。

圖11、計(jì)算SI570配置寄存器流程步驟

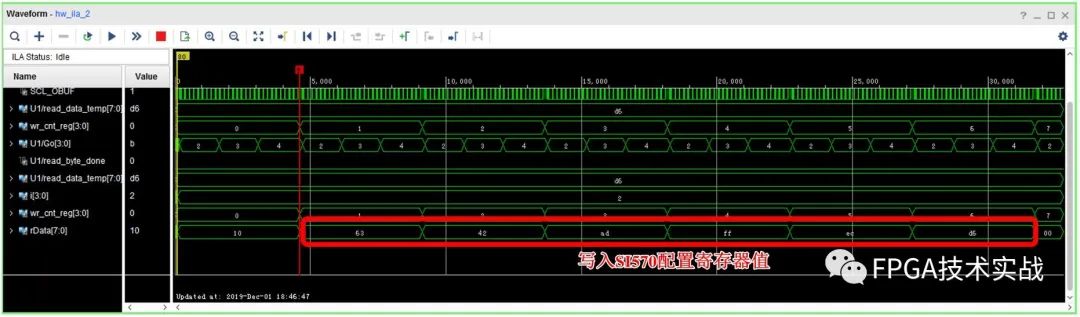

5.寫SI570寄存器配置值。FPGA I2C總線寫時(shí)序圖如圖12所示。

圖12、FPGA I2C總線寫時(shí)序圖

3.2 SI570配置結(jié)果測(cè)試

在圖5SI570測(cè)試?yán)坦こ讨校覀冞€加入了SI570輸出頻率測(cè)試代碼,以通過(guò)FPGA在線邏輯分析儀測(cè)試SI570輸出頻率是否達(dá)到50MHz設(shè)計(jì)輸出要求。測(cè)試結(jié)果如圖13所示,可以看到晶振輸出結(jié)果符合設(shè)計(jì)要求。

圖13、SI570輸出頻率測(cè)試結(jié)果

編輯:lyn

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3819瀏覽量

111201 -

晶振

+關(guān)注

關(guān)注

35文章

3564瀏覽量

73446 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1651瀏覽量

83344 -

Xilinx FPGA

+關(guān)注

關(guān)注

1文章

29瀏覽量

7387

原文標(biāo)題:Xilinx FPGA收發(fā)器參考時(shí)鐘設(shè)計(jì)應(yīng)用

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx FPGA中IDELAYCTRL參考時(shí)鐘控制模塊的使用

SN74ABT18652:18位收發(fā)器與寄存器掃描測(cè)試設(shè)備的深度解析

探索DS92CK16:3V BLVDS 1到6時(shí)鐘緩沖/總線收發(fā)器的卓越性能與應(yīng)用

IBERT GT收發(fā)器誤碼率測(cè)試實(shí)例

TCAN341x系列3.3V CAN FD收發(fā)器技術(shù)解析與應(yīng)用指南

一文詳解xilinx 7系列FPGA配置技巧

華普微Sub-GHz無(wú)線收發(fā)單片機(jī)CMT2391F128#單片機(jī) #電路原理 #Sub-GHz #射頻收發(fā)器

谷泰微GT74LVCXTX45系列雙電源總線收發(fā)器產(chǎn)品介紹

CAN收發(fā)器:總線信號(hào)的“翻譯官”

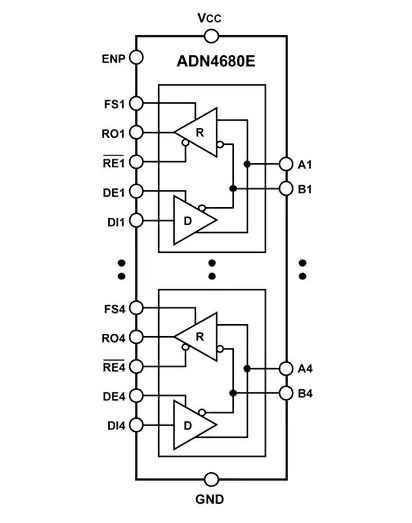

Analog Devices Inc. ADN4680E四通道M-LVDS收發(fā)器數(shù)據(jù)手冊(cè)

如何自動(dòng)測(cè)量CAN收發(fā)器的延遲時(shí)間?

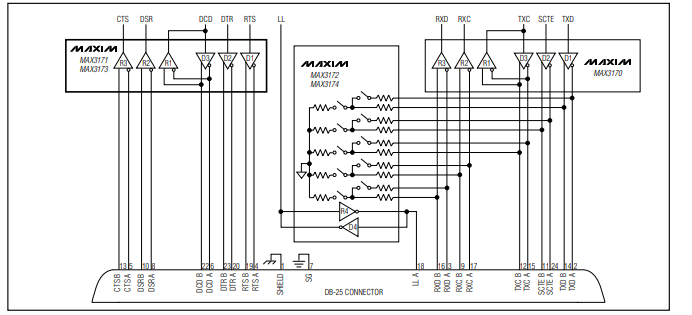

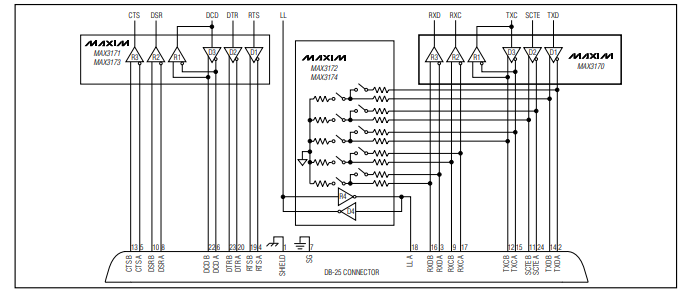

MAX3171/MAX3173 +3.3V、多協(xié)議、3Tx/3Rx、軟件可選的控制收發(fā)器技術(shù)手冊(cè)

MAX3170 +3.3V、多協(xié)議、3 Tx/3 Rx、軟件可選的時(shí)鐘/數(shù)據(jù)收發(fā)器技術(shù)手冊(cè)

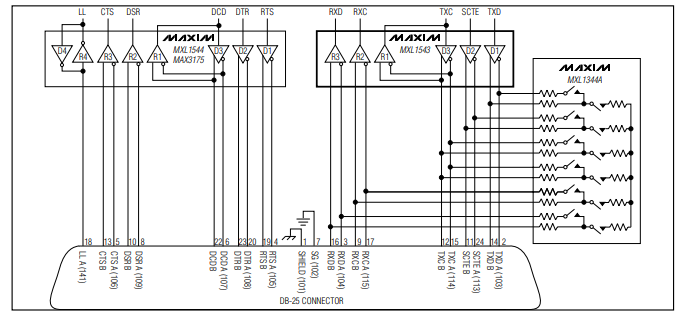

MXL1543 +5V、多協(xié)議、3Tx/3Rx、軟件可選的時(shí)鐘/數(shù)據(jù)收發(fā)器技術(shù)手冊(cè)

芯力特SIT1462Q CAN FD收發(fā)器簡(jiǎn)介

Xilinx FPGA收發(fā)器參考時(shí)鐘設(shè)計(jì)要求與軟件配置及結(jié)果測(cè)試

Xilinx FPGA收發(fā)器參考時(shí)鐘設(shè)計(jì)要求與軟件配置及結(jié)果測(cè)試

評(píng)論