聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

561文章

8244瀏覽量

366656 -

FPGA

+關注

關注

1660文章

22412瀏覽量

636344 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133435

發布評論請先 登錄

相關推薦

熱點推薦

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

IDELAYCTRL 是 Xilinx FPGA(特別是支持高速 I/O 的系列,如 Virtex-5/6/7、Kintex-7、Artix

【VPX610】基于6U VPX總線架構的高性能實時信號處理平臺

板卡概述VPX610是一款基于6UVPX架構的高性能實時信號處理平臺,該平臺采用2片TI的KeyStone系列多核DSPTMS320C6678作為主處理單元,采用1片Xilinx的Virtex-7

FPGA DSP模塊使用中的十大關鍵陷阱

FPGA 芯片中DSP(數字信號處理)硬核是高性能計算的核心資源,但使用不當會引入隱蔽性極強的“坑”。這些坑不僅影響性能和精度,甚至會導致功能錯誤。以下是總結了十大關鍵陷阱及其解決方案,分為

基于DSP與FPGA異構架構的高性能伺服控制系統設計

DSP+FPGA架構在伺服控制模塊中的應用,成功解決了高性能伺服系統對實時性、精度和復雜度的多重需求。通過合理的功能劃分,DSP專注于復雜算法和上層控制,FPGA處理高速硬件任務,兩者

Altera Agilex 5系列FPGA與SoC產品榮膺2025全球電子成就獎

近日,全球 FPGA 創新技術領導者 Altera 的 Agilex 5 FPGA 與 SoC 產品系列,榮獲 2025 年 AspenCore 全球電子成就獎(WEAA)的處理器/DSP

Altera Agilex 5 D系列FPGA和SoC家族全面升級

Agilex 5 D 系列 FPGA 和 SoC 家族全面升級,為中端 FPGA 應用能力帶來巨大飛躍——邏輯單元、內存、DSP/AI 算力提升高達 2.5 倍,外存帶寬提升高達 2

使用Xilinx 7系列FPGA的四位乘法器設計

(Shinshu University)研究團隊的最新設計中,一個專為 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了僅 11 個 LUT + 2 個 CARRY4 塊,關鍵路徑延遲達到 2.75 ns。這是一

DSP、FPGA之間SRIO通信的問題?

目前在使用DSP和FPGA之間通過SRIO的SWRITE事務完成雙向數據通信,大多數情況下都正常,但是在我不停的給DSP進行燒寫程序時,會偶爾出錯,FPGA無法收到

發表于 11-15 16:22

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全國產化信號處理平臺

的Kintex-7系列FPGAJFM7K325T16作為協處理單元,具有1個FMC子卡接口,具有4路SFP+萬兆光纖接口,具有2路RJ45千兆以太網接口,其中1路掛在FP

一文詳解xilinx 7系列FPGA配置技巧

本文旨在通過講解不同模式的原理圖連接方式,進而配置用到引腳的含義(手冊上相關引腳含義有四、五頁,通過本文理解基本上能夠記住所有引腳含義以及使用場景),熟悉xilinx 7系列配置流程,以及設計原理圖時需要注意的一些事項,比如flash與

中科億海微SoM模組——FPGA+DSP核心板

FPGA+DSP核心板是基于中科億海微EQ6HL130型FPGA芯片搭配國產DSP開發的高性能核心板卡。對外接口采取郵票孔連接方式,可以極大提高信號傳輸質量和焊接后的機械強度。核心板卡的系統框圖如下

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

Ultrascale是賽靈思開發的支持包含步進功能的增強型FPGA架構,相比7系列的28nm工藝,Ultrascale采用20nm的工藝,主要有2個

Altera Agilex 7 M系列FPGA正式量產出貨

近日,全球 FPGA 創新技術領導者 Altera 宣布, Agilex 7 M 系列 FPGA 正式量產出貨,這是現階段業界領先的集成高帶寬存儲器,并支持 DDR5 和 LPDDR5

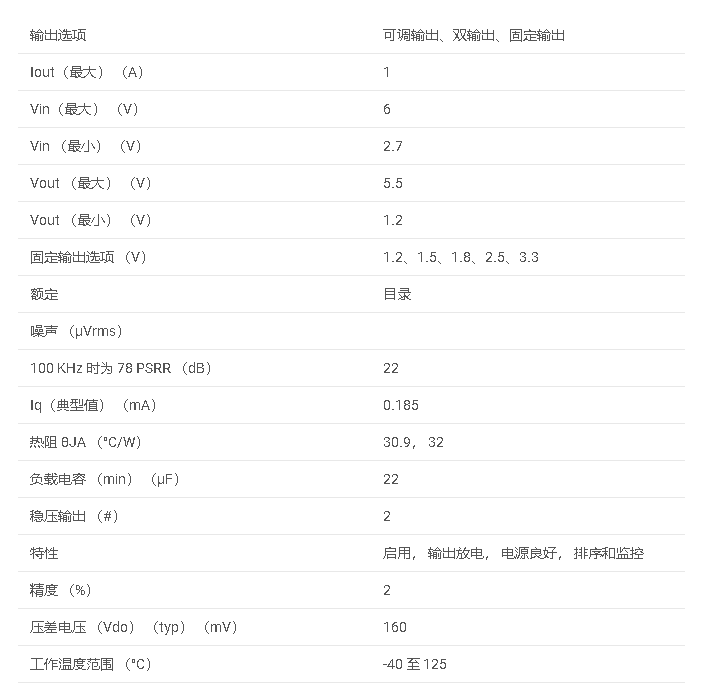

數據手冊#TPS703系列 1-A,雙通道超低壓差穩壓器,具有電源正常和啟用功能

TPS703xx 系列器件旨在為需要雙輸出電壓穩壓器的 TI DSP、處理器電源、ASIC、FPGA 和數字應用提供完整的電源管理解決方案。時序控制功能易于編程,使該

Virtex-7 FPGA系列DSP Slice功能的討論

Virtex-7 FPGA系列DSP Slice功能的討論

評論