FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。

2017-06-21 16:05:57 8433

8433

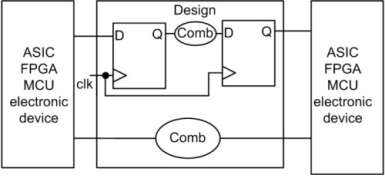

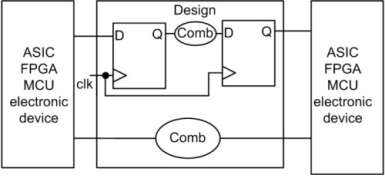

表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數(shù)據(jù)路徑和目的時鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 3687

3687

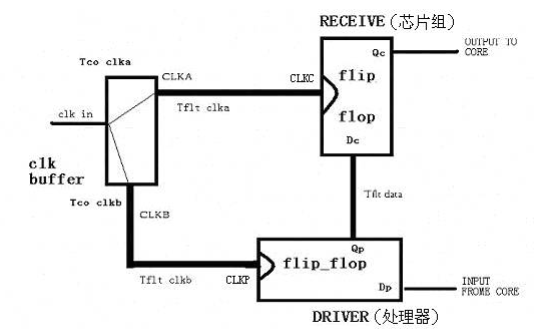

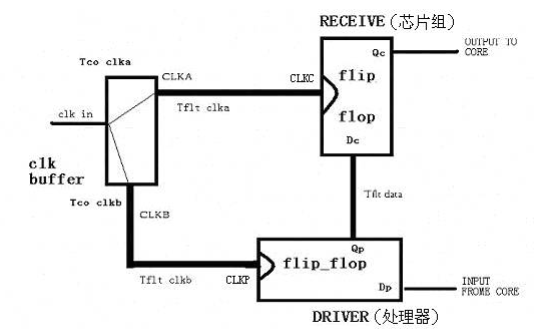

約束流程 說到FPGA時序約束的流程,不同的公司可能有些不一樣。反正條條大路通羅馬,找到一種適合自己的就行了。從系統(tǒng)上來看,同步時序約束可以分為系統(tǒng)同步與源同步兩大類。簡單點來說,系統(tǒng)同步是指

2020-11-20 14:44:52 9155

9155

在高速系統(tǒng)中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 計算和分析。同時,時序和信號完整性也是密不可分的,良好的信號質量是確保穩(wěn)定的時序的關鍵,由于反射,串擾造成的信號質量問題都很可能帶來時序的偏移和紊亂。因此,對于一個信號完整性工程師來說,如果不懂得系統(tǒng)

2022-12-13 10:50:35 2848

2848

FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 1938

1938

在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 12757

12757

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 4234

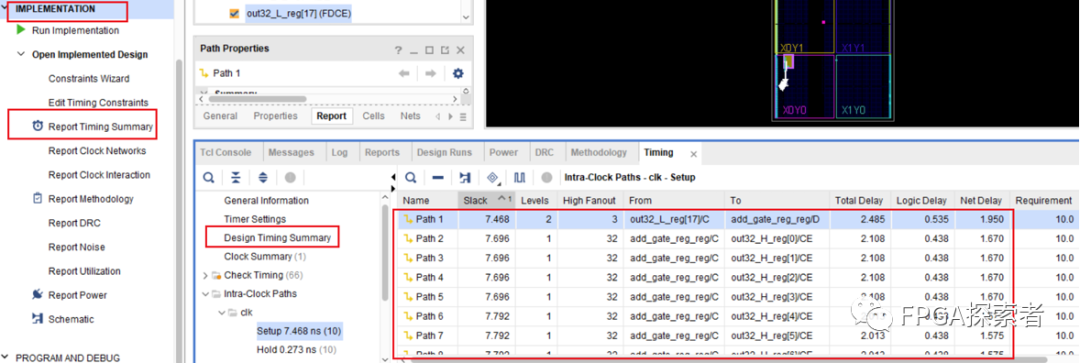

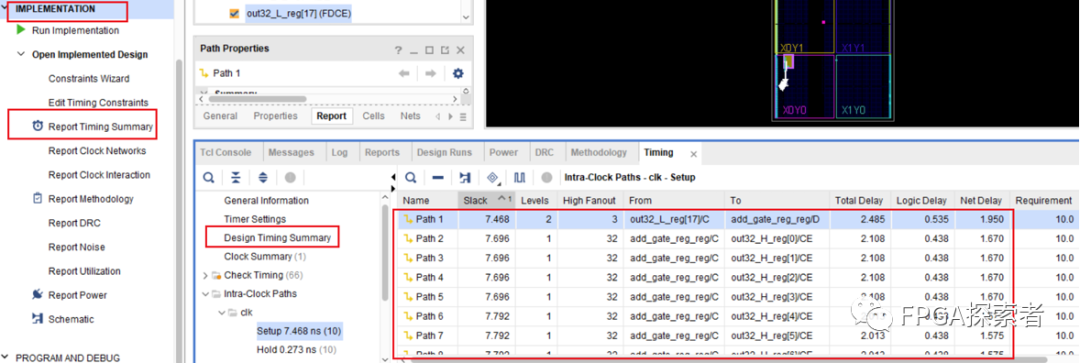

4234 關鍵路徑通常是指同步邏輯電路中,組合邏輯時延最大的路徑(這里我認為還需要加上布線的延遲),也就是說關鍵路徑是對設計性能起決定性影響的時序路徑。

2023-06-21 14:14:16 3117

3117

今天跟大家分享的內容很重要,也是調試FPGA經驗的總結。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼

2023-08-01 09:18:34 3075

3075

FPGA中時序約束是設計的關鍵點之一,準確的時鐘約束有利于代碼功能的完整呈現(xiàn)。進行時序約束,讓軟件布局布線后的電路能夠滿足使用的要求。

2023-08-14 17:49:55 2211

2211

時序路徑作為時序約束和時序分析的物理連接關系,可分為片間路徑和片內路徑。

2023-08-14 17:50:02 1542

1542

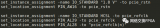

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 3030

3030

在數(shù)字IC/FPGA設計的過程中,對PPA的優(yōu)化是無處不在的,也是芯片設計工程師的使命所在。此節(jié)主要將介紹performance性能的優(yōu)化,如何對時序路徑進行優(yōu)化,提高工作時鐘頻率。

2025-12-09 10:33:20 2961

2961

FPGA系統(tǒng)設計實質上是一個同步時序系統(tǒng)的設計,理解時序概念,掌握代碼優(yōu)化與綜合技術,正確完整地進行時序約束和分析是實現(xiàn)高性能系統(tǒng)的重要保證。很多同學在設計中都會碰到時序方面的問題,如何解決時序難題

2018-06-07 15:52:07

今天給大俠帶來FPGA 高級設計:時序分析和收斂,話不多說,上貨。

這里超鏈接一篇之前的STA的文章,僅供各位大俠參考。

FPGA STA(靜態(tài)時序分析)

什么是靜態(tài)時序分析?靜態(tài)時序分析就是

2024-06-17 17:07:28

FPGA時序分析系統(tǒng)時序基礎理論對于系統(tǒng)設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫窗口越來越小,要想在很短的時間限制里,讓數(shù)據(jù)信號從驅動端完整

2012-08-11 17:55:55

經過兩天的惡補,特別是學習了《第五章_FPGA時 序收斂》及其相關的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據(jù)一些官方的文件對時序分析進行更系統(tǒng)、深入的學習。先總結一下之前

2011-09-23 10:26:01

和時鐘偏差組成的。

二、時序路徑

時序路徑是指從FPGA輸入到輸出的所有邏輯路徑組成的路徑。當存在時序路徑時,需要考慮時序約束以確保正確的邏輯功能和時序性能。

時序路徑中的關鍵元素包括:

(1) 路徑

2023-11-15 17:41:10

FPGA時序約束,總體來分可以分為3類,輸入時序約束,輸出時序約束,和寄存器到寄存器路徑的約束。其中輸入時序約束主要指的是從FPGA引腳輸入的時鐘和輸入的數(shù)據(jù)直接的約束。共分為兩大類:1、源同步系統(tǒng)

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束

2016-06-02 15:54:04

不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束+時序例外約束+I/O約束 I/O約束包括引腳分配位置、空閑引腳驅動方式、外部走線延時

2017-12-27 09:15:17

FPGA時序相關的資料。都看完看懂時序就沒問題了。分了三個附件:第一個是通過一些例子教你如何搞定時序分析。第二個附件是網(wǎng)上各種大神們對時序的理解,主要是他們的博客鏈接以及網(wǎng)站鏈接。第三個是其他的一些零散的關于時序的資料。

2012-11-12 17:45:28

FPGA中的I_O時序優(yōu)化設計在數(shù)字系統(tǒng)的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優(yōu)化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

FPGA時鐘時序資料

2014-06-03 20:13:27

FPGA的時序優(yōu)化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優(yōu)化的方法。1.FPGA靜態(tài)時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優(yōu)化方法

2013-03-27 15:20:27

FPGA/CPLD的綜合、實現(xiàn)過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

延遲。 首先,我們使用TimingDesigner軟件通過存儲器數(shù)據(jù)表為QDR SRAM創(chuàng)造一個圖表 大多數(shù)的FPGA利用約束驅動進行布局和布線。時序約束為關鍵信號提供時序信息

2017-09-01 10:28:10

隨著FPGA器件體積和復雜性的不斷增加,設計工程師越來越需要有效的驗證方。時序仿真可以是一種能發(fā)現(xiàn)最多問題的驗證方法,但對許多設計來說,它常常是最困難和費時的方法之一。過去,采用標準臺式計算機的時序

2019-07-16 08:10:25

FPGA設計驗證關鍵要點不同于ASIC設計,FPGA設計中的標準元件或客制化實作,一般欠缺大量的資源及準備措施可用于設計驗證。由于可以重新程式化元件,更多時候驗證只是事后的想法。本文將探討在FPGA

2010-05-21 20:32:24

FPGA高級時序綜合教程The UCF FileUCF =用戶約束文件( User Constraints File )可以用文本編輯器和XilinxConstraints Editor (GUI

2012-08-11 11:28:50

fpga高手經驗談doc文檔在數(shù)字電路的設計中,時序設計是一個系統(tǒng)性能的主要標志,在高層次設計方法中,對時序控制的抽象度也相應提高,因此在設計中較難把握,但在理解RTL電路時序模型的基礎上,采用合理

2012-08-11 11:30:39

在學習fpga的過程中的疑問:1、在功能仿真和板級驗真后沒問題,還需要進行時序分析嗎2、怎么知道自己寫的代碼有時序問題?

2017-01-08 17:50:35

各位大俠,能否分享一下找到影響時序的關鍵路徑的一些經驗

2014-02-27 11:17:52

時序約束可以很復雜,這里我們先介紹基本的時序路徑約束,復雜的時序約束我們將在后面進行介紹。在本節(jié)的主要內容如下所示:·時序路徑和關鍵路徑的介紹 ·建立時間、保持時間簡述 ·時鐘的約束(寄存器-寄存器之間的路徑約束) ·輸入延時的約束 ·輸出延...

2021-07-26 08:11:30

和關鍵路徑調整為了獲得更好的時序,我們建議使用特定的代碼風格來描述有限狀態(tài)機、RAM、數(shù)學/DSP功能、時鐘樹和移位寄存器。結果會提高時序QoR,因為綜合工具能夠推斷一個實現(xiàn)使用了FPGA原語的構件

2019-08-11 08:30:00

什么是時序分析?時序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

什么是時序路徑和關鍵路徑?常見的時序路徑約束有哪些?

2021-09-28 08:13:15

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現(xiàn)在有一些

2021-05-18 15:55:00

了如何通過FPGA實現(xiàn)RS 232接口的時序邏輯設計。關鍵詞:FPGA;時序電路;RS 232;串行通信

2019-06-19 07:42:37

。掌握分析和確定關鍵路徑時序的方法,并通過分析找出關鍵路徑的時序問題,再對關鍵路徑進行優(yōu)化,通過RTL層面的不斷優(yōu)化,不斷修煉自己的設計能力,讓設計出來的電路更為靠譜有效!本資料屬大西瓜FPGA開發(fā)團隊,在此開源,與大家一起學習FPGA!

2017-02-26 09:42:48

大家好,我想知道如何實現(xiàn)硬件(FPGA)中的時序報告給出的時序。我的意思是,如何測量FPGA和FPGA中輸入信號的建立或保持時間與靜態(tài)時間報告給出的值進行比較。FPGA怪胎以上來自于谷歌翻譯以下

2019-01-15 11:07:15

延遲和確定正確的相位偏移。4. 使用FPGA設計要素大多數(shù)的FPGA利用約束驅動進行布局和布線。時序約束為關鍵信號提供時序信息。TimingDesigner提供獨特的時序參考圖如測量和計算變量結果,從

2009-04-14 17:03:52

1. FPGA時序的基本概念FPGA器件的需求取決于系統(tǒng)和上下游(upstream and downstrem)設備。我們的設計需要和其他的devices進行數(shù)據(jù)的交互,其他的devices可能是

2019-07-09 09:14:48

FPGA重要設計思想及工程應用之時序及同

在FPGA設計中最好的時鐘方案 是: 由專用的全局時鐘輸入引腳 動單個 主時鐘去控制設計項目中的每一個觸發(fā) 器

2010-02-09 10:29:36 51

51 如何有效的管理FPGA設計中的時序問題

當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單

2009-04-15 14:19:31 947

947

介紹了采用STA (靜態(tài)時序分析)對FPGA (現(xiàn)場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯(lián)的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1476

1476 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 FPGA重要設計思想及工程應用之時序及同步設計

2016-05-10 11:24:33 16

16 賽靈思FPGA設計時序約束指南,下來看看

2016-05-11 11:30:19 49

49 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 33

33 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設計中的時序問題

2017-01-14 12:49:02 14

14 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現(xiàn)在有一些

2017-02-09 01:59:11 510

510 Xilinx FPGA編程技巧常用時序約束介紹,具體的跟隨小編一起來了解一下。

2018-07-14 07:18:00 5223

5223

fpga時序收斂

2017-03-01 13:13:34 23

23 作時序和布局約束是實現(xiàn)設計要求的關鍵因素。本文是介紹其使用方法的入門讀物。 完成 RTL 設計只是 FPGA 設計量產準備工作中的一部分。接下來的挑戰(zhàn)是確保設計滿足芯片內的時序和性能要求。為此,您

2017-11-17 05:23:01 3260

3260

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現(xiàn)時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

針對八通道采樣器AD9252的高速串行數(shù)據(jù)接口的特點,提出了一種基于FPGA時序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數(shù)據(jù),利用FPGA內部的時鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 7352

7352

現(xiàn)有的工具和技術可幫助您有效地實現(xiàn)時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現(xiàn)工具為滿足時序要求而優(yōu)化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 3842

3842 作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現(xiàn)時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現(xiàn)

2017-11-24 19:37:55 5955

5955

FPGA的設計與高速接口技術可以幫助你滿足今天的市場要求,但也提出了一些有趣的設計挑戰(zhàn)。為了確保存儲器接口的數(shù)據(jù)傳輸準確,在超過200兆赫茲以上,進行時序分析將發(fā)揮更突出的作用,以識別和解決系統(tǒng)運行

2017-11-25 01:06:01 1541

1541

的數(shù)量,可以用消耗的觸發(fā)器和查找表的個數(shù)或者是等效邏輯門數(shù)來衡量;速度是指一個設計在FPGA上穩(wěn)定運行時所能 達到的最高頻率,由設計時序狀態(tài)決定。 關于面積和速度的折衷,應在滿足設計時序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規(guī)定

2017-11-25 03:57:01 1471

1471

FPGA時序布局算法TMDCP。將退火過程分發(fā)至多線程執(zhí)行,利用TM機制保證共享內存訪問的合法性,并將改進的時序優(yōu)化算法嵌入到事務中并發(fā)執(zhí)行。測試結果表明,與通用布局布線工具相比,8線程下的TMDCP算法在總線長僅有輕微增加的情況下,關鍵

2018-02-26 10:09:04 0

0 FPGA時序收斂讓你的產品達到最佳性能!

2018-04-10 11:38:48 19

19 FPGA設計中,層次結構設計和復位策略影響著FPGA的時序。在高速設計時,合理的層次結構設計與正確的復位策略可以優(yōu)化時序,提高運行頻率。

2019-02-15 15:15:53 1270

1270 關鍵詞:FPGA , 國產 , 國產FPGA , 試用 作者在:特權同學 關于時序工具的一些FAE解答: 問:你們的工具是否只提供所有輸入輸出管腳完全一致的時序約束?如tsu,th,tco,tpd

2019-02-25 18:24:01 740

740

本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

2019-03-27 10:56:04 20

20 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:08:00 3476

3476

時序分析結果,并根據(jù)設計者的修復使設計完全滿足時序約束的要求。本章包括以下幾個部分: 1.1 靜態(tài)時序分析簡介 1.2 FPGA 設計流程 1.3 TimeQuest 的使用 1.4 常用時序約束 1.5 時序分析的基本概念

2020-11-11 08:00:00 67

67 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態(tài)時序分析與邏輯設計包括了:靜態(tài)時序分析一概念與流程,靜態(tài)時序分析一時序路徑,靜態(tài)時序分析一分析工具

2020-12-21 17:10:54 22

22 說到FPGA時序約束的流程,不同的公司可能有些不一樣。反正條條大路通羅馬,找到一種適合自己的就行了。從系統(tǒng)上來看,同步時序約束可以分為系統(tǒng)同步與源同步兩大類。簡單點來說,系統(tǒng)同步是指FPGA與外部

2021-01-11 17:46:32 14

14 在高速系統(tǒng)中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德?lián)P時序約束專題課視頻。

2022-03-16 09:17:19 4001

4001

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時序分析時FPGA設計中永恒的話題,也是FPGA開發(fā)人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德?lián)P時序約束專題課視頻。

2022-05-11 10:07:56 4989

4989

明德?lián)P有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發(fā)器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發(fā)器開始講起。

2022-07-11 11:33:10 6143

6143

本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德?lián)P時序約束專題課視頻。

2022-07-25 15:37:07 3757

3757

FPGA/CPLD的綜合、實現(xiàn)過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 2404

2404 隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼可能無法滿足時序要求。

2023-05-06 09:33:27 1544

1544

STA(Static Timing Analysis,即靜態(tài)時序分析)在實際FPGA設計過程中的重要性是不言而喻的

2023-06-26 09:01:53 1276

1276

FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 1252

1252

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會提供時序報告,以方便開發(fā)者判斷自己的工程時序是否滿足時序要求。

2023-06-26 15:29:05 2343

2343

FPGA時序不收斂,會出現(xiàn)很多隨機性問題,上板測試大概率各種跑飛,而且不好調試定位原因,所以在上板測試前,先優(yōu)化時序,再上板。

2023-06-26 15:41:31 3800

3800

FPGA高級時序綜合教程

2023-08-07 16:07:55 9

9 FPGA時序仿真和功能仿真在芯片設計和驗證過程中各自扮演著不可或缺的角色,它們之間存在明顯的區(qū)別。

2024-03-15 15:28:40 3702

3702 建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2024-08-06 11:40:18 2365

2365

電子發(fā)燒友網(wǎng)站提供《FPGA電源時序控制.pdf》資料免費下載

2024-08-26 09:25:41 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評論