I/O約束 I/O約束是必須要用的約束,又包括管腳約束和延遲約束。 管腳約束 管腳約束就是指管腳分配,我們要指定管腳的PACKAGE_PIN和IOSTANDARD兩個屬性的值,前者指定了管腳的位置

2020-10-30 16:08:13 17476

17476

對話框的約束部分下,選擇默認約束設置作為活動約束設置;包含在Xilinx設計約束(XDC)文件中捕獲的設計約束的一組文件,可以將其應用于設計中。兩種類型的設計約束是: 1) 物理約束:這些約束定義引腳

2020-11-23 14:16:36 6670

6670

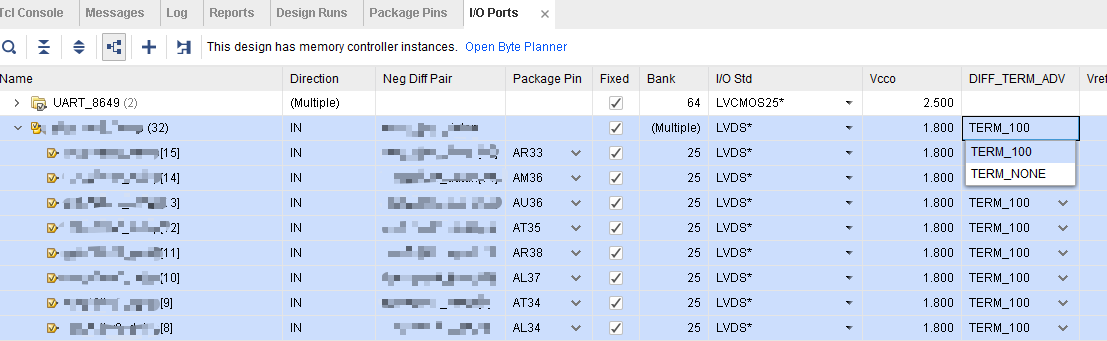

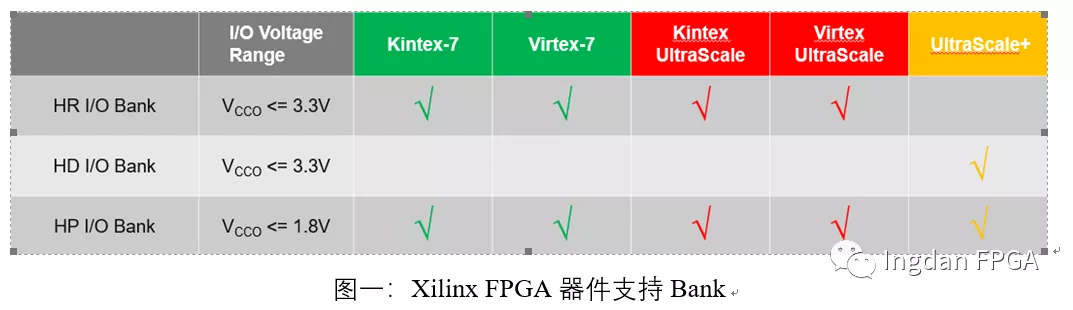

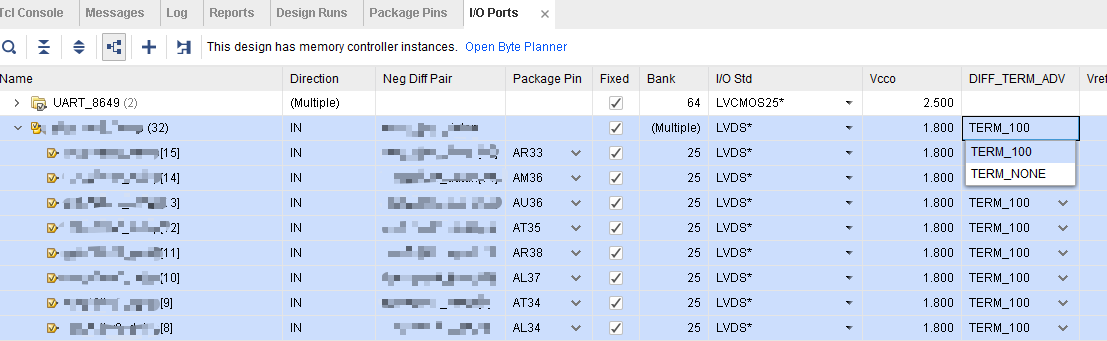

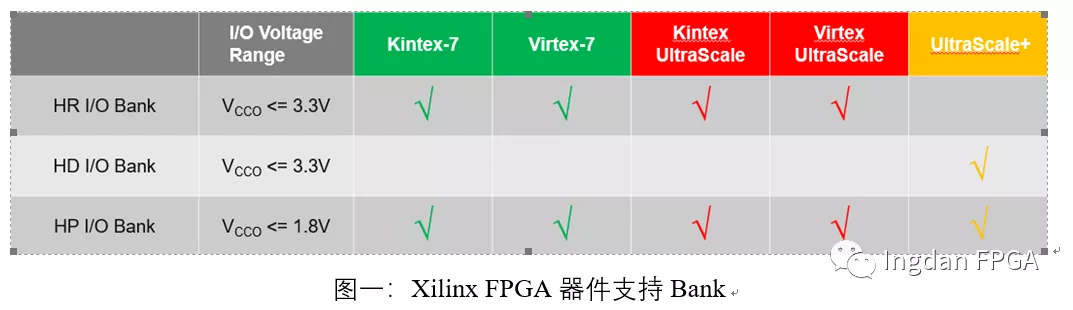

FPGA是電子器件中的萬能芯片,Xilinx FPGA處于行業龍頭地位更是非常靈活。FPGA管腳兼容性強,能跟絕大部分電子元器件直接對接。Xilinx SelectIO支持電平標準多,除MIPI

2022-08-02 09:31:28 7896

7896

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 12757

12757

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 4234

4234 前面幾篇FPGA時序約束進階篇,介紹了常用主時鐘約束、衍生時鐘約束、時鐘分組約束的設置,接下來介紹一下常用的另外兩個時序約束語法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 3055

3055 前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 3030

3030

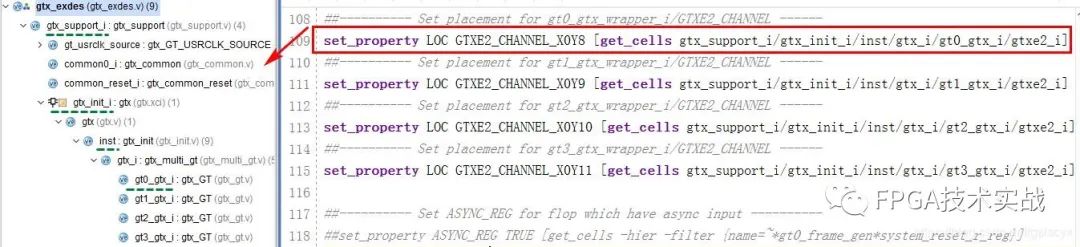

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

I/O約束(I/O Constraints)包括I/O標準(I/OStandard)約束和I/O位置(I/O location)約束。

2023-11-18 16:42:28 2442

2442

IS_ROUTE_FIXED命令用于指定網絡的所有布線進行固定約束。進入Implemented頁面后,Netlist窗口如圖1所示,其中Nets文件展開后可以看到工程中所有的布線網絡。

2023-12-16 14:04:31 2165

2165

在進行布局約束前,通常會對現有設計進行設計實現(Implementation)編譯。在完成第一次設計實現編譯后,工程設計通常會不斷更新迭代,此時對于設計中一些固定不變的邏輯,設計者希望它們的編譯結果

2024-01-02 14:13:53 2363

2363

FPGA 管腳分配需要考慮的因素FPGA 管腳分配需要考慮的因素 在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好

2012-08-11 10:27:54

今天給大俠帶來 Xilinx ISE14.7 LVDS應用,話不多說,上貨。

最近項目需要用到差分信號傳輸,于是看了一下FPGA上差分信號的使用。Xilinx FPGA中,主要通過原語實現差分信

2024-06-13 16:28:52

FPGA管腳分配需要考慮的因素 FPGA 管腳分配需要考慮的因素 在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好

2012-08-11 11:34:24

找到問題根源,后來在做另一個項目里,需要寫MAC的時序約束,發現Xilinx提供的MAC硬對‘RX_CLK’的時序約束要求很高,建立時間只有2.5ns,保持時間0.5ns,無論怎么反復修改這個約束值都無法

2019-07-09 08:00:00

,FPGA上的全局時鐘管腳用完了就出現不夠用的情況。FPGA全局時鐘約束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

鐘偏差。

Tlogic與我們寫的HDL代碼有直接關系,Trouting是FPGA開發軟件綜合布線根據FPGA內部資源情況進行布線產生的延時。

四、總結

本文介紹了FPGA時序約束的基礎理論

2023-11-15 17:41:10

不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束+時序例外約束+I/O約束 I/O約束包括引腳分配位置、空閑引腳驅動方式、外部走線延時

2017-12-27 09:15:17

你好: 現在我使用xilinx FPGA進行設計。遇到問題。我不知道FPGA設計是否符合時序要求。我在設計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應該被禁止。我

2019-03-18 13:37:27

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

本本將從常見的XILINX FPGA和Altera 兩家FPGA的電源供電作如下介紹:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

本帖最后由 china198 于 2013-8-30 12:28 編輯

XILINX的作品---時序約束,寫的非常棒

2013-08-30 12:26:47

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到

2021-05-28 09:23:25

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到

2021-07-08 08:00:00

各位大神,請問Xilinx FPGA中的DCI是如何使用的?我知道是把每個Bank的VRP、VRN管腳分別下拉、上拉,除此之外,在HDL代碼和約束中應該如何寫呢?查了半天資料沒有查到,所以來論壇問問。@LQVSHQ

2017-08-20 20:51:57

本帖最后由 eehome 于 2013-1-5 09:52 編輯

不可多得的Xilinx FPGA中文培訓材料教程,涉及到virtel的基本架構、賽靈思設計流程、如何閱讀報告、時序約束等經典

2012-03-02 09:51:53

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

2024-04-12 17:39:04

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

2024-05-06 15:51:23

在給 FPGA 做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在 FPGA 中都包含有4 種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入 到輸出的純組合邏輯

2012-03-05 15:02:22

Xilinx_fpga_設計:全局時序約束及試驗總結

2012-08-05 21:17:05

我用xilinx spartan-6fpga 它硬核的管腳是固定的還是可配置的我在xilinx提供的文檔里找不到關于硬核管腳的分配求指導

2012-08-11 09:28:44

網線的驅動源為同步點;附加在同步元件的輸出管腳上,則同步元件中驅動該管腳的源為同步點;附加在同步元件上,則輸出管腳為同步點;附加在同步元件的輸入管腳上,則該引腳被定義成同步點。(4)局部約束1多周期約束

2017-03-09 14:43:24

xilinx_fpga結構及工作原理介紹

2012-08-02 22:59:43

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述GTX/GTH收發器時鐘

2021-11-11 07:42:37

完成頂層模塊的實現并且仿真正確后,還需要編寫用戶約束文件,其中引腳約束文件是必不可少的,它將模塊的端口和 FPGA 的管腳對應起來。具體步驟如下。(1)創建約束文件。新建一個源文件,在代碼類型中選

2018-09-29 09:18:05

感謝電子發燒友論壇給予這次試用機會,一直想試用一下Xilinx FPGA,苦于沒有太多機會。這次就讓我好好領略一下Xilinx最新7系列FPGA的高大上。首先介紹一下安裝板卡文件的優勢:1、板載資源

2016-11-28 15:15:16

本視頻是MiniStar FPGA開發板的配套視頻課程,主要通過工程實例介紹Gowin的物理約束和時序約束,課程內容包括gowin的管腳約束及其他物理約束和時序優化,以及常用的幾種時序約束。 本

2021-05-06 15:40:44

流程1.3.1 FPGA設計方法概論1.3.2 典型FPGA開發流程1.3.3 基于FPGA的SOC設計方法1.4 Xilinx公司主流可編程邏輯器件簡介1.4.1 Xilinx FPGA芯片介紹

2012-04-24 09:23:33

右鍵然后點擊 show IO banks,這個時候就會看到FPGA的管腳被幾種顏色劃分開了。一種顏色下的IO口代表一組bank。你在吧管腳的locaTIon約束完成以后。IO Bank會自動填充完畢

2019-04-03 07:00:00

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是

2015-01-06 17:38:22

大家好, 誰能告訴我如何在RTL或xilinx spartan fpga的約束文件中插入1.56ns延遲緩沖區?這是為了避免xilinx工具在進行合成后報告的保持時間違規。問候馬赫什以上來自于谷歌

2019-06-18 07:18:04

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產品介紹使用Xilinx的FPGA、SoC和ACAP進行設計和開發

2021-01-22 06:38:47

大家好我正在使用Virtex5 FPGA,我在設計中添加了一個OFFSET IN約束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

物理約束文件ADC可做哪些約束?

2023-08-11 08:37:29

十分鐘學會Xilinx FPGA 設計

Xilinx FPGA設計基礎系統地介紹了Xilinx公司FPGA的結構特點和相關開發軟件的使用方法,詳細描述了VHDL語言的語法和設計方法,并深入討

2010-03-15 15:09:08 179

179 在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮這種方法往往是不可取的,RTL驗證

2011-01-25 18:19:39 163

163 電子發燒友網:針對目前 電子發燒友網 舉辦的 玩轉FPGA:iPad2,賽靈思開發板等你拿 ,小編在電話回訪過程中留意到有很多參賽選手對 Xilinx 公司的 FPGA 及其設計流程不是很熟悉,所以

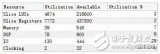

2012-06-27 13:39:47 339

339 本文是關于 xilinx公司的7系列FPGA應用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 Xilinx FPGA設計進階(提高篇)

有需要的下來看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發環境

2016-01-18 15:30:32 52

52 Xilinx時序約束設計,有需要的下來看看

2016-05-10 11:24:33 18

18 FPGA學習資料教程之Xilinx時序約束培訓教材

2016-09-01 15:27:27 0

0 FPGA學習資料教程之Xilinx-FPGA-引腳功能詳細介紹

2016-09-01 15:27:27 0

0 研究了相關的時序約束后,在設計中我們也不能忽視所能運用到的物理約束。一個工程師最常用的物理約束是I/O管腳的放置和與每個I/O腳相關的參數定義(標準、驅動能力等)。然而,還有其它類型的物理約束

2017-02-08 02:20:11 477

477

引腳和區域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應關系。 那么我們應該怎么寫呢?

2018-07-14 02:49:00 11898

11898 Xilinx FPGA編程技巧常用時序約束介紹,具體的跟隨小編一起來了解一下。

2018-07-14 07:18:00 5223

5223

FPGA設計中的約束文件有3類:用戶設計文件(.UCF文件)、網表約束文件(.NCF文件)以及物理約束文件(.PCF文件),可以完成時序約束、管腳約束以及區域約束。

2017-02-11 06:33:11 2023

2023 xilinx 約束實現

2017-03-01 13:12:47 15

15 Xilinx FPGA的Maxim參考設計

2017-10-31 09:59:24 23

23 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

針對八通道采樣器AD9252的高速串行數據接口的特點,提出了一種基于FPGA時序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數據,利用FPGA內部的時鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 7352

7352

本文主要通過一個實例具體介紹ISE中通過編輯UCF文件來對FPGA設計進行約束,主要涉及到的約束包括時鐘約束、群組約束、邏輯管腳約束以及物理屬性約束。 Xilinx定義了如下幾種約束類型

2017-11-24 19:59:29 4435

4435

摘要:本文主要通過一個實例具體介紹ISE中通過編輯UCF文件來對FPGA設計進行約束,主要涉及到的約束包括時鐘約束、群組約束、邏輯管腳約束以及物理屬性約束。 Xilinx定義了如下幾種約束類型

2017-11-25 01:27:02 7029

7029

詳細講解了xilinx的時序約束實現方法和意義。包括:初級時鐘,衍生時鐘,異步時終域,多時終周期的講解

2018-01-25 09:53:12 6

6 介紹FPGA約束原理,理解約束的目的為設計服務,是為了保證設計滿足時序要求,指導FPGA工具進行綜合和實現,約束是Vivado等工具努力實現的目標。所以首先要設計合理,才可能滿足約束,約束反過來檢查

2018-06-25 09:14:00 7199

7199 觀看視頻,了解和學習有關XDC約束,包括時序,以及物理約束相關知識。

2019-01-07 07:10:00 7145

7145

了解如何將Altera的SDC約束轉換為Xilinx XDC約束,以及需要更改或修改哪些約束以使Altera的約束適用于Vivado設計軟件。

2018-11-27 07:17:00 5883

5883 本文檔的主要內容詳細介紹的是xilinx的FPGA芯片選型手冊免費下載

2019-02-13 17:16:34 52

52 本篇主要介紹Xilinx FPGA的電源設計,主要包括電源種類、電壓要求、功耗需求,上下電時序要求,常見的電源實現方案等。

2019-02-17 11:03:52 11926

11926

本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 6756

6756 1 I/O延遲約束介紹 要在設計中精確建模外部時序,必須為輸入和輸出端口提供時序信息。Xilinx Vivado集成設計環境(IDE)僅在FPGA邊界內識別時序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 6236

6236 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個工藝級別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點 4.7系列

2020-11-13 18:03:30 16550

16550 本文檔的主要內容詳細介紹的是Xilinx 7 系列FPGA中的Serdes總結。

2020-12-31 17:30:58 26

26 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 26

26 本文檔的主要內容詳細介紹的是Xilinx的時序設計與約束資料詳細說明。

2021-01-14 16:26:51 34

34 引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到:

2021-05-01 09:47:00 11807

11807

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2021-04-27 10:36:59 6127

6127

我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。

2021-04-27 10:45:29 9045

9045

AD7991 pmod Xilinx FPGA參考設計

2021-05-20 12:37:26 12

12 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

Xilinx FPGA開發實用教程資料包免費下載。

2022-04-18 09:43:46 29

29 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德揚時序約束專題課視頻。

2022-07-25 15:37:07 3757

3757

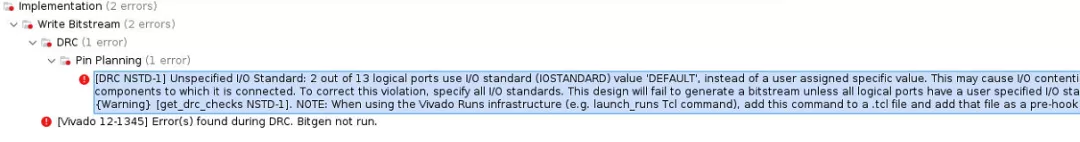

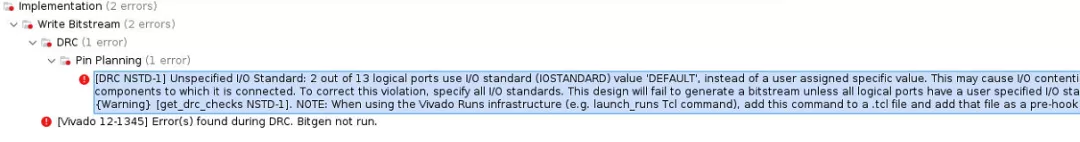

在FPGA開發中,我們經常遇到因為管腳忘記約束,導致最后生成bit的時候報錯。

2022-08-02 09:02:22 1838

1838

電子發燒友網站提供《Gowin設計物理約束用戶指南 .pdf》資料免費下載

2022-09-15 16:07:35 0

0 本篇主要介紹Xilinx FPGA的電源設計,主要包括電源種類、電壓要求、功耗需求,上下電時序要求,常見的電源實現方案等。

2022-10-17 17:43:39 8052

8052 約束文件是FPGA設計中不可或缺的源文件。那么如何管理好約束文件呢? 到底設置幾個約束文件? 通常情況下,設計中的約束包括時序約束和物理約束。前者包括時鐘周期約束、輸入/輸出延遲約束、多周期路徑約束

2022-12-08 13:48:39 2150

2150 FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 2404

2404 Xilinx FPGA pcb設計

2023-05-29 09:11:36 0

0 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 1252

1252

FPGA設計中,時序約束對于電路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應用,演示了TopJTAG Probe軟件的應用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應用,兩者幾乎是一樣。

2023-09-13 12:29:37 2690

2690

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 5686

5686 LOC約束是FPGA設計中最基本的布局約束和綜合約束,能夠定義基本設計單元在FPGA芯片中的位置,可實現絕對定位、范圍定位以及區域定位。

2024-04-26 17:05:05 2426

2426

xilinx FPGA IOB約束使用以及注意事項 一、什么是IOB約束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距離IO最近的寄存器,同時位置固定。當你輸入或者輸出

2025-01-16 11:02:01 1657

1657

Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設計。本文深入分析了Aurora、PCI Express和Serial RapidIO這三種在Xilinx系統設計中關鍵的串行通信協議。介紹了它們的特性、優勢和應用場景,以及如何在不同需求下選擇合適的協議。

2025-11-14 15:02:11 2357

2357

電子發燒友App

電子發燒友App

評論