在FPGA開發中,我們經常遇到因為管腳忘記約束,導致最后生成bit的時候報錯。

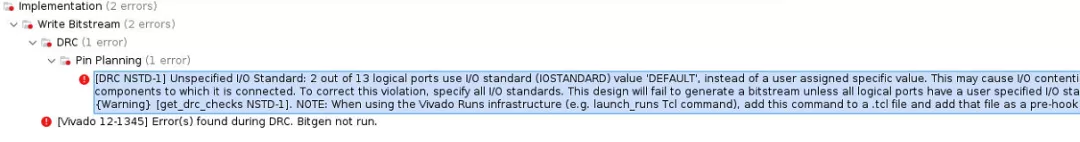

1.管腳電平未約束

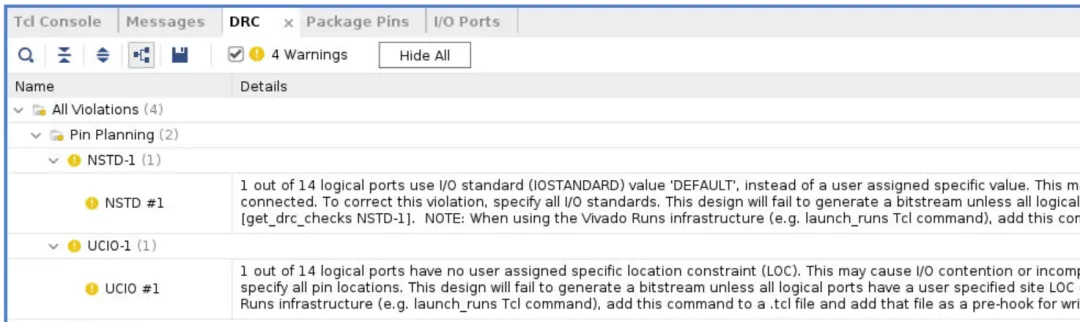

像上面這個圖中,由于在約束中忘記指定mdc和mdio的電平,再經過了長時間的綜合和實現后,最后的Generate Bitstream報錯了。

這種情況下,如何才能不重新Implementation的情況下生成bit呢?

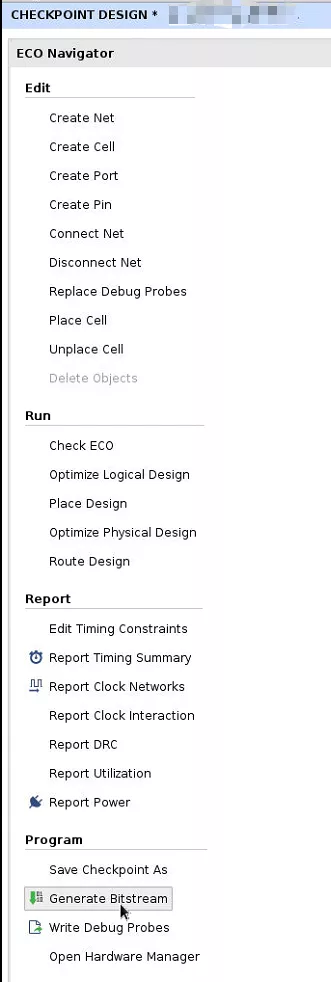

打開實現后的routed.dcp文件:

open_checkpoint ./Work/eth_demo.runs/impl_1/top_routed.dcp

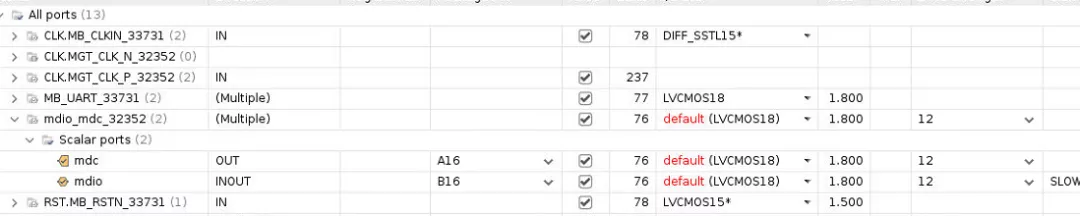

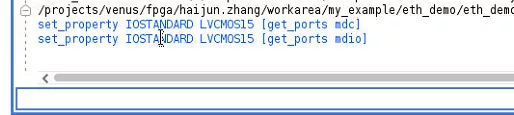

然后通過下面指令設置這兩個管腳的電平:

set_property IOSTANDARD LVCMOS15 [get_ports mdc] set_property IOSTANDARD LVCMOS15 [get_ports mdio]

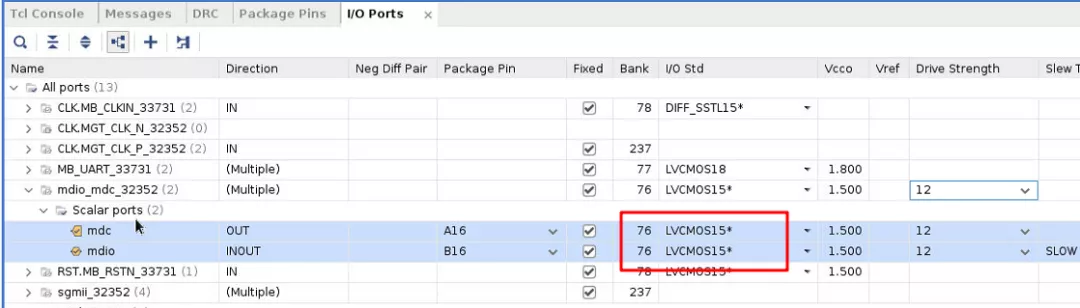

設置完成后,可以在I/O Ports窗口中看到這兩個管腳的電平已經改了過來

然后再點左側的生成bit:

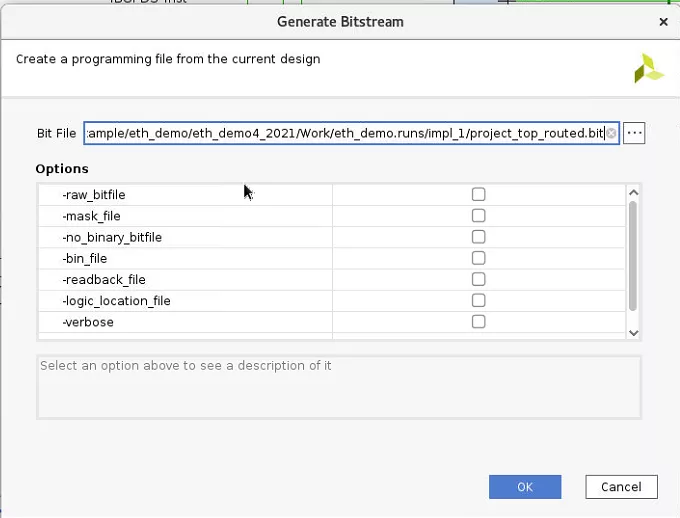

提示生成文件的位置和名字:

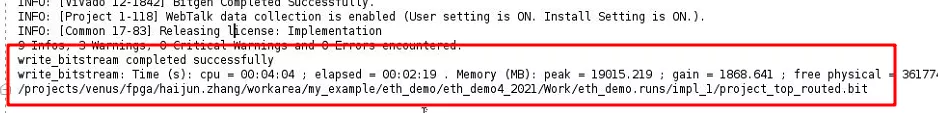

在正確生成后,可以看到tcl中提示write_bitstream completed successfully:

管腳電平修改后由于跟布局布線都沒有關系,因此直接生成bit是可以的。

2.管腳位置未約束

如果是管腳位置未約束,那我們就不能在dcp中修改位置然后直接生成bit了,因為位置變了,布局布線也需要改變。如果這個管腳的功能的需要的,那我們只能重新Implementation,如果這個管腳功能是不需要的,

那如果這個管腳的功能我們可以先不用,就想把經過了長時間的Synthsis和Implentation后的工程生成bit文件。

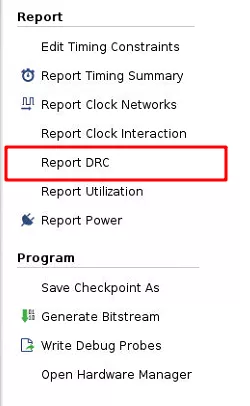

還是像上面一樣,打開route.dcp文件,然后點擊坐標的Report DRC

可以看到有兩個問題,一個是NSTD-1,一個是UCIO-1

我們只需要把這兩個DRC的問題設成warning,不讓工具在生成bit的時候報錯,也是可以生成bit的。執行tcl腳本如下:

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

然后再Generate Bitstream。

審核編輯:劉清

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636330 -

電平

+關注

關注

5文章

372瀏覽量

41604 -

管腳

+關注

關注

1文章

230瀏覽量

33690

發布評論請先 登錄

如何在LTspice仿真中實現偽隨機數和真隨機數的生成

求助,關于mcs文件生成的問題求解

win10環境下使用vivado生成.bit與.mcs文件

E203移植genesys2(差分時鐘板)生成比特流文件全過程

非對稱密鑰生成和轉換規格詳解

ez-usb3.0如何更改slfifosync中的數據,可以生成8bit數據位的usb固件?

PanDao:實際約束條件下成像系統的初始結構的生成

FX2LP如何在不更改硬件的情況下對其進行重新編程?

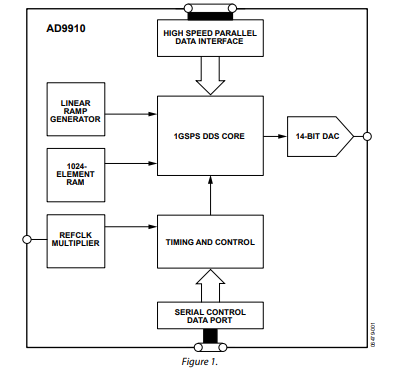

AD9910 1GSPS,14bit,3.3V CMOS直接數字頻率合成器技術手冊

管腳約束問題導致生成bit時報錯 如何在不重新Implentation情況下生成bit?

管腳約束問題導致生成bit時報錯 如何在不重新Implentation情況下生成bit?

評論