XDC 是 Xilinx Design Constraints 的簡寫,但其基礎語法來源于業界統一的約束規范SDC(最早由 Synopsys 公司提出,故名 Synopsys Design Constraints)。XDC 在本質上就是 Tcl 語言,但其僅支持基本的 Tcl 語法如變量、列表和運算符等等,對其它復雜的循環以及文件 I/O 等語法可以通過在 Vivado 中 source 一個 Tcl 文件的方式來補充。觀看視頻,了解和學習有關XDC約束,包括時序,以及物理約束相關知識。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133425 -

語言

+關注

關注

1文章

97瀏覽量

24833 -

時序

+關注

關注

5文章

406瀏覽量

38851

發布評論請先 登錄

相關推薦

熱點推薦

Vivado時序約束中invert參數的作用和應用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號的有效邊沿或邏輯極性。

尺寸約束下商業衛星編碼器系統的抗輻照MCU性能邊界研究

地研究在LQFP144塑封封裝所施加的物理尺寸約束條件下,商業航天級MCU的抗輻照性能邊界及其在衛星編碼器應用中的適配特性。 1. 引言 當前全球商業航天產業正經歷由低軌寬帶通信星座、地球觀測星座及物聯網星座驅動的爆發式增長。據

輸入引腳時鐘約束_Xilinx FPGA編程技巧-常用時序約束詳解

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為:

輸入路徑(Input Path),使用輸入約束

寄存器到寄存器路徑

發表于 01-16 08:19

聲智科技提出物理信息約束的聲學世界模型

scene denoising and dynamic prediction)入選,是計算聲學(Computational Acoustics)領域唯一入選的中國團隊。聲智聯合創始人常樂代表團隊做了學術報告,首次介紹物理信息約束

時序約束問題的解決辦法

Time 是否滿足約束。

我們要留意的是 WNS 和 WHS 兩個數值,如果這兩個數值為紅色,就說明時序不滿足約束。下面將解釋怎么解決這個問題。

1. Setup Time 違例

Setup

發表于 10-24 09:55

關于綜合保持時間約束不滿足的問題

1、將 nuclei-config.xdc 和 nuclei-master.xdc 加入到項目工程中,綜合得到時序約束報告如下:

保持時間約束不滿足,分析原因,發現所有不滿足均出現在

發表于 10-24 07:42

技術資訊 I Allegro 設計中的走線約束設計

,能夠在走線的時候清楚的知道目標在哪里,允許的誤差是多少、最小間距等。上期我們介紹了如何使用cadenceAllegro的規則“約束”孔,實現一鍵式快速生成孔;本期我

技術資訊 I 圖文詳解約束管理器-差分對規則約束

!Allegro約束管理器搞差分對,簡直是把高速設計的「地獄模式」切換成「新手村」!上期我們介紹了盲/埋孔的使用,本期我們將教會大家如何使用Cadence的約束管

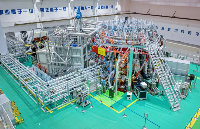

再創新高,“中國環流三號”實現百萬安培億度高約束模

近日,由核工業西南物理研究院(簡稱“西物院”)研制的新一代人造太陽“中國環流三號”再次創下我國聚變裝置運行新紀錄——實現百萬安培億度高約束模(H模),即裝置同時實現等離子體電流100萬安培、離子溫度

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發商

精彩看點 此次收購將幫助系統級芯片 (SoC) 設計人員通過經市場檢驗的時序約束管理能力來加速設計,并提高功能約束和結構約束的正確性 ? 西門子宣布 收購 Excellicon 公司 ,將該公司用于

PCB Layout 約束管理,助力優化設計

本文重點PCBlayout約束管理在設計中的重要性Layout約束有助避免一些設計問題設計中可以使用的不同約束在PCB設計規則和約束管理方面,許多設計師試圖采用“一刀切”的方法,認為同

PanDao:實際約束條件下成像系統的初始結構的生成

摘要 :初始點的選擇對后續設計過程具有重大影響。除透鏡規格外,其它必要的實際約束條件也可能起到非常關鍵的作用。本研究采用“First Time Right”方法生成受約束的初始系統,并運用

發表于 05-07 08:57

FPGA時序約束之設置時鐘組

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析時鐘組中時鐘的時序路徑,使用set_false_path約束則會雙向忽略時鐘間的時序路徑

XDC約束及物理約束的介紹

XDC約束及物理約束的介紹

評論