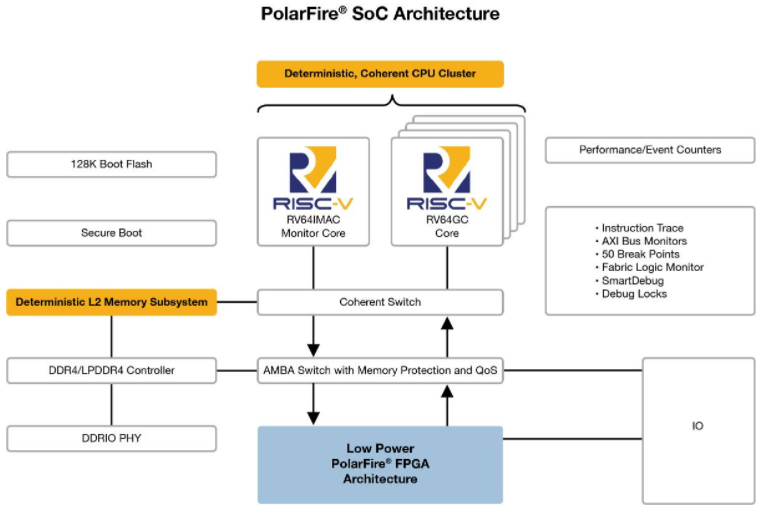

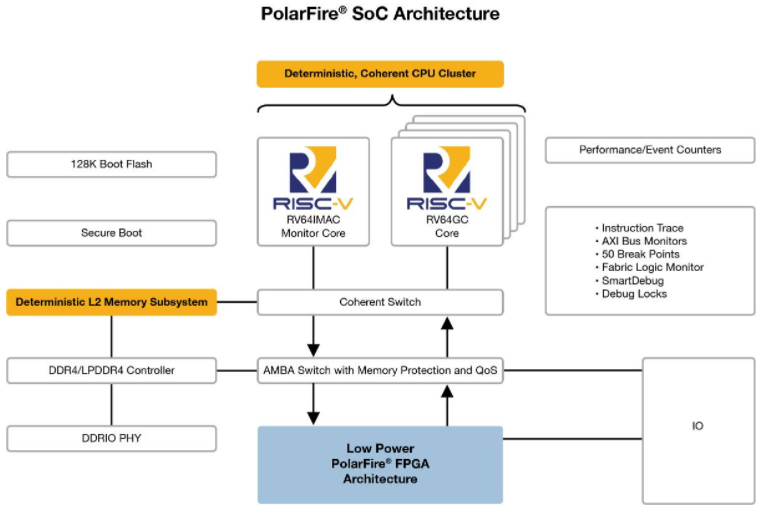

Microchip Technology Inc.(美國(guó)微芯科技公司)啟動(dòng)了PolarFire?片上系統(tǒng)(SoC)現(xiàn)場(chǎng)可編程門陣列(FPGA)早期使用計(jì)劃(EAP)。

2019-12-11 16:55:15 1608

1608 的Zynq 7000, 找了一個(gè)HLS的教程,就開始了如下入門實(shí)驗(yàn),體驗(yàn)高級(jí)語(yǔ)言綜合設(shè)計(jì)IP。Vivado HLS是Xilinx 推出的高層次綜合工具,采用C/C++語(yǔ)言進(jìn)行FPGA設(shè)計(jì)。HLS提供了一些

2020-10-14 15:17:19 4185

4185

直接使用C、C++或 System C 來(lái)對(duì) Xilinx 系列的 FPGA 進(jìn)行編程,從而提高抽象的層級(jí),大大減少了使用傳統(tǒng) RTL描述進(jìn)行 FPGA 開發(fā)所需的時(shí)間。

2025-04-16 10:43:12 1432

1432

Microchip 今日推出經(jīng)優(yōu)化的耐輻射RT PolarFire FPGA,為新興的高性能太空應(yīng)用市場(chǎng)帶來(lái)具備上述功能的新產(chǎn)品。

2019-10-23 17:04:10 1286

1286 Microsemi PolarFire FPGA視頻和成像套件配備帶有板載PolarFire FPGA的PolarFire視頻與成像板以及一個(gè)雙攝像頭傳感器板。

2019-11-08 11:23:33 1424

1424 Microchip開發(fā)系統(tǒng)高級(jí)總監(jiān)Rodger Richey表示:“目前,許多MCU產(chǎn)品的功能安全工具成本非常高,Microchip推出的功能安全產(chǎn)品的價(jià)格僅為某些競(jìng)爭(zhēng)性解決方案的三分之一,而且提供卓越的全球技術(shù)支持,助力客戶加快產(chǎn)品上市并進(jìn)一步簡(jiǎn)化開發(fā)流程。”

2020-01-21 00:27:00 4723

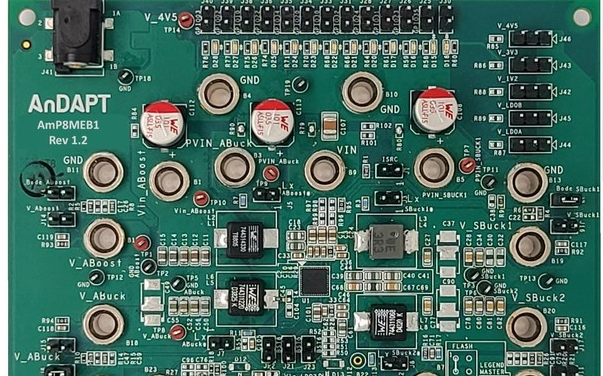

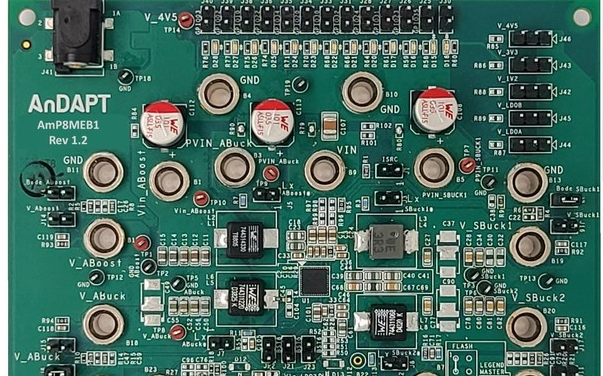

4723 AnDAPT現(xiàn)在支持使用集成、靈活和可編程的AmP電源管理IC為Microchip PolarFire FPGA供電。

2022-01-19 10:46:27 2559

2559

? 合集關(guān)鍵字 :Mi-V峰會(huì);Microchip;Polarfire SOC FPGA;Mercury+ MP1; RISC-V 今年, Enclustra 發(fā)布了其首款基于 Microchip

2022-08-15 15:20:25 1181

1181

的高級(jí)語(yǔ)言(如C++和C++)的準(zhǔn)入,這一點(diǎn)讓眾多軟件工程師甘之如飴。與硬件描述語(yǔ)言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程師掌握的工具。當(dāng)然,它也有局限性:語(yǔ)言限制,就像非可合成

2021-07-10 08:00:00

`為客戶提供完美的硅芯片解決方案是MICROCHIP堅(jiān)持不懈的目標(biāo)。但我們不只局限于提供硅芯片,還需要編程器、編譯器、參考設(shè)計(jì)、函數(shù)庫(kù)、應(yīng)用筆記和評(píng)估板等支持工具,以助您最高效地完成評(píng)估和產(chǎn)品開發(fā)

2011-03-09 14:59:00

的設(shè)計(jì)工具和資源,以幫助開發(fā)人員采用和改進(jìn) RISC-V 應(yīng)用程序設(shè)計(jì)。這些工具可與各種硬件套件結(jié)合使用——用于 PolarFire FPGA 的 PolarFire 評(píng)估套件和Icicle 套件

2021-09-07 17:59:56

、基于 RISC-V 的 PolarFire? SoC FPGA 打造,匯集了眾多的 Mi-V 合作伙伴,助力加速不同行業(yè)的客戶設(shè)計(jì)部署和商業(yè)應(yīng)用。 設(shè)計(jì)人員現(xiàn)在可以開始開發(fā)和評(píng)估實(shí)時(shí)操作系統(tǒng)(RTOS

2020-09-25 11:39:42

Microchip提供了一系列高度集成的開發(fā)工具,可以簡(jiǎn)化應(yīng)用程序的開發(fā)過(guò)程。這些工具分為核心開發(fā)工具和附屬工具。基本開發(fā)工具主要有:•MPLAB®集成開發(fā)環(huán)境

2011-03-08 16:50:21

目前有一個(gè)算法庫(kù) 用的c++ ?用ccs在dsp上可以調(diào)試

現(xiàn)在希望把庫(kù)放在8168的dsp上 ?需要將c++轉(zhuǎn)換成c 有個(gè)工具

mmCC C++-to-C Translator、

不知道論壇里有沒(méi)有 或者大家誰(shuí)有

如果找不到mmcc

那么 ?8168上dsp用c調(diào)用c++庫(kù) 有沒(méi)有可行性

2018-06-21 13:14:22

MYC-CZU3EG/4EV/5EV-V2核心板及開發(fā)板

在MYIR 的 ZU3EG 開發(fā)平臺(tái)上提供了一種高效的解決方案。利用 FPGA 獨(dú)特的靈活性和低功耗優(yōu)勢(shì),助力未來(lái) AIoT 設(shè)備的普及和智能升級(jí)。

2024-12-06 17:18:02

模擬過(guò)程完成沒(méi)有0錯(cuò)誤,但在合成期間顯示錯(cuò)誤。我無(wú)法找到錯(cuò)誤。我在合成期間在HLS工具中收到這樣的錯(cuò)誤“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

TI CC2541開發(fā)套件

2023-03-25 01:27:25

智能化設(shè)計(jì)平臺(tái),為用戶提供了一個(gè)接觸和操作底層算法的便捷途徑。

用戶無(wú)需進(jìn)行復(fù)雜的代碼編寫,可以一鍵套用工程模版,也可以通過(guò)圖形化界面自定義控制算法,就能夠輕松在實(shí)驗(yàn)室有限的環(huán)境中制作實(shí)物電路,快速開發(fā)

2025-08-14 11:30:35

HiHope 滿天星智能家居開發(fā)套件

2023-03-28 13:07:10

潤(rùn)和滿天星系列Pegasus智能小車開發(fā)套件,基于海思Hi3861V100芯片,支持OpenHarmony輕量系統(tǒng),實(shí)現(xiàn)巡線、避障功能通過(guò)尋跡模塊獲取路面軌道數(shù)據(jù),運(yùn)用尋跡算法使得智能小車可以按照固定軌道運(yùn)行

2023-03-28 13:07:10

加利福尼亞州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式發(fā)布。此次最新版本將幫助用戶加速FPGA原型開發(fā)、提高工程師的生產(chǎn)力,以及實(shí)現(xiàn)最高的原型

2019-07-02 06:23:44

/C++的編程技巧者優(yōu)先, 對(duì)圖像信號(hào)處理、識(shí)別、編解碼等算法有較好的基礎(chǔ);4、有良好的英文閱讀能力; 5、具有良好的團(tuán)隊(duì)合作精神和刻苦鉆研精神,責(zé)任心強(qiáng),能承受一定的工作壓力;6、有智能交通行業(yè)產(chǎn)品DSP開發(fā)經(jīng)驗(yàn)者優(yōu)先。工作地點(diǎn):武漢有意向者請(qǐng)窗我:QQ:1940783351

2013-07-16 11:07:23

的高級(jí)語(yǔ)言(如C++和C++)的準(zhǔn)入,這一點(diǎn)讓眾多軟件工程師甘之如飴。與硬件描述語(yǔ)言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程師掌握的工具。當(dāng)然,它也有局限性:語(yǔ)言限制,就像非可合成

2021-07-06 08:00:00

/C++進(jìn)行設(shè)計(jì),然后由Vivado HLS編譯器將C代碼綜合成HDL描述,最后再進(jìn)行邏輯綜合得到網(wǎng)表,這個(gè)網(wǎng)表最終會(huì)被映射到具體的FPGA器件上。就像C語(yǔ)言或者其他高級(jí)語(yǔ)言針對(duì)不同的處理器架構(gòu)有著

2020-10-10 16:44:42

拼接算法試用計(jì)劃:申請(qǐng)理由本人從事圖像處理,圖像編碼算法有十年開發(fā)經(jīng)驗(yàn),熟悉xilinx FPGA的編程,曾設(shè)計(jì)過(guò)ISP算法,由于有監(jiān)控場(chǎng)景需要寬幅圖像,想借助發(fā)燒友論壇和米爾MYD-C7Z020平臺(tái)

2019-10-30 17:03:31

庫(kù)文件,甚至可以引進(jìn)HDL程序,并進(jìn)行仿真,最終生成網(wǎng)表文件,放到FPGA中執(zhí)行。軟件算法工程師不需要特別的培訓(xùn),利用他們熟悉的C語(yǔ)言就可以直接進(jìn)行硬件開發(fā),減輕了硬件開發(fā)的瓶頸和壓力。隨著算法描述

2015-01-13 16:34:40

針對(duì)目標(biāo)FPGA優(yōu)化的RTL代碼。盡管英特爾的HLS工具在現(xiàn)場(chǎng)的使用率比Xilinx的Vivado HLS少得多,但隨著HLS編譯器為英特爾One API軟件開發(fā)平臺(tái)的“ FPGA”分支提供動(dòng)力,我們

2024-03-23 16:48:53

優(yōu)化 FPGA HLS 設(shè)計(jì)

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設(shè)計(jì)性能。

介紹

高級(jí)設(shè)計(jì)能夠以簡(jiǎn)潔的方式捕獲設(shè)計(jì),從而

2024-08-16 19:56:07

,我們一直在使用Vivado給我們提供的IP或者使用硬件描述語(yǔ)言制作 IP 。今天我們將講解如何使用HLS-高級(jí)綜合語(yǔ)言來(lái)創(chuàng)建屬于我們自己的IP。我們將使用的工具稱為Vitis HLS,此后稱為 HLS

2022-09-09 16:45:27

將C、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于OpenCL等框架對(duì)Xilinx可編程邏輯器件進(jìn)行開發(fā),可加速算法開發(fā)的進(jìn)程,縮短產(chǎn)品上市時(shí)間。HLS基本開發(fā)流程如下:(1) HLS工程新建/工程

2021-02-19 18:36:48

。

Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于 OpenCL 等框架對(duì) Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于 OpenCL 等框架對(duì) Xilinx

2023-01-01 23:52:54

(High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于 OpenCL 等框架對(duì) Xilinx 可編程邏輯器件進(jìn)行開發(fā),可加速算法開發(fā)的進(jìn)程,縮短

2023-01-01 23:46:20

(High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于 OpenCL 等框架對(duì) Xilinx 可編程邏輯器件進(jìn)行開發(fā),可加速算法開發(fā)的進(jìn)程,縮短

2023-08-24 14:54:01

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于OpenCL等框架

2021-11-11 09:38:32

和生成比特流以對(duì)FPGA進(jìn)行編程4 - 將比特流導(dǎo)入并阻塞到SDK中,基于此生成板級(jí)支持包(BSP)并與Zedboard連接。順便說(shuō)一下,SDK的目標(biāo)是成為我在Vivado HLS中的測(cè)試平臺(tái)嗎?即在計(jì)算機(jī)中觀察Zedboard產(chǎn)生的結(jié)果是否為例外情況。

2020-03-24 08:37:03

。Vivado HLS作為該套件的一個(gè)組件,能幫助設(shè)計(jì)人員將采用C/C++語(yǔ)言開發(fā)的算法編譯為RTL,以便在FPGA邏輯中運(yùn)行。Vivado HLS工具非常適用于嵌入式視覺(jué)設(shè)計(jì)。在此流程中,您用C/C++

2014-04-21 15:49:33

您好,我目前正在嘗試使用Vivado HLS在FPGA上合成加密算法。我根據(jù)需要拆分了C ++代碼并包含了一個(gè)測(cè)試平臺(tái),但是當(dāng)我嘗試模擬代碼時(shí),我得到一個(gè)錯(cuò)誤,說(shuō)找不到測(cè)試平臺(tái)。我附上了錯(cuò)誤圖片和項(xiàng)目檔案,希望有人能幫我找到解決方案。謝謝!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

進(jìn)行編譯的。本文僅驗(yàn)證了采用高級(jí)語(yǔ)言開發(fā)FPGA的可行性,還有很多優(yōu)化工作待完善,僅以此文為大家提供一個(gè)新的視角,為軟件開發(fā)人員利用FPGA進(jìn)行算法加速做前期調(diào)研,歡迎感興趣的同事共同交流。

2017-09-25 10:06:29

客戶能夠在小至 11 × 11 毫米的封裝尺寸上實(shí)施解決方案。Microchip 的 PolarFire SoC FPGA Icicle 工具包非常適合智能嵌入式成像、物聯(lián)網(wǎng)、工業(yè)自動(dòng)化、國(guó)防、汽車

2021-03-09 19:48:43

Visual C++ 6.0 高級(jí)編程,免費(fèi)下載:全面介紹了Visual C++ 6.0的中高級(jí)編程技術(shù),其內(nèi)容主要有:內(nèi)存管理、高級(jí)圖形處理、使用Internet、創(chuàng)建多線程程序、創(chuàng)建ActiveX和DLL、使用

2009-07-12 15:25:07 0

0 Intel Agilex? F系列FPGA開發(fā)套件Intel Agilex? F系列FPGA開發(fā)套件設(shè)計(jì)用于使用兼容PCI-SIG的開發(fā)板開發(fā)和測(cè)試PCIe 4.0設(shè)計(jì)。該開發(fā)套件還可通過(guò)硬核處理器

2024-02-27 11:51:58

MIDI合成算法及其FPGA實(shí)現(xiàn).

2012-04-16 13:57:38 44

44 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進(jìn)行 FPGA 設(shè)計(jì)的簡(jiǎn)介

2016-01-06 11:32:55 65

65 進(jìn)行編寫解析算法,把G 代碼作為一個(gè)對(duì)象,用類機(jī)制實(shí)現(xiàn)其解析功能,并使用GCC 作為其編譯器,提高編譯效率。可直接應(yīng)用嵌入式,脫離PC+運(yùn)動(dòng)控制卡的限制。通過(guò)實(shí)驗(yàn)的測(cè)試,以ARM 開發(fā)板為驗(yàn)證實(shí)驗(yàn)平臺(tái),以arm-none-eabi-gcc 為編譯工具,驗(yàn)證C++解

2016-07-21 16:36:32 0

0 FPGA學(xué)習(xí)資料教程之Xilinx-FPGA高級(jí)開發(fā)工具,感興趣的可以看看。

2016-09-01 15:27:27 0

0 眾所周知,HLS是Xilinx于幾年前推出的一個(gè)高級(jí)綜合工具,可以直接把C/C++代碼,轉(zhuǎn)換成可綜合的verilog/VHDL代碼。聽起來(lái)很高級(jí),是不是?。但看新鮮的人多,愿意吃螃蟹的人卻很少。這里

2017-02-08 05:07:20 2467

2467

HLS工具 以個(gè)人的理解,xilinx將HLS(高層次綜合)定位于更方便的將復(fù)雜算法轉(zhuǎn)化為硬件語(yǔ)言,通過(guò)添加某些配置條件HLS工具可以把可并行化的C/C++的代碼轉(zhuǎn)化為vhdl或verilog,相比于純?nèi)斯な褂胿hdl實(shí)現(xiàn)圖像算法,該工具綜合出的代碼的硬件資源占用可能較多。

2019-10-12 17:34:00 2937

2937

提供支持。SDAccel允許開發(fā)人員用 OpenCL?、C和C++語(yǔ)言描述他們的算法,并直接編譯到賽靈思FPGA加速板。托管的賽靈思SDAccel? 開發(fā)環(huán)境不僅會(huì)加速FPGA開發(fā)進(jìn)

2017-02-08 16:06:08 494

494 高層次綜合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA設(shè)計(jì)工具,它能讓用戶通過(guò)編寫C/C++等高級(jí)語(yǔ)言代碼實(shí)現(xiàn)RTL級(jí)的硬件功能。隨著這款工具

2018-07-14 06:42:00 8006

8006 Android C++高級(jí)編程----使用NDK

2017-03-19 11:23:45 3

3 測(cè)試用的大量采樣數(shù)據(jù),完成對(duì)硬件系統(tǒng)原型的評(píng)估。對(duì)于I/Q壓縮算法等類似高數(shù)據(jù)吞吐量的應(yīng)用,采用Vivado HLS工具進(jìn)行測(cè)試評(píng)估更加的方便。

2017-11-17 02:25:41 1856

1856

者對(duì)算法FPGA的實(shí)現(xiàn)難度。其中包括:

? 使用VivadoHLS開發(fā)效率比手寫RTL實(shí)現(xiàn)快5-10倍,而實(shí)現(xiàn)的FPGA資源效率與手寫RTL接近

? 由于C/C++仿真驗(yàn)證比傳統(tǒng)FPGA RTL要快100倍,Vivado HLS實(shí)現(xiàn)可以大大縮短用戶的代碼開發(fā)時(shí)間和仿真驗(yàn)證時(shí)間,從而大幅提高生產(chǎn)效率。

2017-11-17 17:47:43 4363

4363

如果您正在努力開發(fā)計(jì)算內(nèi)核,而且采用常規(guī)內(nèi)存訪問(wèn)模式,并且循環(huán)迭代間的并行性比較容易提取,這時(shí),Vivado? 設(shè)計(jì)套件高層次綜合(HLS) 工具是創(chuàng)建高性能加速器的極好資源。通過(guò)向C 語(yǔ)言高級(jí)算法描述中添加一些編譯指示,就可以在賽靈思FPGA 上快速實(shí)現(xiàn)高吞吐量的處理引擎。

2017-11-17 18:12:01 2315

2315 Vivado HLS配合C語(yǔ)言等高級(jí)語(yǔ)言能幫助您在FPGA上快速實(shí)現(xiàn)算法。 高層次綜合(HLS)是指自動(dòng)綜合最初用C、C++或SystemC語(yǔ)言描述的數(shù)字設(shè)計(jì)。工程師之所以對(duì)高層次綜合如此感興趣,不僅是因?yàn)樗茏尮こ處熢谳^高的抽象層面上工作,而且還因?yàn)樗芊奖愕厣啥喾N設(shè)計(jì)解決方案。

2019-10-06 10:44:00 1849

1849

、邊緣模糊等級(jí)和脈沖噪聲等指標(biāo)評(píng)估基于該算法圖像處理效果。與傳統(tǒng)時(shí)域算法作對(duì)比,對(duì)比結(jié)果表明該算法在處理效果和運(yùn)算速度上的優(yōu)異性。基于Zedboard開發(fā)板,運(yùn)用Vivado HLS高級(jí)綜合工具將算法的C程序綜合成硬件IP,并搭建了包含ARM處理器和VGA等

2017-12-12 14:07:38 2

2 本文介紹了PolarFire FPGA主要特性,低功耗特性,可靠特性和安全特性,框圖,以及PolarFire FPGA評(píng)估板硬件特性,框圖,電路圖和元件表以及PCB元件布局圖。

2018-06-17 18:06:00 6952

6952

應(yīng)用大比拼開擂 基于vivado HLS的幀差圖像實(shí)現(xiàn) 基于FPGA的實(shí)時(shí)移動(dòng)目標(biāo)的追蹤 類似嵌入式 C/C++/OpenCL 應(yīng)用開發(fā)的體驗(yàn) SDSoC 開發(fā)環(huán)境可為異構(gòu) Zynq SoC 及 MPSoC 部署

2018-05-21 14:16:00 2572

2572 HLS,高層綜合)。這個(gè)工具直接使用C、C++或SystemC 開發(fā)的高層描述來(lái)綜合數(shù)字硬件,這樣就不再需要人工做出用于硬件的設(shè)計(jì),像是VHDL 或Verilog 這樣的文件,而是由HLS 工具來(lái)做這個(gè)事情。

2018-06-04 01:43:00 7738

7738

子系統(tǒng)以及完整的 Vivado 實(shí)現(xiàn)工具套件,使主流用戶能夠方便地采用生產(chǎn)力最高、最先進(jìn)的C 語(yǔ)言和 IP設(shè)計(jì)流程。結(jié)合最新 UltraFast 高級(jí)生產(chǎn)力設(shè)計(jì)方法指南,相比采用傳統(tǒng)方法而言,用戶可將生產(chǎn)力提升 10-15 倍。全新HLx 版本將作為 Vivado 設(shè)計(jì)套件的免費(fèi)升級(jí)版提供。

2018-08-17 11:43:00 4072

4072 美高森美公司(Microsemi ) 宣布提供低成本IGLOO 2 FPGA評(píng)測(cè)工具套件,為客戶提供PCI Express (PCIe)兼容外形尺寸評(píng)測(cè)平臺(tái)。這款功能齊全的工具套件可讓設(shè)計(jì)人員快速評(píng)測(cè)美高森美最近發(fā)布的IGLOO2 FPGA器件的集成度、低成本、安全性、即時(shí)性和高可靠性特性。

2018-09-18 16:49:00 1914

1914 關(guān)鍵詞:Actel , Fusion , 高級(jí) , 工具 , 套件 愛(ài)特 (Actel) 正式付運(yùn)Fusion高級(jí)開發(fā)工具套件,協(xié)助設(shè)計(jì)人員開發(fā)系統(tǒng)和功率管理應(yīng)用。該工具套件帶有Actel

2018-10-24 20:44:01 1031

1031 了解如何使用GUI界面創(chuàng)建Vivado HLS項(xiàng)目,編譯和執(zhí)行C,C ++或SystemC算法,將C設(shè)計(jì)合成到RTL實(shí)現(xiàn),查看報(bào)告并了解輸出文件。

2018-11-20 06:09:00 4500

4500 使用Spartan-6 FPGA消費(fèi)類視頻套件加速DTV設(shè)計(jì)中高級(jí)視頻算法的開發(fā)。

與消費(fèi)者部門主管Harry Raftopoulos近距離觀看套件。

2018-11-28 06:15:00 2397

2397 盡管 Vivado HLS支持C、C++和System C,但支持力度是不一樣的。在v2017.4版本ug871 第56頁(yè)有如下描述。可見(jiàn),當(dāng)設(shè)計(jì)中如果使用到任意精度的數(shù)據(jù)類型時(shí),采用C++ 和System C 是可以使用Vivado HLS的調(diào)試環(huán)境的,但是C 描述的算法卻是不可以的。

2019-07-29 11:07:16 6103

6103

Xilinx 戰(zhàn)略應(yīng)用高級(jí)工程師。專注于 C/C++ 高層次綜合,擁有多年利用 Xilinx FPGA 實(shí)現(xiàn)數(shù)字信號(hào)處理算法的經(jīng)驗(yàn),對(duì) Xilinx FPGA 的架構(gòu)、開發(fā)工具和設(shè)計(jì)理念有深入的理解。

2019-08-01 15:30:49 2416

2416 接著開始正文。據(jù)觀察,HLS的發(fā)展呈現(xiàn)愈演愈烈的趨勢(shì),隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 7434

7434

Microchip啟動(dòng)了PolarFire片上系統(tǒng)(SoC)現(xiàn)場(chǎng)可編程門陣列(FPGA)早期使用計(jì)劃(EAP)。

2019-12-16 15:16:21 1053

1053 Microchip啟動(dòng)了PolarFire片上系統(tǒng)(SoC)現(xiàn)場(chǎng)可編程門陣列(FPGA)早期使用計(jì)劃(EAP)。

2019-12-26 15:39:03 1460

1460 ,Microchip Technology Inc.(美國(guó)微芯科技公司)宣布推出業(yè)界首款基于 RISC-V 的SoC FPGA開發(fā)工具包。這款名為Icicle 的開發(fā)工具包專為業(yè)界領(lǐng)先的低功耗、低成本

2020-09-24 09:37:29 4146

4146 2019年,Microchip Technology Inc.(美國(guó)微芯科技公司)發(fā)布了用于CryptoAuthentication系列的Trust Platform(可信平臺(tái)),這是業(yè)界

2021-05-14 10:21:27 2244

2244 算法都是由開發(fā)人員使用C++語(yǔ)言原生開發(fā)的,而他們對(duì)底層FPGA硬件知之甚少或一無(wú)所知。為了支持這一重要的開發(fā)群體,Microchip Technology Inc.(美國(guó)微芯科技公司)推出了名為SmartHLS的HLS設(shè)計(jì)工作流程,成為其PolarFire FPGA系列產(chǎn)品的新成員。

2021-09-07 11:50:27 7309

7309 Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數(shù)硬連線到器件邏輯互連結(jié)構(gòu)和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應(yīng)用加速開發(fā)流程中實(shí)現(xiàn)硬件

2022-05-25 09:43:36 3450

3450 由于它是一個(gè)開放標(biāo)準(zhǔn),為 PolarFire 設(shè)備開發(fā)的代碼可以擴(kuò)展和縮減 Microchip FPGA SoC 產(chǎn)品組合以及其他 RISC-V RV64GC 目標(biāo),而無(wú)需從頭開始。

2022-06-01 10:18:56 2348

2348

在整個(gè)流程中,用戶先創(chuàng)建一個(gè)設(shè)計(jì) C、C++ 或 SystemC 源代碼,以及一個(gè)C的測(cè)試平臺(tái)。通過(guò) Vivado HLS Synthesis 運(yùn)行設(shè)計(jì),生成 RTL 設(shè)計(jì),代碼可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 8680

8680 出于這個(gè)原因,Microchip 繼續(xù)在其 PolarFire FPGA SoC 系列中進(jìn)行創(chuàng)新——推出的具有 25K 邏輯元件和硬化四核 RISC-V CPU 的 MPFS025 SoC。

2022-07-10 15:42:15 1538

1538

HLS的FPGA開發(fā)方法是只抽象出可以在C/C++環(huán)境中輕松表達(dá)的應(yīng)用部分。通過(guò)使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 2261

2261

Vitis HLS 工具能夠?qū)?C++ 和 OpenCL 功能部署到器件的邏輯結(jié)構(gòu)和 RAM/DSP 塊上。在 GitHub 上提供 Vitis HLS 前端為研究人員、開發(fā)人員和編譯器愛(ài)好者開啟了無(wú)限可能的新世界,使他們可以利用 Vitis HLS 技術(shù)并根據(jù)其應(yīng)用的特定需求進(jìn)行修改。

2022-08-03 09:53:58 1602

1602 1、HLS簡(jiǎn)介 HLS(High-Level Synthesis)高層綜合,就是將 C/C++的功能用 RTL 來(lái)實(shí)現(xiàn),將 FPGA 的組件在一個(gè)軟件環(huán)境中來(lái)開發(fā),這個(gè)模塊的功能驗(yàn)證在軟件環(huán)境中來(lái)

2022-12-02 12:30:02 7407

7407 推理解決方案的快速開發(fā)平臺(tái) 》的在線研討會(huì)。 VectorBlox平臺(tái)是一款軟件開發(fā)工具包(SDK),可實(shí)現(xiàn)基于PolarFire FPGA的機(jī)器學(xué)習(xí)(ML)推理。這款SDK有多種工具,無(wú)需對(duì)FPGA

2022-12-12 20:25:08 1322

1322 HLS ?(high-level synthesis)稱為高級(jí)綜合, 它的主要功能是用 C/C++為 FPGA開發(fā) 算法。這將提升FPGA 算法開發(fā)的生產(chǎn)力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 6467

6467 AMD Vitis HLS 工具允許用戶通過(guò)將 C/C++ 函數(shù)綜合成 RTL,輕松創(chuàng)建復(fù)雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統(tǒng)一軟件平臺(tái)(用于所有異構(gòu)系統(tǒng)設(shè)計(jì)和應(yīng)用)高度集成。

2023-04-23 10:41:01 1730

1730

。 ? 這些新工具進(jìn)一步擴(kuò)大了Microchip FPGA全面的工具和服務(wù)工具包,支持成熟的PolarFire系列器

2023-06-08 08:05:02 1234

1234 。 這些新工具進(jìn)一步擴(kuò)大了Microchip FPGA全面的工具和服務(wù)工具包,支持成熟的PolarFire系列器件

2023-06-15 09:05:01 873

873 該項(xiàng)目包含使用高級(jí)綜合 (HLS) 的 2D 中值濾波器算法的實(shí)現(xiàn)。該項(xiàng)目的目標(biāo)是在不到 3 ms的時(shí)間內(nèi)對(duì)測(cè)試圖像進(jìn)行去噪,同時(shí)消耗不到 25% 的可用 PL 資源。特征如下:

2023-07-03 09:06:43 1551

1551

安全當(dāng)前已成為各垂直市場(chǎng)所有設(shè)計(jì)的當(dāng)務(wù)之急。今天,有進(jìn)一步證據(jù)向系統(tǒng)架構(gòu)師和設(shè)計(jì)人員證明,使用Microchip Technology Inc.(美國(guó)微芯科技公司)的PolarFire FPGA

2023-09-05 11:50:01 1330

1330 Microchip推出針對(duì)智能邊緣設(shè)計(jì)的定制PolarFire FPGA和SoC解決方案堆棧,以加快開發(fā)速度,同時(shí)推動(dòng)FPGA的采用。 為了加快智能邊緣設(shè)計(jì),Microchip Technology

2023-10-26 18:09:50 2340

2340 。XilinxVivadoHLS(High-LevelSynthesis,高層次綜合)工具支持將C、C++等語(yǔ)言轉(zhuǎn)化成硬件描述語(yǔ)言,同時(shí)支持基于OpenCL等框架對(duì)Xilinx可編程邏輯器件進(jìn)行開發(fā),可

2023-01-03 15:47:38 7

7 很多人都比較反感用C/C++開發(fā)(HLS)FPGA,大家第一拒絕的理由就是耗費(fèi)資源太多。但是HLS也有自己的優(yōu)點(diǎn),除了快速構(gòu)建算法外,還有一個(gè)就是接口的生成,尤其對(duì)于AXI類接口,按照標(biāo)準(zhǔn)語(yǔ)法就可以很方便地生成相關(guān)接口。

2024-07-16 18:01:03 1940

1940

電子發(fā)燒友網(wǎng)站提供《使用航天級(jí)電源元件為Microchip RT PolarFire FPGA供電.pdf》資料免費(fèi)下載

2024-09-02 10:56:54 0

0 和靈感。 以下是本周新品情報(bào),請(qǐng)及時(shí)查收: 嵌入式系統(tǒng)快速開發(fā) ? Microchip Technology PolarFire SoC Discovery套件 ? 貿(mào)澤電子即日起

2024-10-17 14:36:35 1408

1408

Microchip Technology推出了PolarFire? FPGA以太網(wǎng)傳感器橋,以幫助開發(fā)人員創(chuàng)建與NVIDIA Holoscan傳感器處理平臺(tái)兼容的人工智能(AI)驅(qū)動(dòng)的傳感器處理系統(tǒng)

2024-11-19 09:29:16 1724

1724 為了幫助開發(fā)人員構(gòu)建人工智能(AI)驅(qū)動(dòng)的傳感器處理系統(tǒng),Microchip Technology Inc.(微芯科技公司)發(fā)布了支持NVIDIA Holoscan 傳感器處理平臺(tái)的PolarFire FPGA 以太網(wǎng)傳感器橋接器。

2024-11-25 16:43:16 1457

1457 在 2025 國(guó)際嵌入式展(Embedded World 2025)上,全球 FPGA 創(chuàng)新技術(shù)領(lǐng)導(dǎo)者 Altera 發(fā)布了專為嵌入式開發(fā)者打造的最新可編程解決方案,以進(jìn)一步突破智能邊緣領(lǐng)域的創(chuàng)新

2025-03-12 09:47:29 2400

2400 ? ? ? ? ? ? ? ? ? ? ? ? Microchip PolarFire?? SoC FPGA通過(guò)?? AEC-Q100汽車級(jí)認(rèn)證? ? ? ? Microchip

2025-03-31 19:26:56 2181

2181 當(dāng)前市場(chǎng)中,物料清單(BOM)成本持續(xù)攀升,開發(fā)者需在性能和預(yù)算間實(shí)現(xiàn)優(yōu)化。鑒于中端FPGA市場(chǎng)很大一部分無(wú)需集成串行收發(fā)器,Microchip Technology Inc.(微芯科技公司)正式發(fā)布PolarFire Core現(xiàn)場(chǎng)可編程門陣列(FPGA)和片上系統(tǒng)(SoC)。

2025-05-23 14:02:15 1369

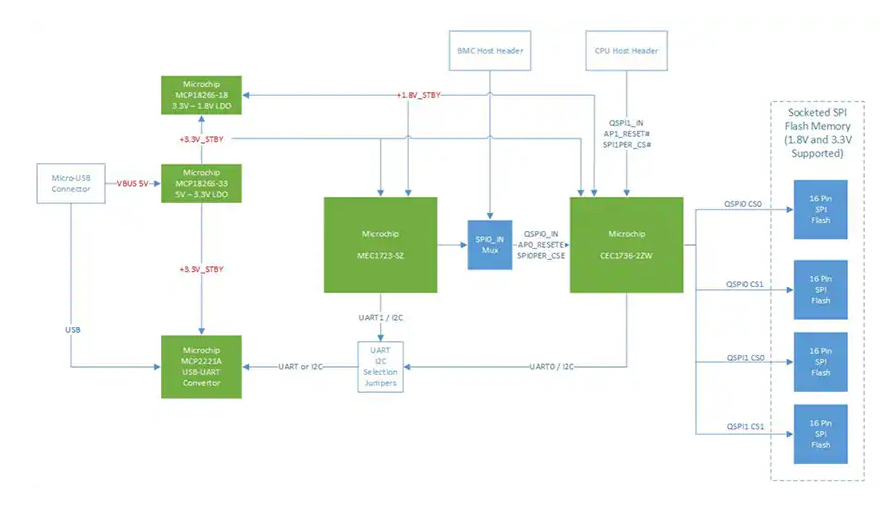

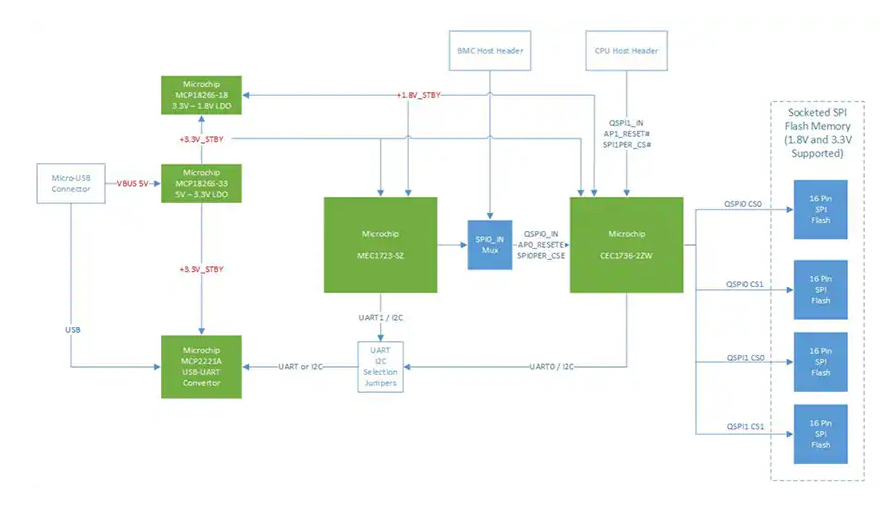

1369 Microchip Technology CEC173x評(píng)估套件 (EV42J24A) 是用于CEC173x可信擴(kuò)展板系列平臺(tái)信任根控制器的評(píng)估和開發(fā)套件。該板與TPDS(信任平臺(tái)設(shè)計(jì)套件)工具配合

2025-09-29 14:55:33 638

638

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論