當我們安裝好Vivado 的時候,也同時裝好了Vivado HLS.。 這是個什么東西?我就有一種想一探究的感覺。網上一查,Vivado High-Level Synthesis。學習了一段時間的Zynq 7000, 找了一個HLS的教程,就開始了如下入門實驗,體驗高級語言綜合設計IP。Vivado HLS是Xilinx 推出的高層次綜合工具,采用C/C++語言進行FPGA設計。HLS提供了一些樣例方便大家熟悉其開發流程。另外關于HLS的使用介紹,Xilinx官方提供了2個重要開發文檔ug871 和 ug902。里面詳細介紹了包括怎么建立HLS 工程,怎么編寫Testbench,怎么進行優化等問題。在HLS軟件界面,在右側有個directive, 里面列出了程序中所有用到的變量,函數和循環結構,點右鍵可以給其配置。

對循環結構, 一般選擇 unroll( 即展開循環) , 可以自己設定展開因子 factor。 為提高程序的并行化處理, 可以給函數選擇 PIPELINE。 對應數組, 可以設置為 ARRAY_PARTITION,數組維數可以自己設定。 HLS 軟件其實很智能的, 簡單的結構, 一般軟件自己會優化好。 每一個優化方案都保存在一個 Solution 里, HLS 可以創建多個 Solution, 用于比較不用的優化效果。

如同軟件開發都是從“ Hello Wrold! ” 進入編程的大門一樣, 這一個實驗我們就通過 HLS 封裝一個移位流水燈的程序, 包括工程的創建, 仿真, 綜合, 封裝, 以及在硬件平臺上的實現,來熟悉HLS的開發流程。

本文參考了米聯的zynq 修煉秘籍 網手版。

實驗代碼和工程的下載:

鏈接: http://pan.baidu.com/s/1c1BXkvm 密碼:h2i2

1:HLS工程建立

打開 Vivado HLS 開發工具, 單擊 Creat New Project 創建一個新工程, 設置好工程路

徑和工程名, 一直點擊 Next 按照默認設置,

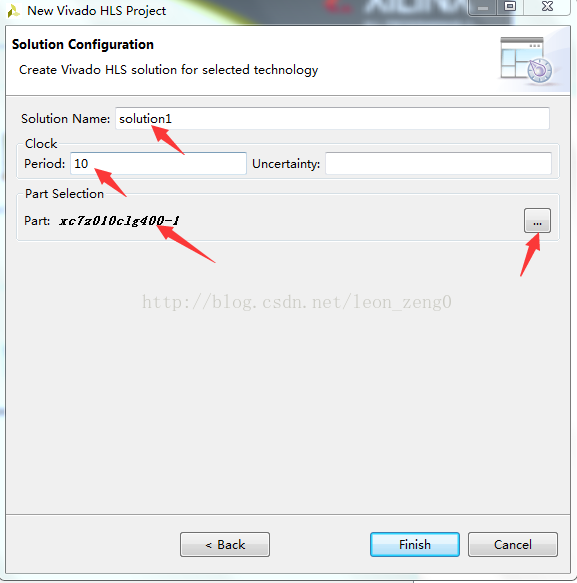

出現如下圖所示界面,時鐘周期 Clock Period 按照默認 10ns,Uncertaintly 和 Solution

Name 均按照默認設置, 點擊紅色圓圈部分選擇芯片類型, 然后點擊 OK。下圖示是選擇好后的界面。

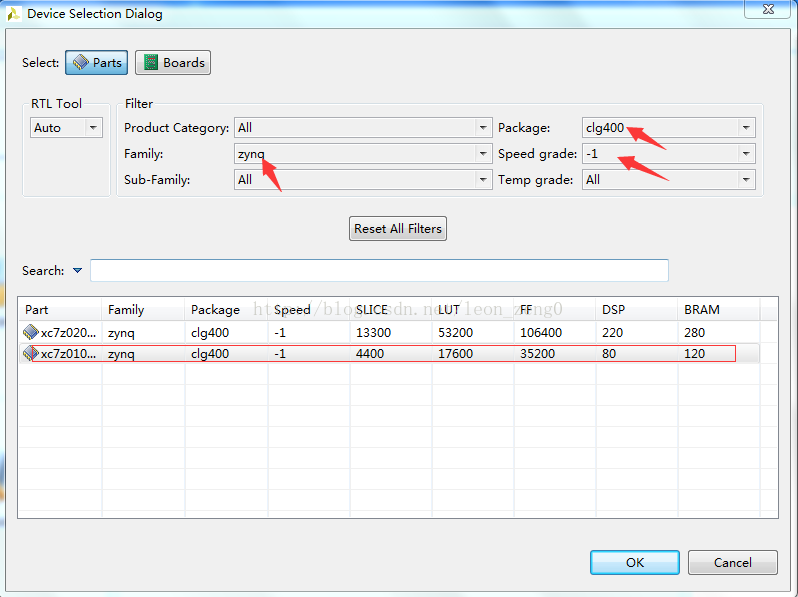

下面是選擇芯片型號的界面。根據你自己的硬件選擇,我的是如圖

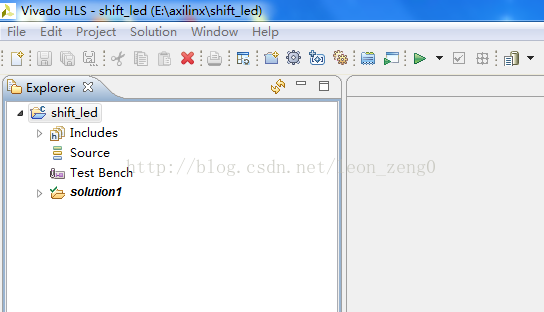

工程建立完后的界面是這樣的。下面就是導入工程里用到的源文件。

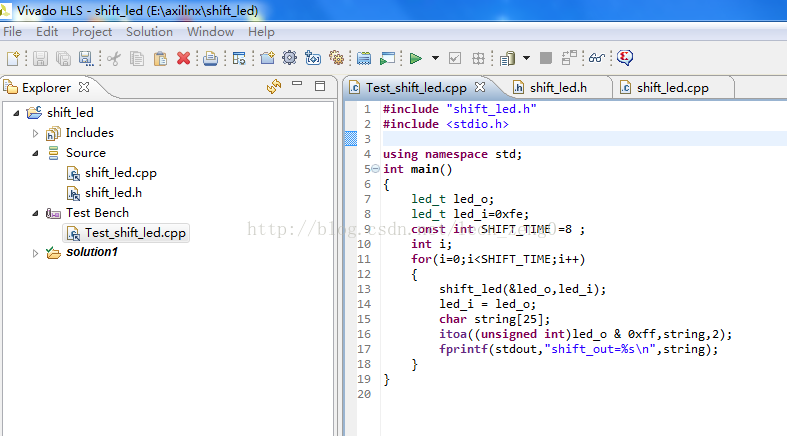

需要在工程添加3個源文件。都可以在文件開頭介紹的下載地址下載。右鍵點擊source , Add Files 分別添加shift_led.cpp 和 shift_led.h。 右鍵點擊Test Bench , Add Files 添加Test_shift_led.cpp.

添加完成后效果如下:

shift_led.h 代碼內容:

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

//

#include "ap_int.h"

//#define MAX_CNT 10000/2 //仿真時可以用這個代替下面的行介紹仿真等待時間

#define MAX_CNT 100000000/2

#define SHIFT_FLAG MAX_CNT-2

//typedef int led_t;

typedef ap_fixed led_t; // 1st: total width. 2nd: integer width

void shift_led(led_t *led_o,led_t led_i);

#endif

shift_led.cpp 代碼內容:

#include "shift_led.h"

void shift_led(led_t *led_o,led_t led_i)

{

led_t tmp_led=led_i;

int i; //for cycle variables

for(i = 0;i {

if(i==SHIFT_FLAG)

{

//tmp_led = ((tmp_led>>7)&0x01) + ((tmp_led tmp_led = ((tmp_led>>4)&0x01) + ((tmp_led *led_o = tmp_led;

}

}

}

Test_shift.led.cpp 代碼內容:

#include "shift_led.h"

#include

using namespace std;

int main()

{

led_t led_o;

led_t led_i=0xfe;

const int SHIFT_TIME =8 ;

int i;

for(i=0;i

shift_led(&led_o,led_i);

led_i = led_o;

char string[25];

itoa((unsigned int)led_o & 0xf,string,2);

fprintf(stdout,"shift_out=%s/n",string);

}

}

2:工程綜合

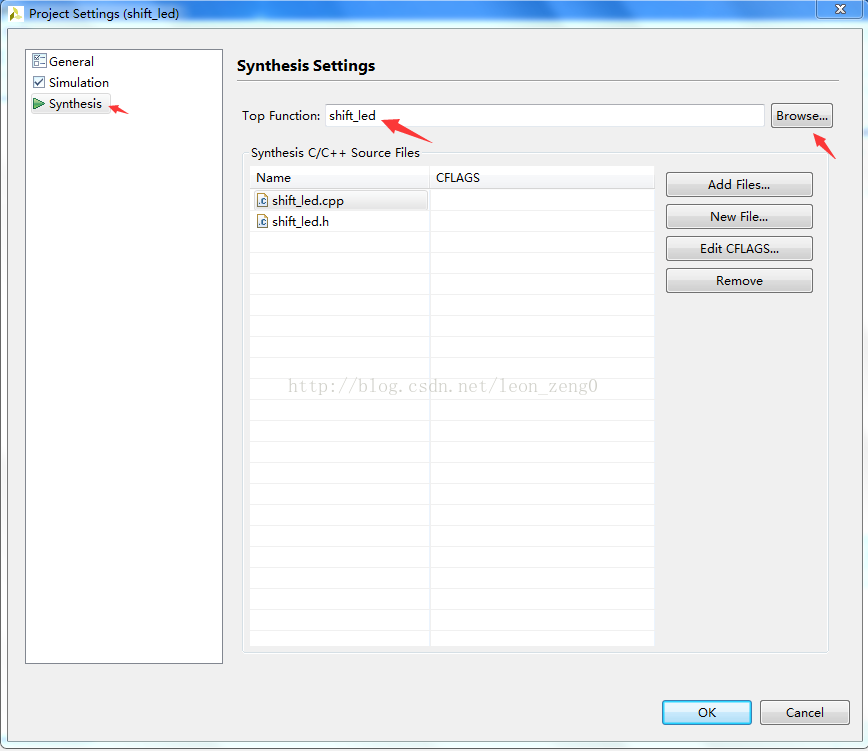

工程綜合前,需要設置 Top Function。

點擊 Project-> Project Settings ,也可以點擊紅箭所指那樣的快捷鍵。

出現如下界面 ,在Syntheses 界面下選擇綜合的頂層函數名。

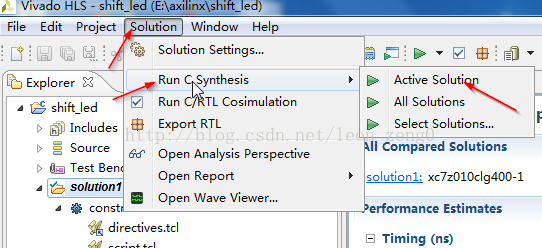

因為當前工程中只存在一個Solution, 我們選擇Solution ->Run C Sytheses -> Active Solutions 進行綜合,菜單旁有個快捷鍵的圖標,所以也有快捷可以直接點取:

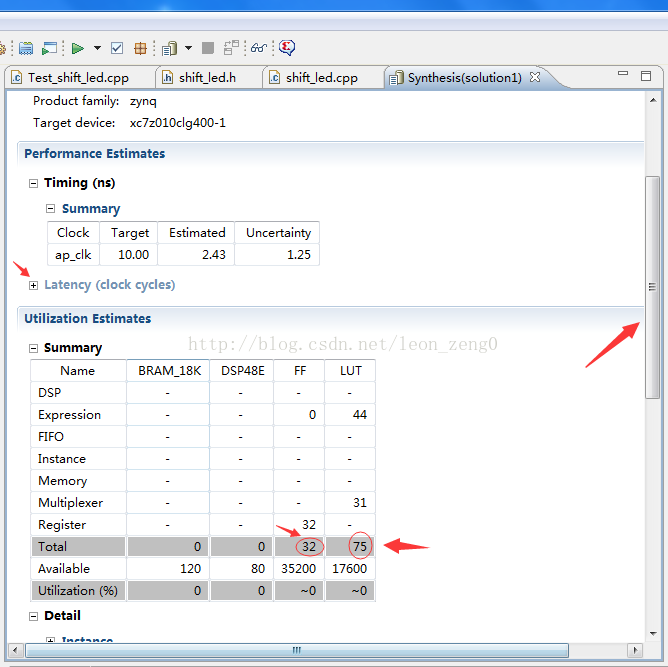

在未經優化的情況下綜合報告如圖所示, 出現這個界面需要把上下條拉到合適位置, 并收起Latency (Clock cycles)。

3: 優化和添加約束

在原文中, led_t tmp_led=led_i; 最開始是int , 然后把他定義為4位整數。我這里一開始就是這樣,也就沒有什么優化了。

但這里做一下他的約束添加,或者也是優化的內容。

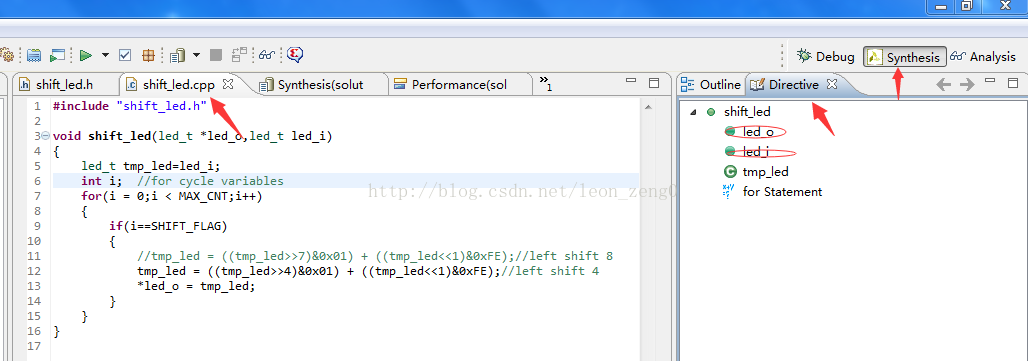

在主頁面里,點擊如下3出紅箭,如果不是這個界面。選擇文件 shift_led.cpp 文件, 選擇 synthesis, 選擇 directive。

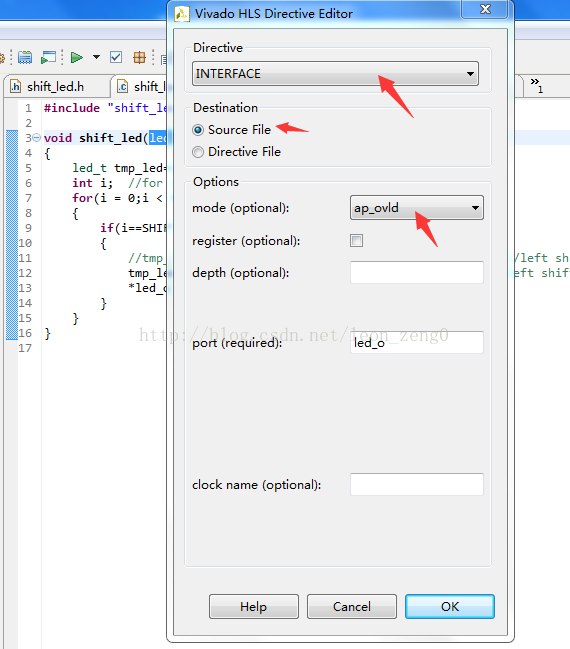

這里把led_o 設置為輸出,右鍵點擊led_o 出現Insert Drrective.. ,選擇后如下界面:

選擇 INTERFACE mode 選擇 ap_ovld。

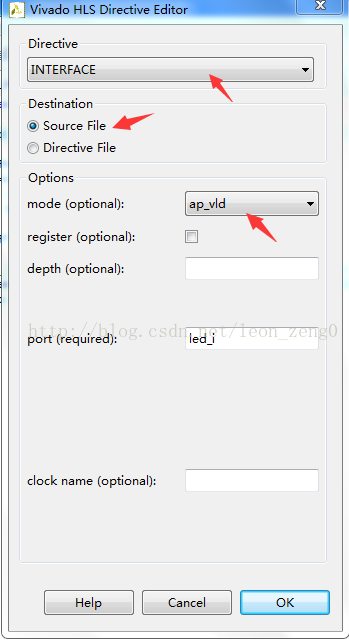

同樣對led_i 進行基本相同的工作,mode 選擇 ap_vld。

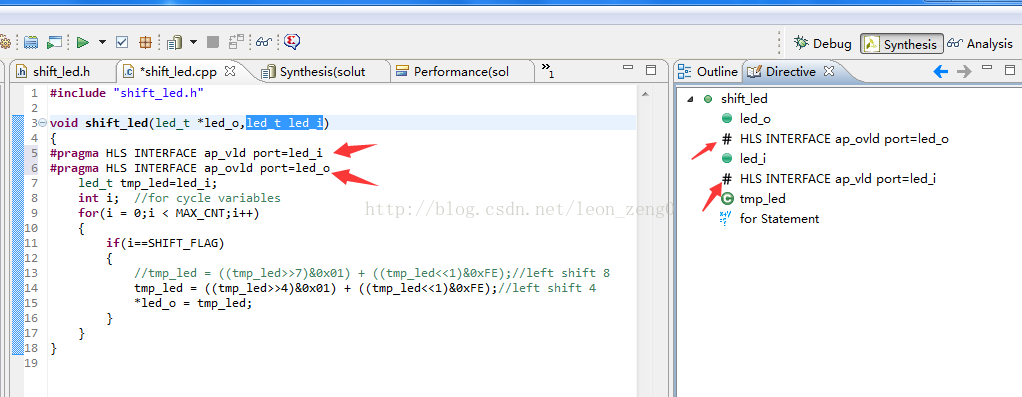

進行如上操作后,看看源程序出現的變化。還有Directive 的變化。

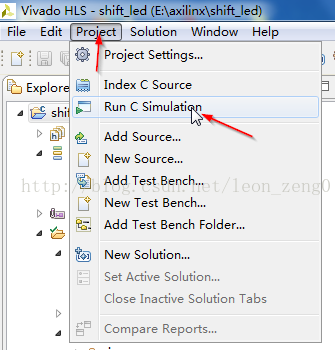

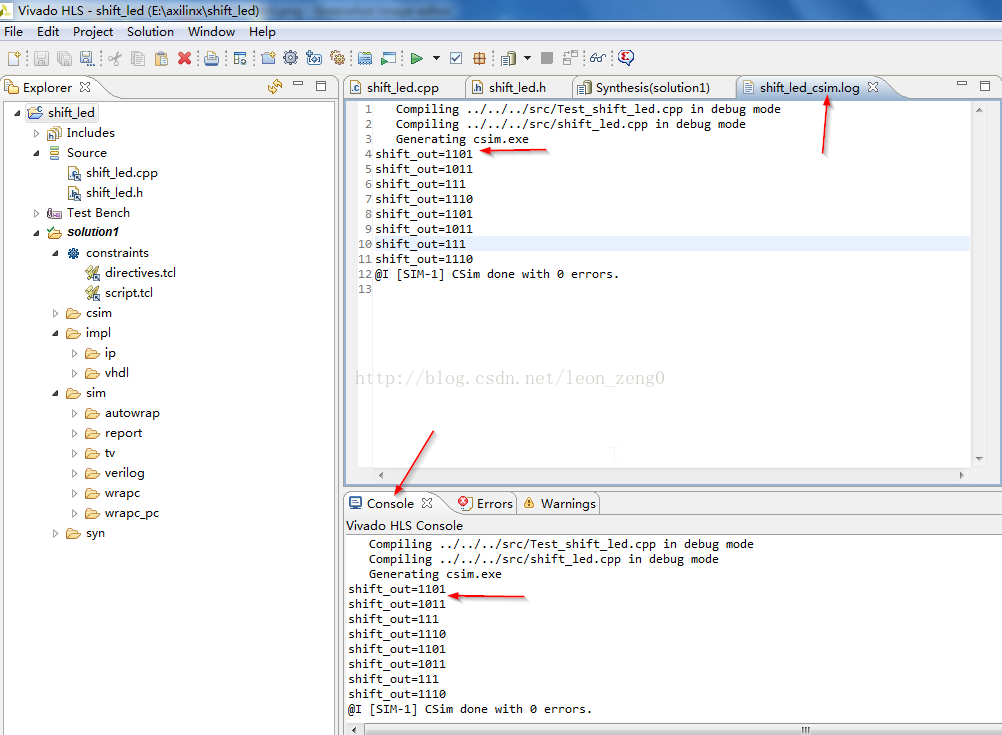

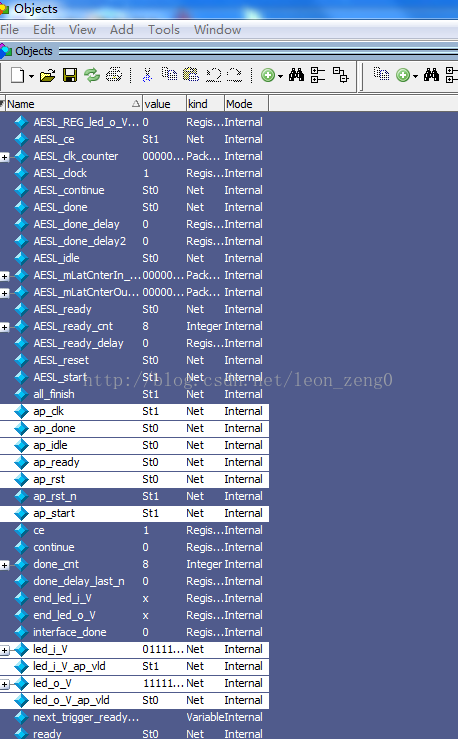

仿真運行的情況是這樣的:

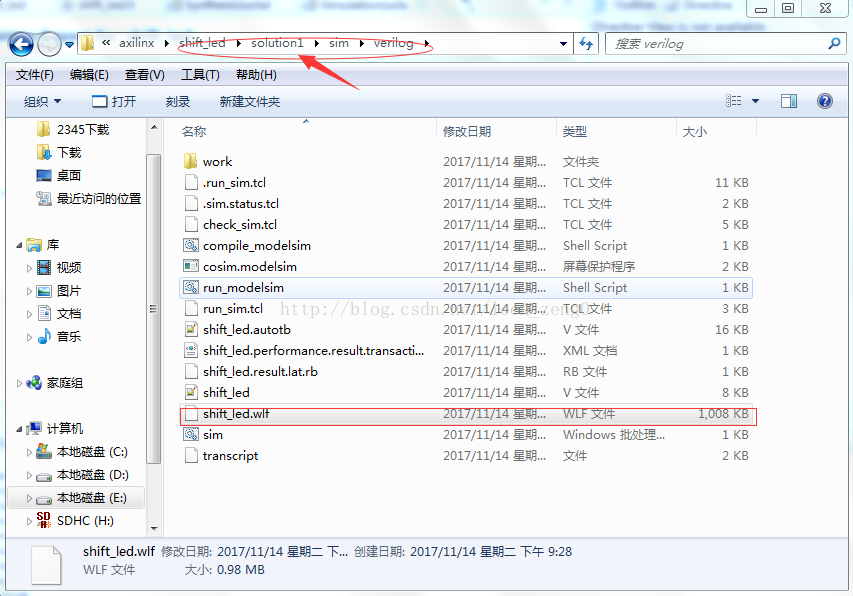

4:波形仿真(如果不熟悉ModelSim 就跳過這一節):

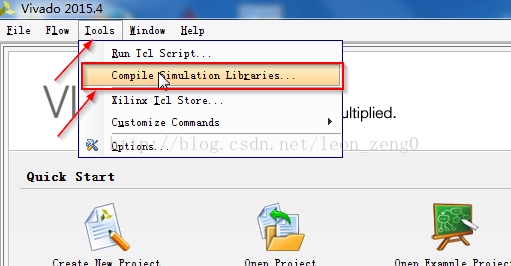

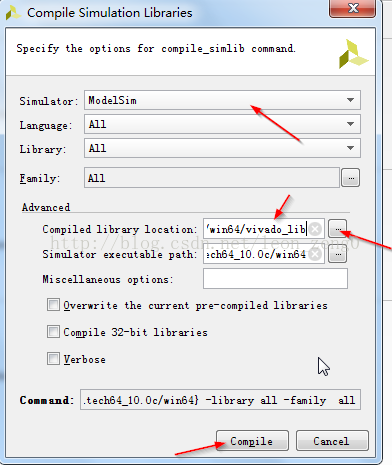

在這之前需要運行Vivado 的編譯仿真庫,我是開始這個試驗前就做了這個設置。

打開Vivado 后,菜單 Tools -> Compile Simulation Libraries...

出現對話框后,選擇Simulator 為 ModelSim, 選擇編譯庫的位置,看紅箭。

做好設置后, 點擊Compile 就開始生成仿真庫。

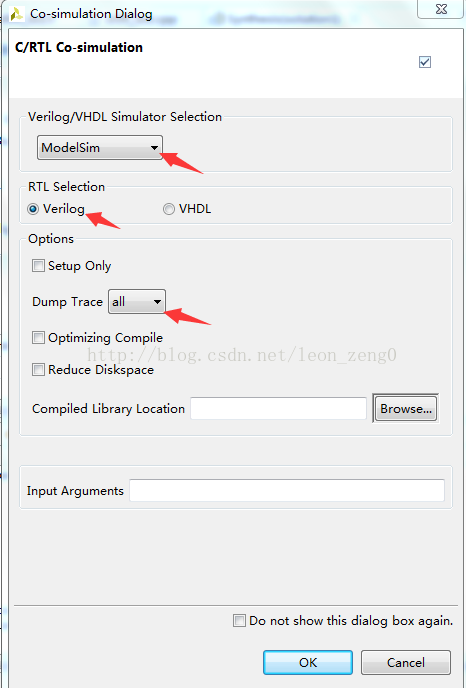

如果做好了上面的仿真庫編譯準備,就可以開始看波形仿真了。

菜單Solution -> Run C/RTL Cosimulation 運行C協同仿真。做了如圖所示選擇。

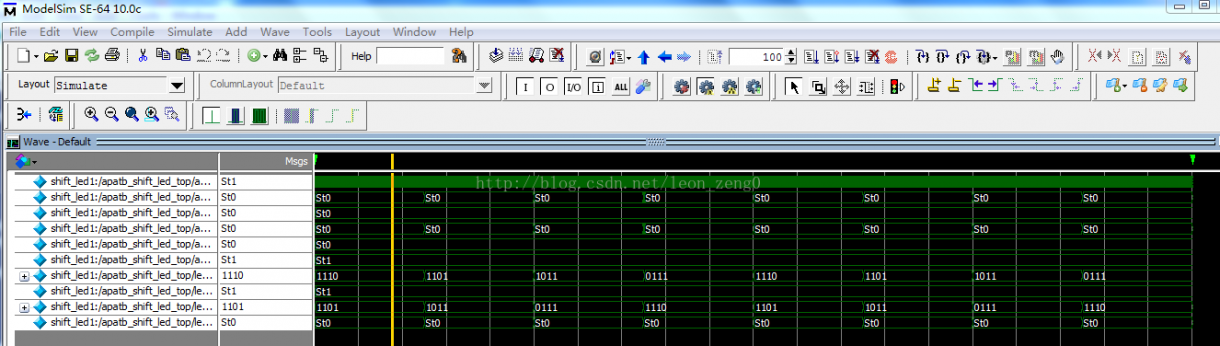

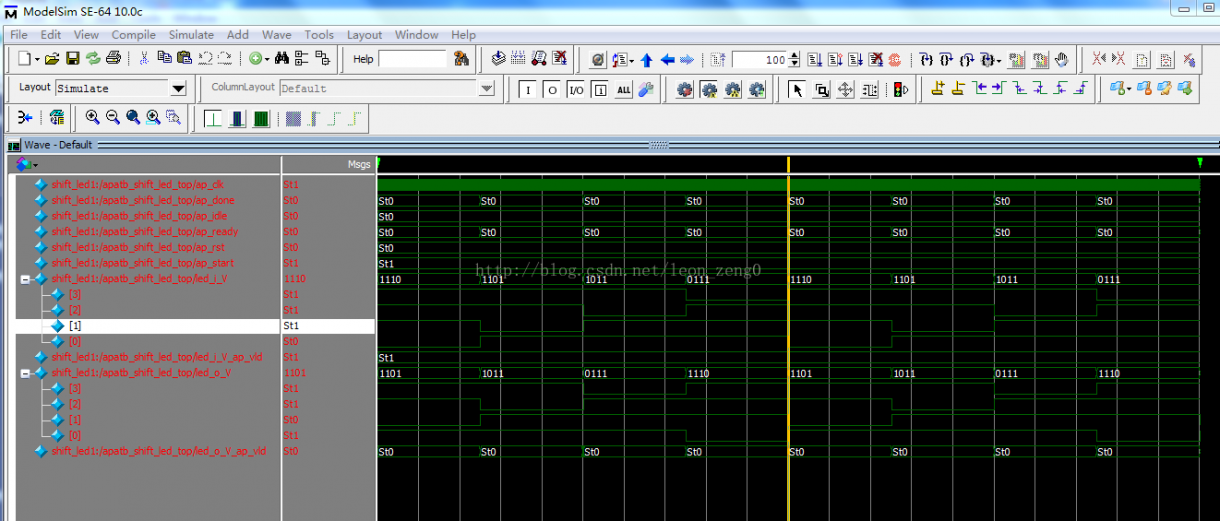

波形顯示就是這樣的。

這就是波形仿真。

5: HLS代碼封裝

通過前面的實驗,我們進行了HLS的工程創建,仿真,但這只是把算法實現從C 到RTL的轉換。下面我們開始把其打包成IP, 在硬件平臺上進行測試,也方便Vivado 進行調用,應用。

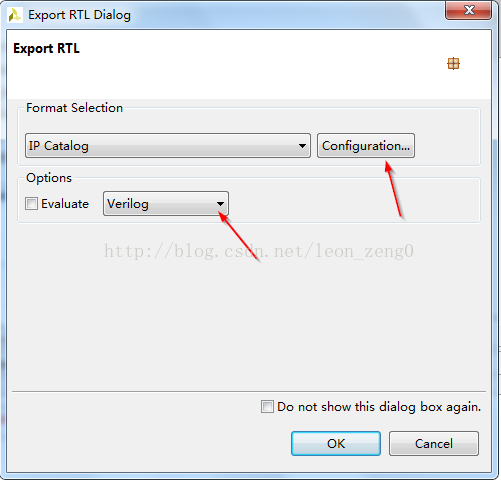

菜單 Solution -> Export RTL 也可以點快捷(菜單圖示)。

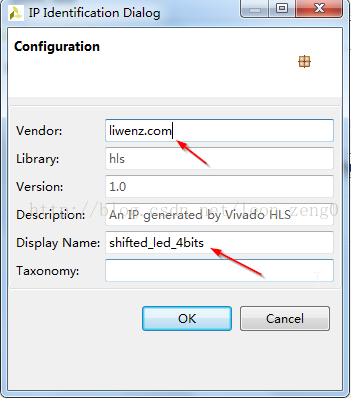

在彈出的對話框中,點擊Configuration 對一些參數進行輸入,修改,然后點擊OK。

Configuration 的對話框設置。

點擊2次OK 之后,就開始IP 打包封裝。

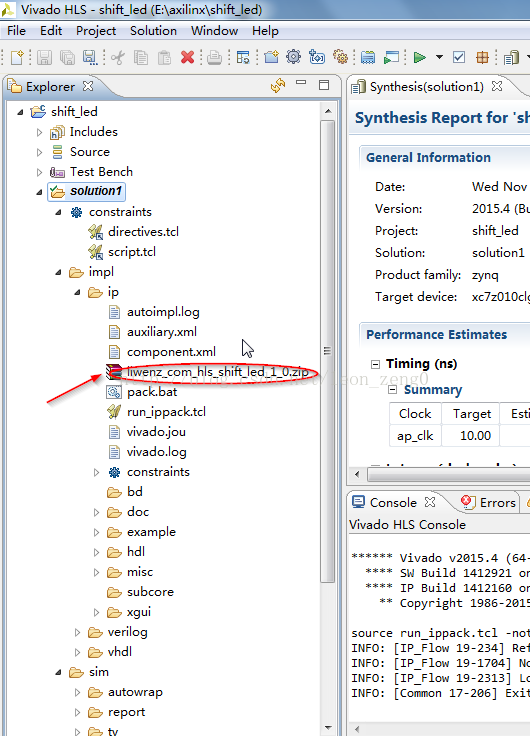

運行結束后,就在solution1 目錄下多了一個impl 文件夾,并且在0等待一段時間后在 solution1 目錄下多了一個 impl 文件夾, 并且在ip 文件夾中生成了一個壓縮包,這就是我們需要的打包好的IP。

6 測試和應用:

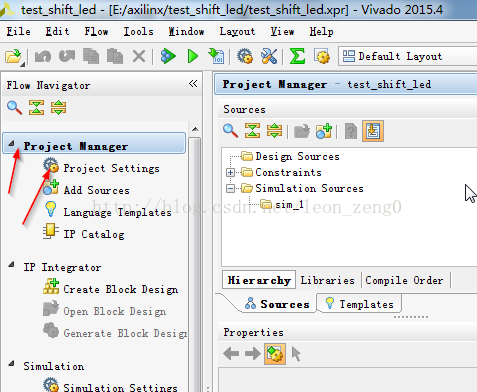

打開Vivado, 新建一個工程,工程名為test_shift_led。

在Project Manager 中點擊 Project Settings。

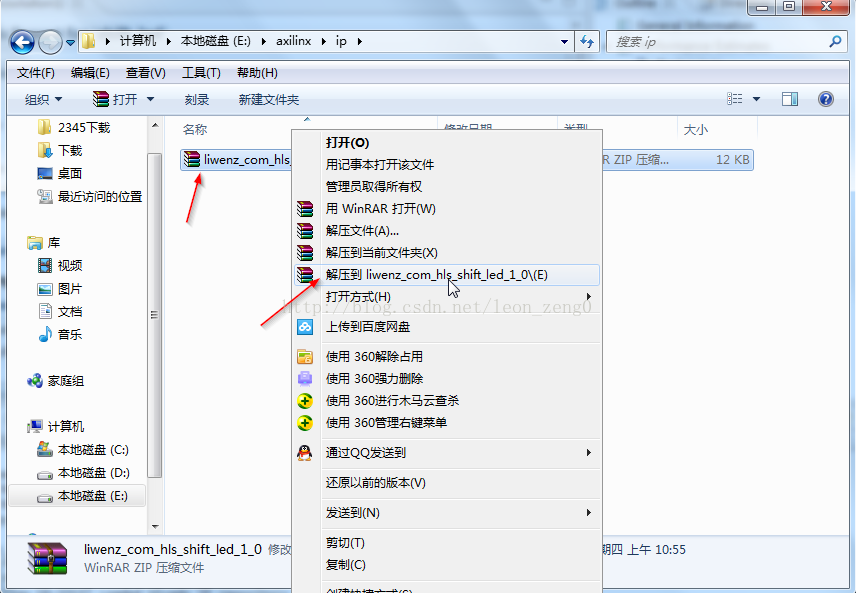

在這解壓剛才建立的IP 壓縮包到一個新建的文件夾里,這是在文件管理器里完成的。

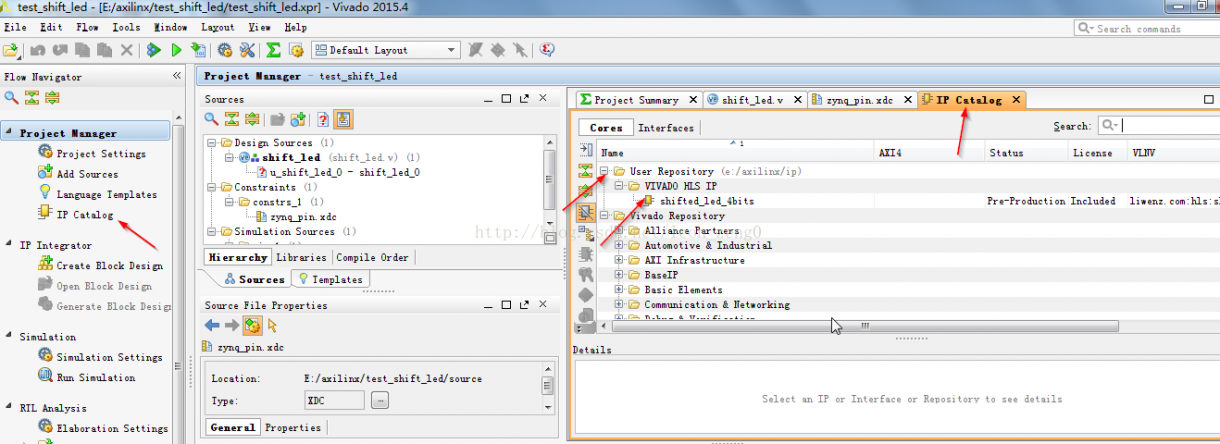

選擇IP 設置區的 Repository Manager 頁面,然后點擊+號, 下面圖示是添加后的結果。

進行了以上設置后,開始添加我們的IP包。

點擊Project Manager 下的IP Catalog 。 在右邊的IP Catalog 里點開User Repository,然后選擇我們建立的IP, 顯示的是shifted_led_4bits。這和我們添加其他的ip 是一樣的。

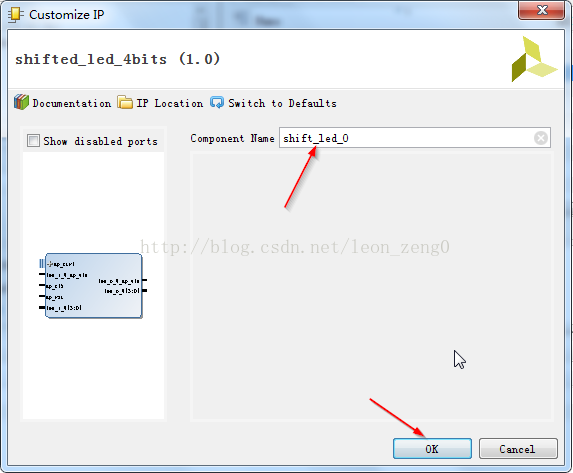

可以設置下IP, 名字為shift_led_0

在這個對話框里選擇Generate

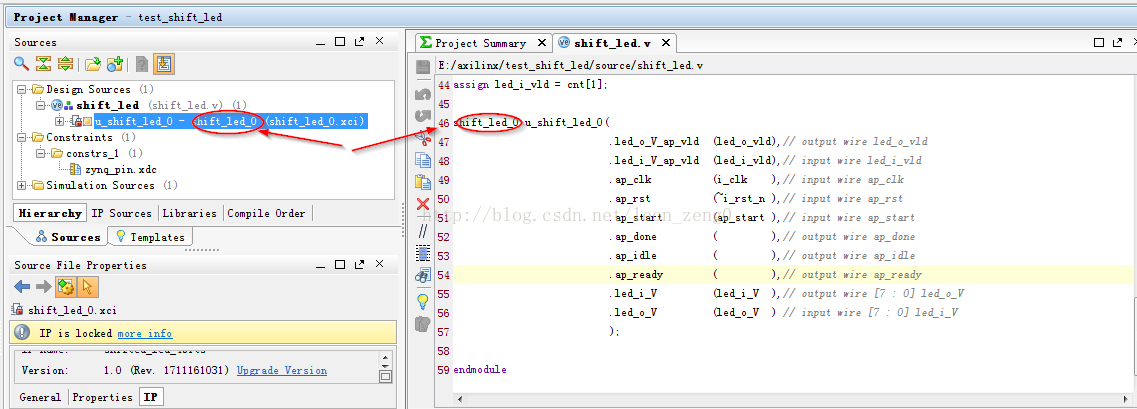

現在右鍵 Design Sources ,添加shift_led.v 文件,可以在下載鏈接出獲取。右鍵Constraints,添加led

的約束文件。特別注意這個約束文件必須和你硬件的led 引腳定義一致。

看看下圖,ip取名和程序中必須一致,就是左邊和右邊。

shift_led.v 的代碼如下(如果不想下載,也可以復制):

`timescale 1ns / 1ps

module shift_led

#(

parameter DATA_WIDTH = 4

)

(

input i_clk,

input i_rst_n,

output reg [DATA_WIDTH-1:0] led

);

reg [1:0] cnt ;

reg [DATA_WIDTH-1:0] led_i_V ;

wire ap_start ;

wire led_i_vld;

wire [DATA_WIDTH-1:0] led_o_V ;

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

cnt else if(cnt[1]==1'b0)

cnt end

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

led_i_V else if(cnt[0]==1'b1)

led_i_V else if(led_o_vld == 1'b1)

led_i_V end

always@(posedge i_clk or negedge i_rst_n)begin

if(i_rst_n == 1'b0)

led else if(led_o_vld == 1'b1)

led end

assign ap_start = cnt[1];

assign led_i_vld = cnt[1];

shift_led_0 u_shift_led_0(

.led_o_V_ap_vld (led_o_vld),// output wire led_o_vld

.led_i_V_ap_vld (led_i_vld),// input wire led_i_vld

.ap_clk (i_clk ),// input wire ap_clk

.ap_rst (~i_rst_n ),// input wire ap_rst

.ap_start (ap_start ),// input wire ap_start

.ap_done ( ),// output wire ap_done

.ap_idle ( ),// output wire ap_idle

.ap_ready ( ),// output wire ap_ready

.led_i_V (led_i_V ),// output wire [7 : 0] led_o_V

.led_o_V (led_o_V ) // input wire [7 : 0] led_i_V

);

endmodule

zynq.xdc 文件內容如下:

set_property IOSTANDARD LVCMOS33 [get_ports i_clk]

set_property IOSTANDARD LVCMOS33 [get_ports i_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN M14 [get_ports {led[0]}]

set_property PACKAGE_PIN M15 [get_ports {led[1]}]

set_property PACKAGE_PIN K16 [get_ports {led[2]}]

set_property PACKAGE_PIN R19 [get_ports {led[3]}]

set_property PACKAGE_PIN U18 [get_ports i_clk]

set_property PACKAGE_PIN R18 [get_ports i_rst_n]

下面就和你硬件板提供的 FPGA led 實驗程序一樣了。綜合,執行,生成流文件,下載運行。

你的led 應該流水運行了。

-

FPGA設計

+關注

關注

9文章

431瀏覽量

28143 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131149 -

C++

+關注

關注

22文章

2124瀏覽量

77124 -

Vivado

+關注

關注

19文章

857瀏覽量

71118

發布評論請先 登錄

HLS設計中的BRAM使用優勢

**CW32L012****開發評估板的第一個程序**

第4章 C語言基礎以及流水燈的實現(4.7 4.8)

蜂鳥E203在黑金XC7A200T型FPGA上點亮LED并實現流水燈

一文讀懂:W55MH32 如何攜手微信小程序與 OneNET,實現以太網燈條調色自由(軟硬件開源)

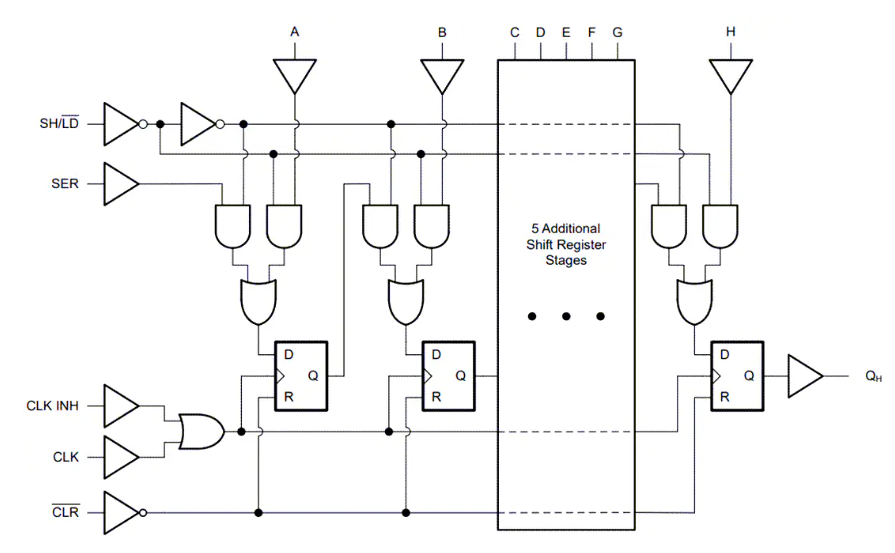

Texas Instruments SN74LVC166A 8位并聯負載移位寄存器數據手冊

【沁恒CH585開發板免費試用體驗】GPIO 流水燈

如何在Unified IDE中創建視覺庫HLS組件

使用AMD Vitis Unified IDE創建HLS組件

【RA-Eco-RA4M2開發板評測】點燈實現6種LED花式流水燈操作

【RA-Eco-RA4M2開發板評測】2 初識GPIO流水燈

Vivado HLS設計流程

通過HLS封裝一個移位流水燈的程序案例

通過HLS封裝一個移位流水燈的程序案例

評論