由于邊緣計算應用需要綜合考慮性能與低功耗,因此帶動了開發人員將現場可編程門陣列(FPGA)用作高能效加速器的需求,這種做法還能夠提供靈活性和加快上市時間。然而,大部分邊緣計算、計算機視覺和工業控制算法都是由開發人員使用C++語言原生開發的,而他們對底層FPGA硬件知之甚少或一無所知。為了支持這一重要的開發群體,Microchip Technology Inc.(美國微芯科技公司)推出了名為SmartHLS的HLS設計工作流程,成為其PolarFire FPGA系列產品的新成員。SmartHLS可以將C++算法直接轉換為FPGA優化的寄存器傳輸級(RTL)代碼,從而極大提升了生產力和設計的便利性。

Microchip FPGA業務部副總裁Bruce Weyer表示:“SmartHLS增強了Microchip的Libero SoC設計工具套件的功能,使屢獲殊榮的中等帶寬PolarFire和PolarFire SoC平臺的巨大優勢能夠被不同的算法開發者群體所利用,而無需成為FPGA硬件專家。結合Microchip的VectorBlox神經網絡軟件開發工具包,新套件將大大提高設計人員的工作效率,可使用基于C/C++算法并利用基于FPGA的硬件加速器,為嵌入式視覺、機器學習、電機控制和工業自動化等應用開發尖端解決方案。”

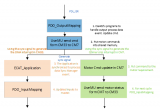

基于開源Eclipse集成開發環境,SmartHLS設計套件使用C++軟件代碼生成HDL IP組件,以集成到Microchip的Libero SmartDesign項目中。這使工程師能夠在比傳統FPGA RTL工具更高的抽象層次上描述硬件行為。與其他HLS產品相比,它通過多線程應用編程接口(API)并發執行硬件指令,并簡化復雜硬件并行性的表達,在減少開發時間的同時進一步提高生產力。

SmartHLS工具所需的代碼行數是同等RTL設計的十分之一,而且由此產生的代碼更容易閱讀、理解、測試、調試和驗證。該工具還簡化了對硬件微架構設計的取舍,并使開發人員能將已有的C++軟件用于PolarFire FPGA和FPGA SoC。

責任編輯:haq

-

加速器

+關注

關注

2文章

839瀏覽量

40097 -

microchip

+關注

關注

53文章

1639瀏覽量

120899 -

C++

+關注

關注

22文章

2123瀏覽量

77110

原文標題:Microchip發布智能高級合成(HLS)工具套件,助力客戶使用PolarFire? FPGA平臺進行基于C++的算法開發

文章出處:【微信號:MicrochipTechnology,微信公眾號:Microchip微芯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

是德科技與三星攜手英偉達展示端到端AI-RAN驗證工作流程

虛幻引擎5在建筑可視化中的應用:趨勢、挑戰與基于Perforce P4的工作流程

一張圖看懂遠動通信裝置的工作流程

芯片ATE測試詳解:揭秘芯片測試機臺的工作流程

Microchip推出模型語境協議(MCP)服務器,助力AI驅動的產品數據訪問

強強合作 西門子與日月光合作開發 VIPack 先進封裝平臺工作流程

ADI Power Studio工作流程與工具概述

恩智浦i.MX RT1180跨界MCU驅動EtherCAT的工作流程

如何在Unified IDE中創建視覺庫HLS組件

新思科技攜手是德科技推出AI驅動的射頻設計遷移流程

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

Princetel 推出新的手動電纜卷筒在線配置器

Vivado HLS設計流程

Microchip推出HLS設計工作流程

Microchip推出HLS設計工作流程

評論