經(jīng)常涉及對寬帶模擬信號進(jìn)行數(shù)據(jù)采集和存儲,以便計算機進(jìn)一步進(jìn)行數(shù)據(jù)處理。為了對高速模擬信號進(jìn)行不失真采集,根據(jù)奈奎斯特定理, 采樣頻率必須為信號頻率的2 倍以上,但在電阻抗多頻及參數(shù)成像技術(shù)中正

2023-09-15 09:45:01 3841

3841

1、 應(yīng)用背景

基于ARM+FPGA的高速同步數(shù)據(jù)采集方案,解決了數(shù)據(jù)采集的同步性問題,與以往

2010-07-22 16:36:17 1633

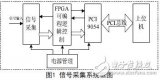

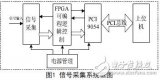

1633 為解決現(xiàn)場測試系統(tǒng)中微弱信號的高速實時采集處理和及時可靠存儲的問題,本文提出了基于PCI總線的數(shù)據(jù)采集電路的設(shè)計方案,該方案將模擬信號通過高速A/D芯片有效采樣,在FPGA的控制下將數(shù)據(jù)上傳到PC機

2014-01-24 09:45:29 4027

4027

隨著現(xiàn)代檢測技術(shù)和科技水平的高速發(fā)展,信號采集技術(shù)的應(yīng)用范圍越來越廣泛[1]。與此同時,對信號采集系統(tǒng)的采集精度、采樣率以及便攜性等設(shè)計需求提出了更高的要求。現(xiàn)場可編程門陣列(FPGA)具有邏輯門

2020-01-26 16:58:00 2987

2987

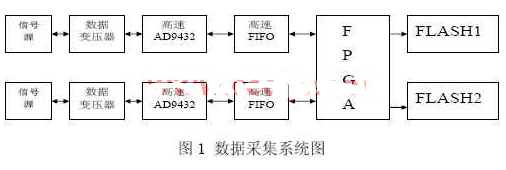

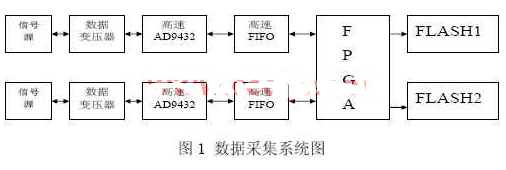

的領(lǐng)域。目前由于數(shù)字信號的快速發(fā)展,對信號采集的要求也不斷的提高,特別是在參數(shù)方面的要求越來越高,如精度、速度、采樣通道數(shù)等。鑒于此,本文會介紹一種基于FPGA來控制高速A/D轉(zhuǎn)換器AD9432實現(xiàn)高速采集,從而滿足在系統(tǒng)中的應(yīng)用。

2020-07-30 17:53:31 3597

3597

,基于Xilinx 6系列FPGA實現(xiàn)。集成了豐富的對外高速和低速接口。系統(tǒng)由CPU子系統(tǒng)、數(shù)據(jù)采集(DAQ子系統(tǒng)、高速存儲(Storage)子系統(tǒng)和數(shù)據(jù)回放(loopback)子系統(tǒng)構(gòu)成,具有配置靈活

2016-07-25 11:35:43

E30-M系列/E32-M系列的產(chǎn)品有哪些?有什么優(yōu)勢?

2022-03-02 07:19:01

門陣列實現(xiàn)1bit 的RAM時一般需要4 個門,因此 ESB/BARM 做RAM使用時,1bit 等效 4 個門,對Altera FPGA 中一個2048bit的ESB ,等效門數(shù)為8K。光靠這些數(shù)據(jù)還不

2012-08-11 10:29:07

RAM Bits 327,680Maximum Macrocells2,560Maximum I/O Pins 716圖1 EP20K 系列的等效門數(shù)下面以EP20K1000E 為例詳細(xì)說明FPGA

2012-03-01 10:08:53

的EZ-USB FX2系列智能USB接口芯片。其作用是將主機所發(fā)送的命令序列經(jīng)USB2.0端口輸出,實現(xiàn)對數(shù)據(jù)采集系統(tǒng)的控制;同時把A/D轉(zhuǎn)換器采集的數(shù)據(jù)以高速的數(shù)據(jù)序列形式發(fā)送到主機。其中,USB2.0端口

2020-01-07 07:00:00

比較器將網(wǎng)線傳輸過來的差分信號轉(zhuǎn)為單端信號,該信號時鐘頻率為100M,電平標(biāo)準(zhǔn)能滿足FPGA的輸入電平標(biāo)準(zhǔn),波形質(zhì)量尚可。單端信號直接連接到FPGA,現(xiàn)在如果想用FPGA直接采集,應(yīng)該怎么處理呢,是當(dāng)作異步信號直接打拍嗎,過采樣的話時鐘頻率不夠。時鐘恢復(fù)目前來不及實現(xiàn)。

2020-03-07 16:01:37

JESD204B協(xié)議ADC多片多通道之間采樣點相對時延固定,從而確保各通道采集信號相位一致。JESD204B協(xié)議支持的確定性延遲特性保證了設(shè)計實現(xiàn)。驗證方案的測試電路采用XilinxK7系列FPGA控制

2019-12-03 17:32:13

。JESD204B協(xié)議支持的確定性延遲特性保證了設(shè)計實現(xiàn)。驗證方案的測試電路采用XilinxK7系列FPGA控制兩片AD9694(采樣率320Msps)同步采集,證實設(shè)計方案滿足應(yīng)用需求。3、雷達(dá)

2019-12-04 10:11:26

采用的高速AD:PXIe-5114 PXI示波器,高速DA:PXIe-5413 PXI波形發(fā)生器,跪求實現(xiàn)高速DA采樣和AD的例程。

2018-08-21 16:19:19

各種高速AD采集卡大體硬件功能相同時,使用不同的FPGA 時,如V5和V6系列,單就高速AD采集卡的邏輯和性能來說,帶來一些差異。通過簡單對比北京坤馳科技有限公司的使用了交織采樣技術(shù)的高性能同系列

2016-03-10 14:10:43

。 3、海量緩存的設(shè)計實現(xiàn) 本系統(tǒng)使用了兩片256k16bit容量的SRAM作為高速緩存,系統(tǒng)中的4個通道可同時存儲每通道128k點采樣數(shù)據(jù)。在25MHz的采樣頻率下,一次可采集存儲5ms多的波形

2020-12-04 15:59:14

ADC采樣遇到了問題,采集的信號值是逐漸連續(xù)減小的。我采樣時是每10ms采集一次,采集32次排序,取中間的24個值求平均,每秒運算出一個值。但是實際測量中,大概每隔30S左右。我的采樣值會連續(xù)2-4

2023-06-26 08:14:59

測試條件:

1,線性電源12.6V,分壓電阻20K:2K

2,AMS1117降壓到5V供電 N76E003 ;

3,ADC_BandGap讀出來是比較穩(wěn)定的。

4,ADC單通道在分壓電阻處連續(xù)采樣

2023-06-25 13:23:43

PCIE高速傳輸方案傳輸?shù)膸捓寐士蛇_(dá)到90%以上,延遲可達(dá)到理論的最低延遲值。該方案已經(jīng)應(yīng)用到航天航空、雷達(dá)等領(lǐng)域。一、 高效率傳輸方案 該采集方案 Demo 基于 VC709 開發(fā)板

2021-05-19 08:58:02

10KE EPF10K30E, FLEX 10KE EPF10K50S, FLEX 10KE EPF10K100E, FLEX 10KE EPF10K130E, FLEX 10

2012-08-15 12:30:03

需要實現(xiàn)整數(shù)和半整數(shù)頻率合成;輸出頻率范圍為1KHz-999.5KHz,步進(jìn)頻率為0.5KHz。FPGA芯片選用的是FLEX 10K系列的EPF10K10LC84-4,40MHz的有源晶振,LCD1602顯示小妹實在是太菜了,看了幾日還在門外徘徊,不知大神們是否有心情,求賜教~

2014-03-30 13:51:03

項目名稱:高速AD采集板試用計劃:申請理由本人一直做高速AD采集及高速DA設(shè)計,一直使用Xilinx K7 系列及ZYNQ系列FPGA,電源方面一直尋求更好的解決方案。想借助發(fā)燒友論壇和MPS電源

2020-06-18 13:43:36

對數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實時性。對數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計,有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

高速、超寬帶信號采集技術(shù)在雷達(dá)、天文和氣象等領(lǐng)域應(yīng)用廣泛。高采樣率需要高速的模/數(shù)轉(zhuǎn)換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現(xiàn)的數(shù)據(jù)采集對FPGA的性能和PCB布局布線技術(shù)提出了嚴(yán)峻的挑戰(zhàn)。

2019-11-08 06:34:52

環(huán)境模擬信號的高速采集、分析、記錄、存儲和回放產(chǎn)生。超寬帶信號高速采集記錄存儲回放系統(tǒng)基于高性能PCI EXPRESS及SRIO協(xié)議,實現(xiàn)標(biāo)準(zhǔn)化、模塊化、可擴(kuò)展、可重構(gòu)的超寬帶信號高速連續(xù)采集記錄回放產(chǎn)生

2020-08-26 11:53:36

哪位大神能告我如何在qutars ii上添加EPF10K20TC144-4的褲

2014-05-31 11:01:55

。為了實現(xiàn)高速、連續(xù)采樣的數(shù)據(jù)采集系統(tǒng),本文介紹了一種基于 FPGA +AD7609的數(shù)據(jù)采集系統(tǒng)的構(gòu)成及技術(shù)實現(xiàn)。采用 FPGA 作為主模塊,AD7609為數(shù)據(jù)采集模塊,并設(shè)計了硬件實現(xiàn)電路。實驗測試

2018-08-09 14:28:00

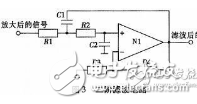

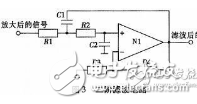

的輸入輸出接口設(shè)計就顯得尤為重要。1 高速采集系統(tǒng)介紹 數(shù)據(jù)采集系統(tǒng)原理框圖如圖1所示,輸入的中頻信號經(jīng)A/D采樣電路采樣后,轉(zhuǎn)換成LVDS信號送入FPGA中,或通過FPGA的端口RocketIO從高速接口

2018-12-18 10:22:18

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案中,有采用通用單片機和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實現(xiàn)

2019-09-05 07:22:57

率、高精度、多通道同步數(shù)據(jù)采集方案,可以通過監(jiān)測者的要求完成多通道數(shù)據(jù)的同步采集并實現(xiàn)實時的網(wǎng)絡(luò)傳輸。 基于ARM+FPGA的高速同步

2010-08-31 09:14:55

為了實現(xiàn)—是彈武器瞄準(zhǔn)自動化,本文設(shè)計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計了CCD驅(qū)動時序電路,采用

2014-11-07 14:54:07

) 以其可靠性好、集成度高、功耗低和運算速度高等優(yōu)勢,在高速實時圖像采集系統(tǒng)得到廣泛應(yīng)用。這里采用FPGA控制MV-D1024E系列相機的數(shù)據(jù)接口,實現(xiàn)了脫離PC機的圖像采集卡功能。為方便系統(tǒng)和用戶輸入,設(shè)計了基于USB的PC機接口。通過USB接口,同樣可用于脫離PC機的系統(tǒng)。

2019-07-02 08:11:34

本文主要討論使用FLEX10K系列FPGA來實現(xiàn)信道編碼的功能。

2021-06-07 06:00:58

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

怎么實現(xiàn)高速采樣保持電路的設(shè)計?

2021-10-11 07:42:17

你好,我感興趣的是匯集一個高速數(shù)據(jù)采集系統(tǒng)。我正在考慮將高速ADC直接連接到FX3/FX3S的可能性,而不使用例如使用GPIF的FPGA。我所看到的ADCs是14(或16)位四路和八路同時采樣ADC

2019-09-11 10:56:03

數(shù)字濾波器是什么?數(shù)字濾波器有哪些特點?怎樣去設(shè)計一種基于EPF10K10LC84芯片的IIR濾波器?

2021-10-20 08:01:13

如何利用單片機AT89C52對FLEX10K系列FPGA中的EPF10K10進(jìn)行在線并行配置?

2021-04-29 06:19:03

求大神分享一種高速突發(fā)模式誤碼測試儀的FPGA實現(xiàn)方案

2021-04-29 06:58:18

電機控制之旋變及位置反饋解決方案篇其它話題的熱門問答請前往總貼查看。http://www.deyisupport.com/question_answer/microcontrollers/c2000

2020-05-20 09:33:31

得到采集數(shù)據(jù),在數(shù)據(jù)傳輸端,可以采用如下4種方案:方案1:通過設(shè)置觸發(fā)門限,只采集有用信號。 在脈沖周期為10ms時,每個脈沖根據(jù)觸發(fā)設(shè)置,采集3us左右(長度可以設(shè)置),約3000個采樣點;實時傳輸

2016-08-15 14:59:39

在超高速數(shù)據(jù)采集方面,FPGA(現(xiàn)場可編程門陣列)有著單片機和DSP所無法比擬的優(yōu)勢。FPGA時鐘頻率高,內(nèi)部時延小,目前器件的最高工作頻率可達(dá)300MHz;硬件資源豐富,單片集成的可用門數(shù)達(dá)1000萬門;全部控制邏輯由硬件資源完成,速度快,效率高;組成形式靈活,可以集成外圍控制、譯碼和接口電路。

2019-08-02 06:51:33

` PXDAQ18373E是一款高精度高速率的聲發(fā)射采集卡,該卡具有真實的18bit采樣精度和每通道30M/S的采樣率,采用標(biāo)準(zhǔn)的PICE2.0 X 8接口,數(shù)據(jù)通過率高達(dá)2.6GB/s,是迄今為止

2016-09-22 14:17:14

探討了高速數(shù)據(jù)采集系統(tǒng)中高速采樣緩存的重要性和實現(xiàn)途徑,闡述了基于ADSP-21065L的并行多通道數(shù)據(jù)采集板上高速采樣緩存的設(shè)計與電路結(jié)構(gòu),給出了采用FPGA實現(xiàn)通道復(fù)用和采樣數(shù)據(jù)

2009-04-23 17:08:09 23

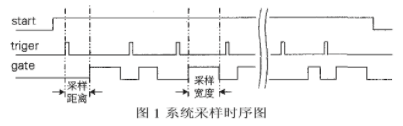

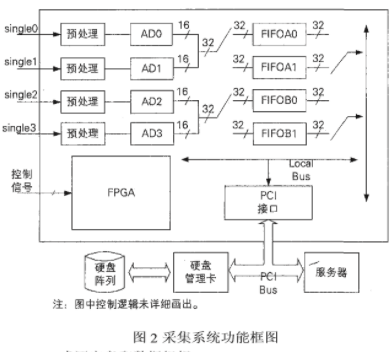

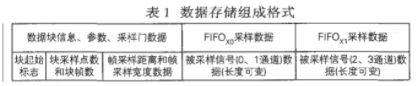

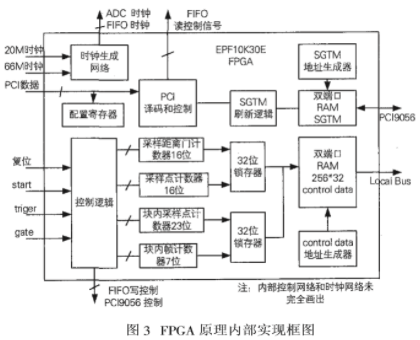

23 本文提出了一種用于雷達(dá)回波信號采集的高速數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)實現(xiàn)了對數(shù)十兆赫的回波信號進(jìn)行連續(xù)的采樣和存儲。系統(tǒng)通過FPGA控制數(shù)據(jù)連續(xù)采集、緩沖,通過PCI9056將緩沖區(qū)

2009-08-15 11:45:53 23

23 本文介紹了一種高速雙通道遙感衛(wèi)星信號實時采集處理技術(shù)的研究與實現(xiàn)。基于Xilinx Spartan3 150萬門高性能FPGA,設(shè)計出具有數(shù)據(jù)海量傳輸和高速處理能力需求的衛(wèi)星信號采集處

2009-09-26 15:30:39 25

25 本文介紹了一種基于FPGA 的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計方案,描述了系統(tǒng)的主要組成及FPGA 的實現(xiàn)方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現(xiàn)A/D 轉(zhuǎn)換器的控制電路、多路

2009-12-19 16:02:33 50

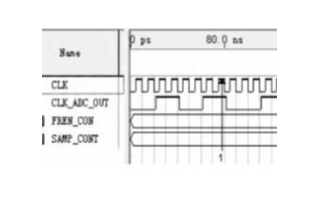

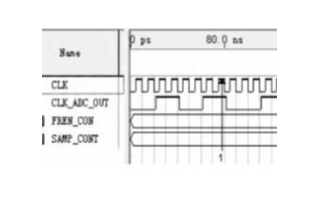

50 本文介紹了一種能夠完成半整數(shù)和各種占空比的奇/偶數(shù)和的通用的分頻器設(shè)計,并給出了本設(shè)計在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中實現(xiàn)后的測試數(shù)據(jù)和設(shè)計硬件的測

2009-12-19 16:25:09 65

65 本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進(jìn)行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進(jìn)行采樣,采樣后的數(shù)據(jù)通過FPGA進(jìn)行數(shù)據(jù)

2009-12-23 15:09:09 15

15 本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進(jìn)行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進(jìn)行采樣,采樣后的數(shù)據(jù)通過FPGA進(jìn)行數(shù)據(jù)處理,再

2010-07-21 17:24:58 26

26 為解決現(xiàn)有采集存儲系統(tǒng)不能同時滿足高速率采集,大容量脫機且長時間持續(xù)存儲的問題,設(shè)計了一種基于SATA硬盤和FPGA的數(shù)據(jù)采集和存儲方案。本設(shè)計由AD9627轉(zhuǎn)換芯片,Altera Cyclone系列

2011-11-15 11:35:19 170

170 本文一Spartan-3E系列FPGA為核心控制模塊,結(jié)合AD10242數(shù)模轉(zhuǎn)換芯片和MAX-123MD-F光收發(fā)模塊,實現(xiàn)了告訴數(shù)據(jù)采集和光纖傳輸。

2012-05-24 15:38:26 72

72 恒頤基于ARM+FPGA的高速同步數(shù)據(jù)采集方案,解決了數(shù)據(jù)采集的同步性問題,與以往的數(shù)據(jù)采集方案相比,具有高精度、高速率、多參數(shù)同步測量、實時處理、網(wǎng)絡(luò)傳輸不受區(qū)域限制等特點

2012-11-27 10:51:24 1670

1670 高速數(shù)據(jù)采集系統(tǒng)中的FPGA的設(shè)計,下來看看

2016-05-10 11:24:33 15

15 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設(shè)計.

2016-05-10 17:06:40 48

48 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計.

2016-05-10 17:06:40 27

27 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計,下來看看

2016-05-10 17:06:40 21

21 基于FPGA高速數(shù)據(jù)采集的解決方案,下來看看

2016-05-11 09:46:01 13

13 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計,用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 基于FPGA的高速圖像采集系統(tǒng)的研究與設(shè)計

2016-08-30 15:10:14 6

6 變采樣率技術(shù)在連續(xù)波測速雷達(dá)中的應(yīng)用,下來看看

2017-01-08 15:59:09 12

12 基于FPGA實現(xiàn)變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 基于FPGA的高速多通道AD采樣系統(tǒng)的設(shè)計與實現(xiàn)_徐加彥

2017-01-18 20:23:58 12

12 本文針對由FPGA構(gòu)成的高速數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)處理能力弱的問題,提出FPGA與單片機實現(xiàn)數(shù)據(jù)串行通信的解決方案。

2017-02-11 14:30:00 11728

11728 采用FPGA實現(xiàn)對AD 輸出數(shù)據(jù)的高速采集

2017-08-30 17:16:02 36

36 提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收發(fā)器設(shè)計的一個高速串行傳輸實現(xiàn)方案,詳細(xì)闡述了硬件設(shè)計要點和軟件實現(xiàn)概要,系統(tǒng)實測表明,該方案能在某信號處理系統(tǒng)兩個板卡之間穩(wěn)定地進(jìn)行1.6 Gb/s的數(shù)據(jù)傳輸,誤碼率優(yōu)于10e-12,傳輸距離大于1米。

2017-11-21 10:16:00 9094

9094 針對機械設(shè)備運行中的振動監(jiān)控,設(shè)計振動信號采集系統(tǒng),提出了一種基于FPGA的振動信號采集系統(tǒng)的設(shè)計方案。重點闡述了系統(tǒng)硬件結(jié)構(gòu)組成、信號調(diào)理電路和數(shù)據(jù)采集模塊的設(shè)計,同時對A/D采樣的控制邏輯進(jìn)行了討論。經(jīng)試驗驗證表明,該系統(tǒng)可達(dá)到采樣率10 K每秒、采集精度16位,能夠滿足實時性和精度要求。

2017-11-17 11:04:38 8468

8468

設(shè)計了基于FPGA與ARM 芯片的數(shù)據(jù)采集系統(tǒng),FPGA 負(fù)責(zé)控制A/D轉(zhuǎn)換器,保證了采樣精度與處理速度,ARM負(fù)責(zé)邏輯控制及與上位機交互的實現(xiàn),并將采集到的數(shù)據(jù)通過USB高速上傳至主機進(jìn)行實時處理。對模擬數(shù)據(jù)采集的測試結(jié)果達(dá)到了較高的采樣精度和速度,驗證了整個系統(tǒng)的高速性和可行性。

2017-11-18 12:47:10 5019

5019

隨著測試環(huán)境越來越復(fù)雜,需要采集的參數(shù)種類越來越多,要求采集系統(tǒng)連續(xù)采集各種傳感器輸出的模擬信號,而目前常用的固態(tài)存儲器件FLASH的寫入速率比較低。本文提出一種基于FPGA(現(xiàn)場可編程門陣列)片

2018-07-12 09:06:00 6077

6077

利用AD574A設(shè)計基于FPGA的高速數(shù)據(jù)采集系統(tǒng),系統(tǒng)包含內(nèi)嵌雙口,在FPGA內(nèi)部實現(xiàn)的RAM用于寫入操作;地址計數(shù)器,用于提供存儲地址保存采集數(shù)據(jù)。具備高采樣精度、高集成度,并且速度快、靈活性強、可靠性高,易于升級與擴(kuò)展。

2017-12-18 17:37:20 9294

9294

,常規(guī)做法是利用插值和抽取的方法實現(xiàn)數(shù)字信號的變采樣處理,這種方法實現(xiàn)復(fù)雜,硬件成本高。文中提出了一種高速并行成型濾波器的FPGA實現(xiàn)方法,這種基于群延時結(jié)構(gòu)的查找表算法,所需的查找表只需存儲單位沖擊響應(yīng)的采樣值,

2018-02-23 10:14:22 0

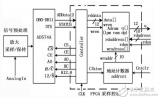

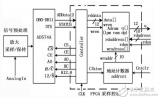

0 數(shù)據(jù)采集系統(tǒng)的總體架構(gòu)如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內(nèi)部實現(xiàn)。為實現(xiàn)多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態(tài)機控制下,完成模擬信號經(jīng)過

2018-08-28 10:16:07 14862

14862

為了實現(xiàn)高清晰度油氣管道漏磁檢測器高精度多通道數(shù)據(jù)采集的要求,采用AlteraCyclone系列FPGA EPlC6為核心控制模塊,結(jié)合AD9223模數(shù)轉(zhuǎn)換芯片構(gòu)建了超多通道、高速數(shù)據(jù)采集系統(tǒng)。利用

2018-10-16 10:34:09 51

51 在嵌入式系統(tǒng)設(shè)計中,掌握MCU對FPGA的配置,對系統(tǒng)的設(shè)計是十分必要的。根據(jù)EPF10K10的配置時序和AVR單片機Atmega128的接口特點,詳細(xì)介紹了Atmega128對EPF10K10配置的軟硬件設(shè)計原理。

2018-10-26 15:34:41 9

9 本文提出了一種實現(xiàn)信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統(tǒng)的系統(tǒng)設(shè)計,并著重介紹前端硬件的設(shè)計,并就ARM 處理器和FPGA 的互聯(lián)設(shè)計進(jìn)行探討。利用FPGA 硬件控制A/D 轉(zhuǎn)換,達(dá)到了較好的效果,實現(xiàn)了信號的采集與存儲。

2018-11-02 15:46:01 12

12 介紹了1種基于FPGA和DSP的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計和實現(xiàn),其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 20

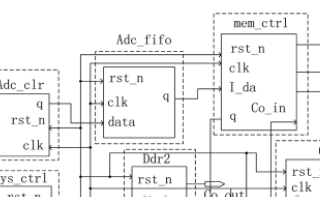

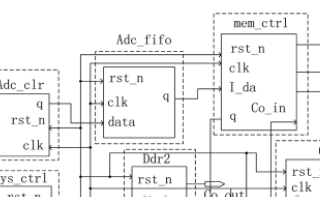

20 采用DDR2 SDRAM作為被采集數(shù)據(jù)的緩存技術(shù), 給出了USB2.0與DDR2相結(jié)合的實時、高速數(shù)據(jù)采集系統(tǒng)的解決方案, 同時提出了對數(shù)據(jù)采集系統(tǒng)的改進(jìn)思路以及在Xilinx的Virtex5 LX30 FPGA上的實現(xiàn)方法。

2018-12-07 16:12:39 21

21 在FPGA高速AD采集設(shè)計中,PCB布線差會產(chǎn)生干擾。今天小編為大家介紹一些布線解決方案。

2019-03-07 14:52:24 7372

7372 提出了一種基于FPGA+ARM的多路視頻采集系統(tǒng)的設(shè)計與實現(xiàn)方法。該視頻采集系統(tǒng)不僅能對多路快速變化的視頻信號進(jìn)行采集和處理,而且能應(yīng)用為系統(tǒng)信號發(fā)生設(shè)備.系統(tǒng)采用FPGA為核心高速時序邏輯控制

2019-11-19 15:51:42 21

21 FPGA是一種可編程邏輯器件,它具有良好性能、極高的密度和極大的靈活性,外圍電路簡單可靠等特性。因此,該系統(tǒng)設(shè)計是由MCU、FPGA、按鍵等部分組成。60路按鍵信號進(jìn)入FPGA單元,以供數(shù)據(jù)采集

2020-08-11 14:40:36 1164

1164

基于FPGA 在高速數(shù)據(jù)采集方面有單片機和DSP 無法比擬的優(yōu)勢, FPGA 具有時鐘頻率高,內(nèi)部延時小, 全部控制邏輯由硬件完成, 速度快,效率高,組成形式靈活等特點。因此,本文研究并開發(fā)了一個

2020-08-21 16:16:00 32

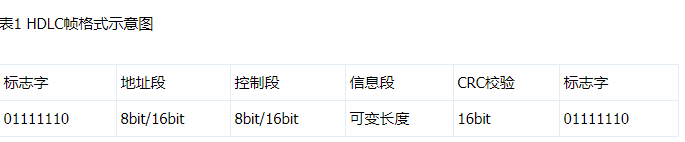

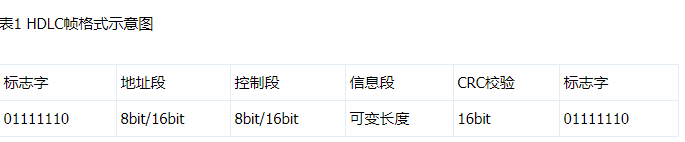

32 .同時它還具有設(shè)計開發(fā)周期短、設(shè)計制造成本低、可實時在線檢驗等優(yōu)點,因此被廣泛用于特殊芯片設(shè)計中.本設(shè)計中采用Altera公司的FLEX10K芯片EPF10K20RC240-3來實現(xiàn)HDLC協(xié)議控制器.

2020-09-27 21:00:12 1829

1829

本文檔的主要內(nèi)容詳細(xì)介紹的是基于FPGA的AD采樣的實現(xiàn)免費下載。

2021-01-21 15:33:54 32

32 通過FPGA(現(xiàn)場可編程門陣列)時序模型分析得出FPGA門延時的方案,綜合利用FPGA各種布局布線EDA工具,摸索出一套人工干預(yù)FPGA布局布線的方法,使FPGA門延時能夠有效地用于時序調(diào)整,調(diào)整精度可達(dá)到納秒級。該方法具有不增加任何額外器件,成本低、高效方便的特點。

2021-01-26 16:22:00 13

13 基于圖像采集系統(tǒng)高速、大容量的特點,提出了一種以FPGA芯片為核心處理器件的CMOS圖像傳感器數(shù)據(jù)采集系統(tǒng)的設(shè)計方案。系統(tǒng)將模塊化結(jié)構(gòu)設(shè)計、LVDS與乒乓存儲等多項技術(shù)應(yīng)用于設(shè)計過程中,保證了

2021-01-29 15:27:49 9

9 介紹一種基于Actel公司Fusion StartKit FPGA的線陣CCD圖像數(shù)據(jù)采集系統(tǒng)。以FPGA作為圖像數(shù)據(jù)的控制和處理核心,通過采用高速A/D、異步FIFO、UART以及電平轉(zhuǎn)換、放大

2021-02-02 17:12:32 8

8 為了解決圖像掃描設(shè)備與主機之間海量數(shù)據(jù)高速傳輸問題,提出了一種基于FPGA的圖像數(shù)據(jù)采集卡的設(shè)計方法。該設(shè)計方法對采集卡的原理設(shè)計、FPGA的開發(fā)以及驅(qū)動程序的實現(xiàn)進(jìn)行了研究;板卡采用

2021-02-03 16:26:11 21

21 針對高速率QPSK數(shù)據(jù)傳輸鏈系統(tǒng),比較分析了數(shù)字中頻接收與零中頻接收的優(yōu)、缺點,并提出了一種基于多相濾波的寬帶中頻正交采樣數(shù)字零中頻接收方案。基于FPGA對此數(shù)字零中頻正交變換方案進(jìn)行了實現(xiàn)和驗證,同時,對一種全數(shù)字零中頻QPSK信號的高速解調(diào)算法及其FPGA硬件實現(xiàn)進(jìn)行了介紹。

2021-03-19 17:43:12 11

11 AGM FPGA之AG10K 系列的開發(fā)建議(連載二)

2021-12-05 17:21:14 27

27 對速度要求;后者雖然可以實現(xiàn)高速傳輸,但DSP價格過于昂貴。而利用FPGA和USB接口芯片結(jié)合的方案,具有功耗低、時鐘頻率高、速度快、效率高、組合形式靈活等特點,是單片機和DSP所無法比擬的。 系統(tǒng)總體方案 根據(jù)本系統(tǒng)要實現(xiàn)的功能,該系統(tǒng)硬件

2023-10-06 14:55:02 2955

2955

電子發(fā)燒友App

電子發(fā)燒友App

評論