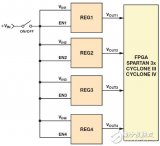

電源時(shí)序控制是微控制器、FPGA、DSP、 ADC和其他需要多個(gè)電壓軌供電的器件所必需的一項(xiàng)功能。##通過(guò)將衰減版本的調(diào)節(jié)器輸出端連接至待上電的下一個(gè)調(diào)節(jié)器使能引腳,可對(duì)多通道電源進(jìn)行時(shí)序控制。

2014-08-05 10:15:54 4625

4625

電源時(shí)序控制是微控制器、FPGA、DSP、ADC和其他需要多個(gè)電壓軌供電的器件所必需的一項(xiàng)功能。##使用電阻分壓器簡(jiǎn)化電源時(shí)序控制

2014-08-14 10:57:25 3181

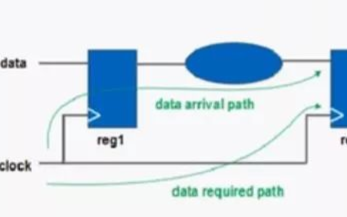

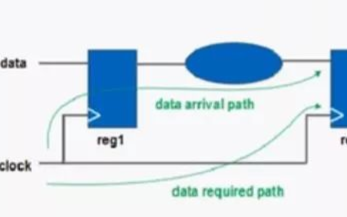

3181 表。 這4類(lèi)路徑中,我們最為關(guān)心是②的同步時(shí)序路徑,也就是FPGA內(nèi)部的時(shí)序邏輯。 時(shí)序模型 典型的時(shí)序模型如下圖所示,一個(gè)完整的時(shí)序路徑包括源時(shí)鐘路徑、數(shù)據(jù)路徑和目的時(shí)鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 3687

3687

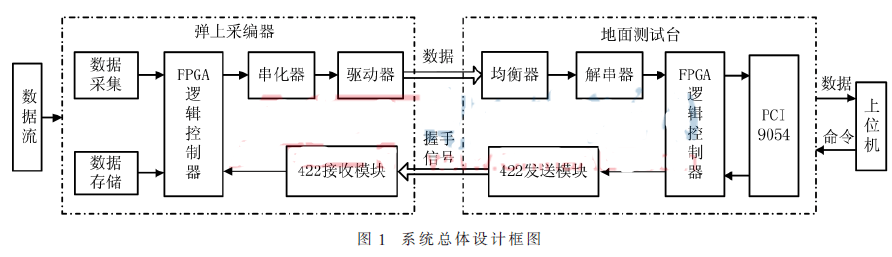

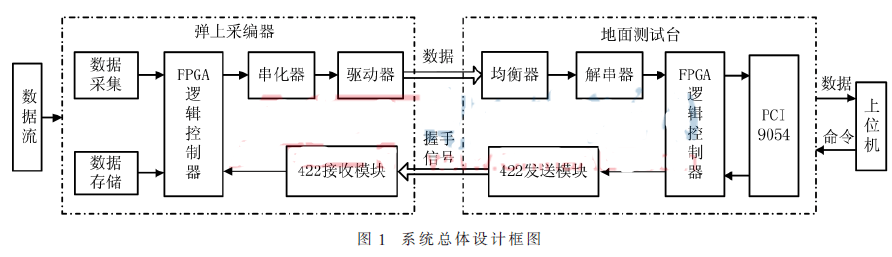

通過(guò)以上分析,首先在硬件設(shè)計(jì)方面對(duì)LVDS接口電路進(jìn)行優(yōu)化。在數(shù)據(jù)發(fā)送端,使用SN65LV1023A串化器將FPGA輸出的并行數(shù)據(jù)轉(zhuǎn)化為串行輸出,其次在發(fā)送端增加LMH0001SQ高速驅(qū)動(dòng)器,增強(qiáng)

2020-12-22 16:49:00 2572

2572

在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是一個(gè)重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

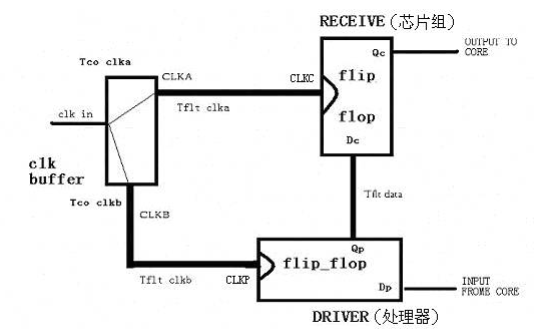

2392 對(duì)于系統(tǒng)設(shè)計(jì)工程師來(lái)說(shuō),時(shí)序問(wèn)題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫(xiě)窗口越來(lái)越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整地傳送到接收端,就必須進(jìn)行精確的時(shí)序

2022-12-13 10:50:35 2848

2848

FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間。

2023-06-06 17:53:07 1938

1938

前面講解了時(shí)序約束的理論知識(shí)FPGA時(shí)序約束理論篇,本章講解時(shí)序約束實(shí)際使用。

2023-08-14 18:22:14 3030

3030

這篇文章是探討對(duì)接收端進(jìn)行時(shí)序優(yōu)化(即ready打拍,或稱backward打拍)的方式。

2023-12-04 10:20:55 1207

1207

在輸入信號(hào)到輸出信號(hào)中,因?yàn)榻?jīng)過(guò)的傳輸路徑、寄存器、門(mén)電路等器件的時(shí)間,這個(gè)時(shí)間就是時(shí)序。開(kāi)發(fā)工具不知道我們路徑上的要求,我們通過(guò)時(shí)序約束來(lái)告訴開(kāi)發(fā)工具,根據(jù)要求,重新規(guī)劃,從而實(shí)現(xiàn)我們的時(shí)序要求,達(dá)到時(shí)序的收斂。

2019-07-31 14:50:41 7018

7018

今天給大俠帶來(lái)FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂,話不多說(shuō),上貨。

這里超鏈接一篇之前的STA的文章,僅供各位大俠參考。

FPGA STA(靜態(tài)時(shí)序分析)

什么是靜態(tài)時(shí)序分析?靜態(tài)時(shí)序分析就是

2024-06-17 17:07:28

引言 現(xiàn)場(chǎng)可編程邏輯門(mén)陣列FPGA器件的出現(xiàn)是超大規(guī)模集成電路技術(shù)和計(jì)算機(jī)輔助設(shè)計(jì)技術(shù)發(fā)展的結(jié)果。FPGA器件集成度高、體積小,具有通過(guò)用戶編程實(shí)現(xiàn)專(zhuān)門(mén)應(yīng)用功能。它允許電路設(shè)計(jì)者利用基于計(jì)算機(jī)的開(kāi)發(fā)

2018-12-18 09:51:38

從可編程器件發(fā)展看FPGA未來(lái)趨勢(shì) 15第三章、FPGA主要供應(yīng)商與產(chǎn)品 173.1.1 賽靈思主要產(chǎn)品介紹 17第四章、FPGA開(kāi)發(fā)基本流程 294.1 典型FPGA開(kāi)發(fā)流程與注意事項(xiàng) 294.2

2009-04-09 18:28:46

布線、時(shí)序驗(yàn)證,這一階段是詳細(xì)設(shè)計(jì)階段;第三個(gè)階段是FPGA器件實(shí)現(xiàn),除了器件燒錄和板級(jí)調(diào)試外,其實(shí)這個(gè)階段也應(yīng)該包括第二個(gè)階段的布局布線和時(shí)序驗(yàn)證,因?yàn)檫@兩個(gè)步驟都是和FPGA器件緊密相關(guān)的。我們

2019-01-28 04:24:37

FPGA時(shí)序分析系統(tǒng)時(shí)序基礎(chǔ)理論對(duì)于系統(tǒng)設(shè)計(jì)工程師來(lái)說(shuō),時(shí)序問(wèn)題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫(xiě)窗口越來(lái)越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整

2012-08-11 17:55:55

FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間

2023-11-15 17:41:10

對(duì)自己的設(shè)計(jì)的實(shí)現(xiàn)方式越了解,對(duì)自己的設(shè)計(jì)的時(shí)序要求越了解,對(duì)目標(biāo)器件的資源分布和結(jié)構(gòu)越了解,對(duì)EDA工具執(zhí)行約束的效果越了解,那么對(duì)設(shè)計(jì)的時(shí)序約束目標(biāo)就會(huì)越清晰,相應(yīng)地,設(shè)計(jì)的時(shí)序收斂過(guò)程就會(huì)更可

2016-06-02 15:54:04

(InputDelay、OutputDelay)、上下拉電阻、驅(qū)動(dòng)電流強(qiáng)度等。加入I/O約束后的時(shí)序約束,才是完整的時(shí)序約束。FPGA作為PCB上的一個(gè)器件,是整個(gè)PCB系統(tǒng)時(shí)序收斂的一部分。FPGA作為

2017-12-27 09:15:17

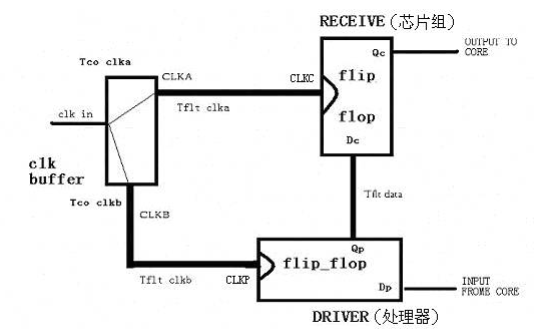

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)在數(shù)字系統(tǒng)的同步接口設(shè)計(jì)中, 可編程邏輯器件的輸入輸出往往需要和周?chē)缕瑢?duì)接,此時(shí)IPO接口的時(shí)序問(wèn)題顯得尤為重要。介紹了幾種FPGA中的IPO時(shí)序優(yōu)化設(shè)計(jì)的方案, 切實(shí)有效的解決了IPO接口中的時(shí)序同步問(wèn)題。

2012-08-12 11:57:59

FPGA入門(mén):基本開(kāi)發(fā)流程概述 在第一章中,已經(jīng)給出了FPGA/CPLD的基本開(kāi)發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA/CPLD器件開(kāi)發(fā)流程,從項(xiàng)目

2019-01-28 02:29:05

FPGA的設(shè)計(jì)流程就是利用EDA開(kāi)發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開(kāi)發(fā)的過(guò)程。FPGA的開(kāi)發(fā)流程一般包括功能定義、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)與布局布線、時(shí)序仿真與驗(yàn)證、板級(jí)仿真

2023-12-31 21:15:31

基本的時(shí)序分析理論1本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態(tài)時(shí)序分析(STA,Static

2015-07-09 21:54:41

模塊,熟練verilog語(yǔ)言,熟練使用Altera FPGA的開(kāi)發(fā)環(huán)境,熟練使用仿真、綜合、時(shí)序分析工具,有1年以上工作經(jīng)驗(yàn)者優(yōu)先。簡(jiǎn)歷接收郵箱:awejob@chnawe.com 。歡迎各位小伙伴們

2016-09-27 16:45:15

FPGA有哪些開(kāi)發(fā)環(huán)境?可以用VSCode開(kāi)發(fā)嘛?

2024-04-29 23:05:48

FPGA/CPLD的綜合、實(shí)現(xiàn)過(guò)程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析。

2023-09-21 07:45:57

FPGA 設(shè)計(jì)優(yōu)化主要分為編碼風(fēng)格、設(shè)計(jì)規(guī)劃和時(shí)序收斂三大部分,這 些因素直接決定了 FPGA 設(shè)計(jì)的成敗。 編碼風(fēng)格直接影響 FPGA 設(shè)計(jì)的實(shí)現(xiàn)并最終影響設(shè)計(jì)的性能。盡管綜合 工具集成

2022-09-29 06:12:02

的相位偏移將有效地改變存儲(chǔ)控制器接收寄存器的最小有效數(shù)據(jù)窗口,因此將形成平衡有效數(shù)據(jù)窗口。時(shí)鐘偏移調(diào)整是FPGA裝置中PLL器件的一個(gè)組成部分。要確定偏移的值,我們必須考慮到影響信號(hào)的布線延遲和任何外部

2017-09-01 10:28:10

隨著FPGA器件體積和復(fù)雜性的不斷增加,設(shè)計(jì)工程師越來(lái)越需要有效的驗(yàn)證方。時(shí)序仿真可以是一種能發(fā)現(xiàn)最多問(wèn)題的驗(yàn)證方法,但對(duì)許多設(shè)計(jì)來(lái)說(shuō),它常常是最困難和費(fèi)時(shí)的方法之一。過(guò)去,采用標(biāo)準(zhǔn)臺(tái)式計(jì)算機(jī)的時(shí)序

2019-07-16 08:10:25

實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是一個(gè)重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。1.2FPGA整體概念 由于IO口時(shí)序約束分析是針對(duì)于電路板

2012-04-25 15:42:03

。Vivado工具支持專(zhuān)用的編輯器實(shí)現(xiàn)時(shí)序約束、I/O引腳約束和布局布線約束。設(shè)計(jì)仿真 在整個(gè)開(kāi)發(fā)過(guò)程的任意時(shí)刻,設(shè)計(jì)者都可以使用仿真工具對(duì)FPGA工程進(jìn)行功能驗(yàn)證,比如Vivado內(nèi)置的仿真器或者第三方工具

2019-04-01 17:50:52

專(zhuān)用的全局時(shí)鐘輸入引腳驅(qū)動(dòng)單個(gè)主時(shí)鐘去控制設(shè)計(jì)項(xiàng)目中的每一個(gè)觸發(fā)器。同步設(shè)計(jì)時(shí), 全局時(shí)鐘輸入一般都接在器件的時(shí)鐘端,否則會(huì)使其性能受到影響。 對(duì)于需要多時(shí)鐘的時(shí)序電路, 最好選用一個(gè)頻率是它們

2012-03-05 14:29:00

資源不足跑不起來(lái),所以暫未實(shí)現(xiàn),后續(xù)考慮實(shí)現(xiàn)一個(gè)俄羅斯方塊或者貪吃蛇)。圖5 FPGA端程序結(jié)構(gòu)圖PSRAM讀寫(xiě)采用云源軟件內(nèi)的PSRAM控制器IP,并按照數(shù)據(jù)手冊(cè)進(jìn)行讀寫(xiě)時(shí)序仿真和設(shè)計(jì),在接收到特定

2021-05-11 09:16:10

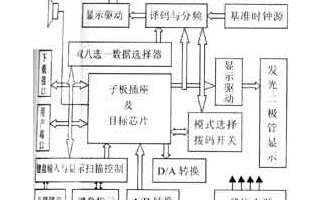

,以及Windows CE、Windows Mobile和Linux環(huán)境的軟件驅(qū)動(dòng)程序。圖2中所示的板卡配有硬盤(pán)驅(qū)動(dòng)器、兩個(gè)SD卡插槽、卡總線接口及用來(lái)連接FPGA器件I/O引腳的接頭

2012-04-27 14:40:21

的劃分;第二個(gè)階段是設(shè)計(jì)實(shí)現(xiàn)階段,這個(gè)階段包括編寫(xiě)RTL代碼、并對(duì)其進(jìn)行初步的功能驗(yàn)證、邏輯綜合和布局布線、時(shí)序驗(yàn)證,這一階段是詳細(xì)設(shè)計(jì)階段;第三個(gè)階段是FPGA器件實(shí)現(xiàn),除了器件燒錄和板級(jí)調(diào)試外

2016-07-13 17:25:34

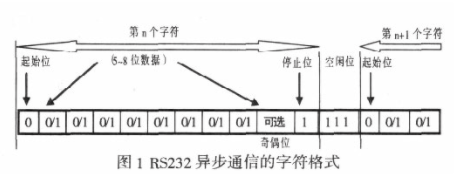

1、在FPGA中實(shí)現(xiàn)串口協(xié)議的設(shè)計(jì)在FPGA中實(shí)現(xiàn)串口協(xié)議,通過(guò)Anlogic_FPGA開(kāi)發(fā)板上的“UART2USB”口接收從計(jì)算機(jī)發(fā)來(lái)的數(shù)據(jù)。實(shí)驗(yàn)設(shè)計(jì)思路UART串口是一種類(lèi)似于USB、VGA

2022-07-19 11:09:48

涉及時(shí)序邏輯電路的實(shí)例,希望能夠幫助大家理解在FPGA中實(shí)現(xiàn)時(shí)序邏輯電路。與組合邏輯電路相比,時(shí)序邏輯電路需要時(shí)鐘的參與,電路中會(huì)有存儲(chǔ)器件的參與,時(shí)序邏輯電路的輸出不僅取決于這一時(shí)刻的輸入,也受此

2022-07-22 15:25:03

?以保證FPGA發(fā)送過(guò)去的數(shù)據(jù)能被外部芯片正確接收的。

FPGA通過(guò)某種通用接口(如SPI)和外部芯片通信時(shí),FPGA如何實(shí)現(xiàn)才能滿足芯片手冊(cè)給出的時(shí)序要求呢?

2023-04-23 11:35:02

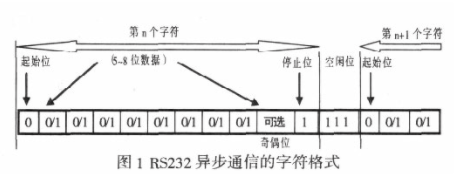

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述

2019-06-19 07:42:37

時(shí)序分析是FPGA設(shè)計(jì)的必備技能之一,特別是對(duì)于高速邏輯設(shè)計(jì)更需要時(shí)序分析,經(jīng)過(guò)基礎(chǔ)的FPGA是基于時(shí)序的邏輯器件,每一個(gè)時(shí)鐘周期對(duì)于FPGA內(nèi)部的寄存器都有特殊的意義,不同的時(shí)鐘周期執(zhí)行不同的操作

2017-02-26 09:42:48

大家好,我想知道如何實(shí)現(xiàn)硬件(FPGA)中的時(shí)序報(bào)告給出的時(shí)序。我的意思是,如何測(cè)量FPGA和FPGA中輸入信號(hào)的建立或保持時(shí)間與靜態(tài)時(shí)間報(bào)告給出的值進(jìn)行比較。FPGA怪胎以上來(lái)自于谷歌翻譯以下

2019-01-15 11:07:15

如何搭建Qt for MCUs PC端開(kāi)發(fā)環(huán)境?

2022-02-10 07:48:18

免各種溫度變化和其他類(lèi)似的設(shè)計(jì)影響,可能在時(shí)鐘或數(shù)據(jù)方面會(huì)遇到一些影響,但不會(huì)很大,因此違背了接收存儲(chǔ)器的建立或保持時(shí)序的要求。在理論上,對(duì)于大部分器件,中心對(duì)齊的時(shí)鐘邊緣將最大限度地建立和保持時(shí)序

2009-04-14 17:03:52

12.288 MHz 的外部時(shí)鐘信號(hào),以實(shí)現(xiàn) 48 KHz 的采樣率。我如何計(jì)算從 CODEC 到 STM32F446 的每個(gè)樣本的接收時(shí)間?

2022-12-19 07:59:50

SpaceWire Codec接收端是什么?怎樣去設(shè)計(jì)SpaeeWire Codec接收端的時(shí)序?時(shí)鐘域可劃分為哪幾個(gè)模塊?如何實(shí)現(xiàn)多時(shí)鐘域信號(hào)的同步?

2021-04-08 07:10:15

1. FPGA時(shí)序的基本概念FPGA器件的需求取決于系統(tǒng)和上下游(upstream and downstrem)設(shè)備。我們的設(shè)計(jì)需要和其他的devices進(jìn)行數(shù)據(jù)的交互,其他的devices可能是

2019-07-09 09:14:48

1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程利用XilinxISE軟件開(kāi)發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實(shí)現(xiàn)、布線后仿真與驗(yàn)證和下班調(diào)試等步驟。如下圖所示。1)電路設(shè)計(jì)

2021-06-24 08:00:01

USB數(shù)據(jù)與并行I/O口數(shù)據(jù)的交換緩沖區(qū)。FIFO實(shí)現(xiàn)與外界(微控制器、FPGA或其它器件)的接口,主要通過(guò)8根數(shù)據(jù)線D0~D7、讀寫(xiě)控制線RD#和WR#以及FIFO發(fā)送緩沖區(qū)空標(biāo)志TXE#和FIFO接收

2019-04-22 07:00:07

USB數(shù)據(jù)與并行I/O口數(shù)據(jù)的交換緩沖區(qū)。FIFO實(shí)現(xiàn)與外界(微控制器、FPGA或其它器件)的接口,主要通過(guò)8根數(shù)據(jù)線D0~D7、讀寫(xiě)控制線RD#和WR#以及FIFO發(fā)送緩沖區(qū)空標(biāo)志TXE#和FIFO接收

2019-04-26 07:00:12

提出了一種采用現(xiàn)場(chǎng)可編程門(mén)陣列器件FPGA 實(shí)現(xiàn)802.16 接收端MIMO(多輸入多輸出)2×2 檢測(cè)的方案。在C 語(yǔ)言平臺(tái)對(duì)基于并行干擾消除的最小均方誤差的算法進(jìn)行研究和仿真后,使用Ver

2009-06-17 10:00:17 23

23 本實(shí)驗(yàn)是基于EasyFPGA030 的串口接收設(shè)計(jì)。FPGA 除了需要控制外圍器件完成特定的功能外,在很多的應(yīng)用中還需要完成FPGA 和FPGA 之間、FPGA 和外圍器件之間以及FPGA 和微機(jī)的數(shù)據(jù)交換和

2010-03-11 15:39:55 30

30 本文詳細(xì)分析了ADSL系統(tǒng)中ATM層和物理層之間的UTOPIA LEVEL2接口時(shí)序,采用FPGA實(shí)現(xiàn)了UTOPIA接口設(shè)計(jì),應(yīng)用在ADSL系統(tǒng)中,數(shù)據(jù)收發(fā)正確,工作穩(wěn)定;該方案的實(shí)現(xiàn)對(duì)解決現(xiàn)有專(zhuān)門(mén)通信芯

2010-07-28 16:54:10 19

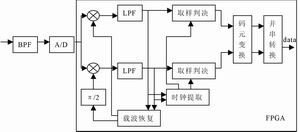

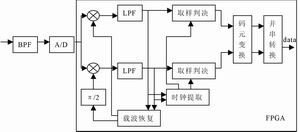

19 本文基于XILINX可編程邏輯器件XC4VLX25 FPGA開(kāi)發(fā)了一個(gè)中頻信號(hào)接收系統(tǒng),利用一個(gè)可配置的硬件平臺(tái)實(shí)現(xiàn)了模擬信號(hào)數(shù)字處理的設(shè)計(jì),為軟件無(wú)線電技術(shù)的研究提供了一個(gè)先進(jìn)的實(shí)驗(yàn)

2010-07-28 18:01:48 17

17 系統(tǒng)(HPS)來(lái)評(píng)估SoC的特性及性能。Intel Agilex? F系列FPGA開(kāi)發(fā)套件提供了一個(gè)完整的設(shè)計(jì)環(huán)境,其中包括采用PCI Express(PCIe)

2024-02-27 11:51:58

摘 要:本文提出了一種基于FPGA的寬帶中頻數(shù)字接收機(jī)的實(shí)現(xiàn)方法。

2006-03-11 13:19:24 1748

1748

如何有效的管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

當(dāng)FPGA設(shè)計(jì)面臨到高級(jí)接口的設(shè)計(jì)問(wèn)題時(shí),EMA的TimingDesigner可以簡(jiǎn)化這些設(shè)計(jì)問(wèn)題,并提供對(duì)幾乎所有接口的預(yù)先精確控制。從簡(jiǎn)單

2009-04-15 14:19:31 947

947

CODEC,CODEC是什么意思

CODEC是“COder/DECoder”的縮寫(xiě),CODEC芯片負(fù)責(zé)數(shù)字與模擬信號(hào)的轉(zhuǎn)換。它可將電腦里的數(shù)字信號(hào)轉(zhuǎn)變成模擬聲音信

2010-03-23 09:38:43 6262

6262 Codec/THX,Codec/THX是什么意思

Codec

由英文編碼器(coder)和譯碼器(decoder)兩詞的詞頭組成的縮略語(yǔ)。指

2010-04-12 10:36:01 1661

1661 當(dāng)你的FPGA設(shè)計(jì)不能滿足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。

2014-08-15 14:22:10 1476

1476 FPGA時(shí)序約束方法很好地資料,兩大主流的時(shí)序約束都講了!

2015-12-14 14:21:25 19

19 基于時(shí)序路徑的FPGA時(shí)序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

2017-01-14 12:49:02 14

14 SuperVessel將包括賽靈思SDAccel開(kāi)發(fā)環(huán)境,支持用C、C++和OpenCL實(shí)現(xiàn)FPGA加速 All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司與IBM公司今天聯(lián)合宣布

2017-02-08 16:06:08 494

494 當(dāng)你的FPGA設(shè)計(jì)不能滿足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。設(shè)計(jì)者現(xiàn)在有一些

2017-02-09 01:59:11 510

510 fpga時(shí)序收斂

2017-03-01 13:13:34 23

23 一個(gè)好的FPGA設(shè)計(jì)一定是包含兩個(gè)層面:良好的代碼風(fēng)格和合理的約束。時(shí)序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來(lái)越重要的作用。毋庸置疑,時(shí)序約束的最終目的是實(shí)現(xiàn)時(shí)序收斂。時(shí)序收斂作為

2017-11-17 07:54:36 2967

2967

針對(duì)八通道采樣器AD9252的高速串行數(shù)據(jù)接口的特點(diǎn),提出了一種基于FPGA時(shí)序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數(shù)據(jù),利用FPGA內(nèi)部的時(shí)鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 7352

7352

現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計(jì)無(wú)法滿足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問(wèn)題的能力。

2017-11-18 04:32:34 3842

3842 作為賽靈思用戶論壇的定期訪客(見(jiàn) ),我注意到新用戶往往對(duì)時(shí)序收斂以及如何使用時(shí)序約束來(lái)達(dá)到時(shí)序收斂感到困惑。為幫助 FPGA設(shè)計(jì)新手實(shí)現(xiàn)時(shí)序收斂,讓我們來(lái)深入了解時(shí)序約束以及如何利用時(shí)序約束實(shí)現(xiàn)

2017-11-24 19:37:55 5955

5955

1. FPGA 開(kāi)發(fā)流程: 電路設(shè)計(jì)與設(shè)計(jì)輸入 ;仿真驗(yàn)證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 10715

10715 FPGA設(shè)計(jì)一個(gè)很重要的設(shè)計(jì)是時(shí)序設(shè)計(jì),而時(shí)序設(shè)計(jì)的實(shí)質(zhì)就是滿足每一個(gè)觸發(fā)器的建立(Setup)/保持(Hold)時(shí)間的要求。

2018-06-05 01:43:00 4865

4865

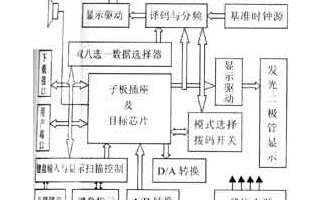

數(shù)據(jù)采集系統(tǒng)的總體架構(gòu)如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內(nèi)部實(shí)現(xiàn)。為實(shí)現(xiàn)多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態(tài)機(jī)控制下,完成模擬信號(hào)經(jīng)過(guò)

2018-08-28 10:16:07 14862

14862

賽靈思公司(Xilinx)推出針對(duì) OpenCL、C 和 C++的S DAccel 開(kāi)發(fā)環(huán)境,將單位功耗性能提高達(dá)25倍,從而利用 FPGA 實(shí)現(xiàn)數(shù)據(jù)中心應(yīng)用加速。SDAccel 是賽靈思 SDx

2018-08-30 17:00:00 1497

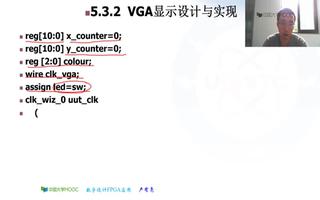

1497 中國(guó)大學(xué)MOOC

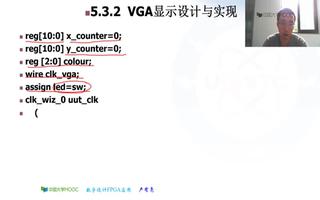

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-08-07 06:00:00 2941

2941

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:08:00 3476

3476

,如何在充分利用現(xiàn)有FPGA器件資源情況下能更高效的實(shí)現(xiàn)所需模塊功能是值得深入研究的。本文首先介紹了實(shí)際應(yīng)用中常見(jiàn)的中頻接收機(jī)各模塊,然后通過(guò)編寫(xiě)各自的硬件描述語(yǔ)言分別映射到三種不同的FPGA芯片,最終通過(guò)布線工具軟件的布線報(bào)告得出相關(guān)的設(shè)計(jì)結(jié)論。

2019-11-28 18:00:41 6

6 隨著FPGA的飛速發(fā)展與其在現(xiàn)代電子設(shè)計(jì)中的廣泛應(yīng)用,越來(lái)越多的實(shí)驗(yàn)和設(shè)計(jì)中會(huì)運(yùn)用FPGA與RS232通信。與此同時(shí), FPGA具有功能強(qiáng)大、開(kāi)發(fā)過(guò)程投資小、周期短、可反復(fù)編程等特點(diǎn)。在FPGA芯片

2020-08-19 16:39:32 2544

2544

當(dāng)前在EDA領(lǐng)域,只要具備臺(tái)式或筆記本電腦并裝有工具軟件,就可以方便地對(duì)可編程ASIC(CPLD/FPGA)進(jìn)行設(shè)計(jì)開(kāi)發(fā),在系統(tǒng)可編程(ISP)器件為我們提供了這種便利條件。ISP方式雖然可以用一根

2020-09-16 20:17:17 1097

1097

器件的選型非常重要,不合理的選型會(huì)導(dǎo)致一系列的后續(xù)設(shè)計(jì)問(wèn)題,有時(shí)甚至?xí)乖O(shè)計(jì)失敗;合理的選型不光可以避免設(shè)計(jì)問(wèn)題,而且可以提高系統(tǒng)的性價(jià)比,延長(zhǎng)產(chǎn)品的生命周期,獲得預(yù)想不到的經(jīng)濟(jì)效果。FPGA 器件

2020-12-23 12:30:00 6

6 說(shuō)到FPGA時(shí)序約束的流程,不同的公司可能有些不一樣。反正條條大路通羅馬,找到一種適合自己的就行了。從系統(tǒng)上來(lái)看,同步時(shí)序約束可以分為系統(tǒng)同步與源同步兩大類(lèi)。簡(jiǎn)單點(diǎn)來(lái)說(shuō),系統(tǒng)同步是指FPGA與外部

2021-01-11 17:46:32 14

14 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束利序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是重點(diǎn)。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 對(duì)于系統(tǒng)設(shè)計(jì)工程師來(lái)說(shuō),時(shí)序問(wèn)題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫(xiě)窗口越來(lái)越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整地傳送到接收端,就必須進(jìn)行精確的時(shí)序

2021-01-14 16:26:51 14

14 、 Synopsys公司的VCS/SS及 FPGA/CPLD廠商的集成開(kāi)發(fā)環(huán)境中自帶的仿真工具,如 Altera Quartus中集成的仿真軟件等

2021-01-20 16:27:59 8

8 AN-1166: 使用HDMI多路復(fù)用器和HDMI接收器的器件的HDMI接收端抖動(dòng)容差問(wèn)題

2021-03-19 04:36:37 7

7 基于FPGA的GPS接收機(jī)實(shí)現(xiàn)說(shuō)明。

2021-04-09 14:01:04 56

56 一、前言 無(wú)論是FPGA應(yīng)用開(kāi)發(fā)還是數(shù)字IC設(shè)計(jì),時(shí)序約束和靜態(tài)時(shí)序分析(STA)都是十分重要的設(shè)計(jì)環(huán)節(jié)。在FPGA設(shè)計(jì)中,可以在綜合后和實(shí)現(xiàn)后進(jìn)行STA來(lái)查看設(shè)計(jì)是否能滿足時(shí)序上的要求。

2021-08-10 09:33:10 6579

6579

本文開(kāi)發(fā)環(huán)境:MCU型號(hào):STM32F103C8T6IDE環(huán)境: MDK 5.27代碼生成工具:STM32CubeMx 5.6.1HAL庫(kù)版本:STM32Cube_FW_F1_V1.8.0本文內(nèi)容

2021-12-06 09:51:11 60

60 上一篇《FPGA時(shí)序約束分享01_約束四大步驟》一文中,介紹了時(shí)序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來(lái)源于明德?lián)P時(shí)序約束專(zhuān)題課視頻。

2022-07-25 15:37:07 3757

3757

FPGA/CPLD的綜合、實(shí)現(xiàn)過(guò)程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析。

2023-04-27 10:08:22 2404

2404 FPGA開(kāi)發(fā)過(guò)程中,vivado和quartus等開(kāi)發(fā)軟件都會(huì)提供時(shí)序報(bào)告,以方便開(kāi)發(fā)者判斷自己的工程時(shí)序是否滿足時(shí)序要求。

2023-06-23 17:44:00 2986

2986

FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間。

2023-06-26 14:42:10 1252

1252

FPGA開(kāi)發(fā)過(guò)程中,vivado和quartus等開(kāi)發(fā)軟件都會(huì)提供時(shí)序報(bào)告,以方便開(kāi)發(fā)者判斷自己的工程時(shí)序是否滿足時(shí)序要求。

2023-06-26 15:29:05 2343

2343

FPGA高級(jí)時(shí)序綜合教程

2023-08-07 16:07:55 9

9 FPGA開(kāi)發(fā)是指利用現(xiàn)場(chǎng)可編程邏輯門(mén)陣列(Field Programmable Gate Array,簡(jiǎn)稱FPGA)進(jìn)行硬件設(shè)計(jì)和實(shí)現(xiàn)的過(guò)程。FPGA是一種可編程的邏輯器件,它允許用戶在制造后通過(guò)

2024-03-15 14:28:56 2679

2679 電子發(fā)燒友網(wǎng)站提供《FPGA電源時(shí)序控制.pdf》資料免費(fèi)下載

2024-08-26 09:25:41 1

1 :?FPGA芯片采用了altera的Cyclon IV E系列的“EP4CE10F17C8”,軟件環(huán)境-Quartus-Ⅱ,采用的AD芯片為—AD-TLC549。 通過(guò)FPGA實(shí)現(xiàn)以下時(shí)序

2024-12-17 15:27:00 1613

1613

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論