Altera公司近日發布其面向FPGA的OpenCL (開放計算語言)早期使用計劃(EAP),支持客戶提前了解Altera面向FPGA的OpenCL解決方案。采用這一開放標準,設計團隊可以在高級C語言框架中面向

2012-09-04 08:47:41 1056

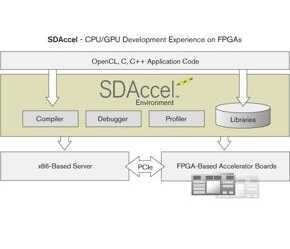

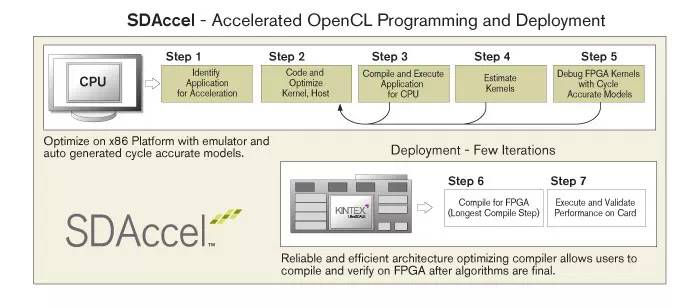

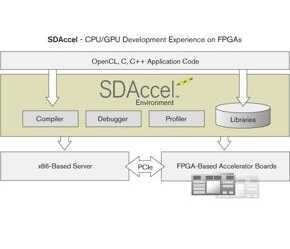

1056 賽靈思在可編程邏輯領域占有領導性地位,此次為了強化數據中心競爭實力,進一步地推出了為數據中心帶來最佳單位功耗性能的針對OpenCL、C和 C++的軟件開發環境SDAccel,可有效解決CPU和GPU

2014-12-03 16:35:46 3712

3712 數據中心采用FPGA做加速器已經成為主流,像MS的Catapult,Amazon基于Xilinx FPGA的AWS F1,Intel的Altera,Baidu公司等

2017-10-16 11:49:24 9499

9499

本文主要分享在軟通動力揚帆系列“競”OpenHarmony開發板上測試Native C++應用開發,實現eTS調用Native C++ 程序實現對給定的兩個數進行加減乘除運算示例(eTS)

2022-10-08 14:37:53 5295

5295 目前開發C++/C用的比較多的當屬Vim、VS code、CLion。

2022-11-25 14:02:19 925

925 這種集成開發環境,為了在 Ubuntu 上也能擁有類似 Visual Studio 的開發體驗,筆者探索出基于 Anaconda 和 VS Code,搭建 OpenVINO C++ 程序開發環境的方式。

2023-08-09 09:42:14 1824

1824

,見證了FPGA在數據中心里可以提供強大的計算能力和足夠的靈活性,來應對數據中心對硬件加速的挑戰。經過之前的FPGA實踐,FPGA聯合團隊獲得了在數據中心使用FPGA的經驗,未來也將在數據中心的計算、網絡

2017-04-15 16:17:41

數據中心光互聯解決方案 隨著數據中心在全球的大規模部署,數據中心對于100Gbps模塊的需求時代已經到了,而對于10G/40Gbps模塊的需求依然強勁。 SMC針對數據中心光模塊應用,提供

2020-07-03 10:36:08

!》,原文作者:啟明 。一、3 年電費消耗,可再建造一個數據中心!1.1 科技驅動,推動數據中心市場持續高速發展國際慣例,先介(bai)紹(du)一(bai)下(ke)“數據中心”:數據中心是全球協作的特定設備網絡,用來在 internet 網絡基礎設施上傳遞、加速、展示、計算、存儲數據信息。一個

2021-06-30 06:27:17

數據中心是什么:數據中心是全球協作的特定設備網絡,用來在因特網絡基礎設施上傳遞、加速、展示、計算、存儲數據信息。數據中心大部分電子元件都是由低直流電源驅動運行的。數據中心的產生致使人們的認識從定量

2021-07-12 07:10:37

數據中心機房的特點是什么?數據中心機房的建設流程是怎樣的?

2021-11-15 06:13:57

數據中心電能質量檢測什么?諧波的檢測需要注意什么?

2021-05-10 06:53:49

ARM是如何滿足數據中心需求的

2021-02-01 06:34:23

如題,我現在是用CH582芯片,有個項目想用C和C++混編(需要用到現成的部分C++代碼),編譯不通過,請問群里的大神們,在MounRiver Studio開發環境如何實現,謝謝了

2022-09-21 07:30:56

OpenHarmony本來就是C和C++開發的,支持C/C++語言環境。應用開發為什么不首選C/C++作為應用開發語言。1、相對于其他開發語言,JS開發的應用性能和資源效率真的就那么高么?2、JS開發的hap包怎么解決代碼的安全性,防止別人解壓hap包,查看源代碼?

2022-06-01 11:30:23

OpenHarmony本來就是C和C++開發的,支持C/C++語言環境。應用開發為什么不首選C/C++作為應用開發語言。1、相對于其他開發語言,JS開發的應用性能和資源效率真的就那么高么?2、JS開發的hap包怎么解決代碼的安全性,防止別人解壓hap包,查看源代碼?求大神解答

2022-03-17 10:30:14

PUE指標能準確衡量數據中心能效嗎?數據中心PUE的局限有哪些?

2021-07-15 09:09:59

些功能原本是用簡單C語言在處理器或DSP中實現的。人們希望能夠找到一種方法,在更高的層次下設計更復雜,更高速的系統,并希望將軟件設計和硬件設計統一到一個平臺下。解決方案C/C++語言是軟件工程師在開發

2015-01-13 16:34:40

有效提高容量。 利用MACOM的專有自對準(SAEFT?)技術,MACOM的L-PIC可實現成本更低、效率極高且可擴展的模塊解決方案,并且有助于提高PIC在云數據中心高密度光互連解決方案中的采用

2018-12-31 22:23:04

數據中心是企業用來容納其關鍵業務應用程序和信息的物理設施。隨著它們的發展,重要的是要長期考慮如何保持它們的可靠性和安全性。什么是數據中心?數據中心通常被稱為單個事物,但實際上它們由許多技...

2021-09-15 06:46:44

數據中心。這一應用模式的轉變需要具備快速擴展能力的計算節點來滿足視頻內容制作和分發的各個不同高計算強度階段的需求,如轉碼需求和水印需求。

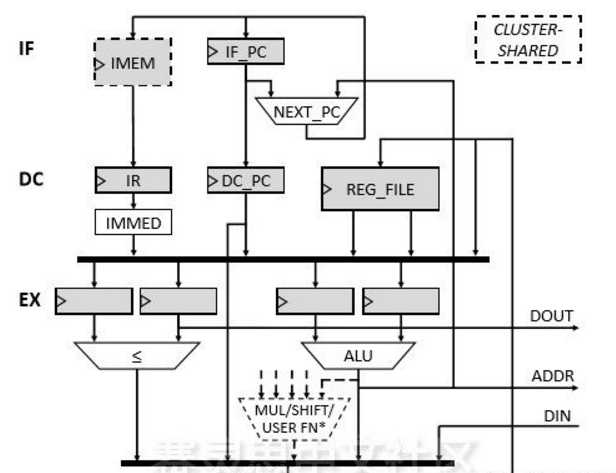

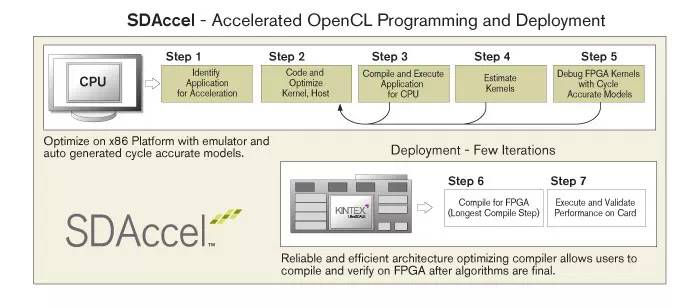

我們近期使用賽靈思SDAccel?開發環境來編譯和優化專為FPGA

2019-06-19 07:27:40

大數據和物聯網是如何影響數據中心的?

2021-05-21 06:24:04

新一代數據中心有哪些實踐操作范例?如何去推進新一代數據中心的發展?

2021-05-25 06:16:40

提高數據中心的運營效率。針對數據中心的能耗即使當前的整個數據中心行業掀起了整合物理資源,并將部分的IT功能遷移到場外異地的新趨勢,但為數據中心內部的各種設...

2021-09-09 06:14:51

本文簡要介紹了如何在IAR中配置C++開發環境,由于C++的封裝支持,引入面向對象的開發思路可以使得用C++進行單片機獲得更高的開發效率

2022-01-27 07:21:38

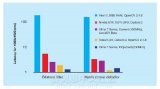

對于各種不同的數據中心工作負載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

外,所有IT物品和服務器機架都可以快速卸下,并放置在中心區域周圍。光模塊也不例外,小封裝的光模塊可以提高空間利用率,可部署更多數量的光模塊,滿足流量高速增長的需求。綠色節能未來數據中心應該需要消耗更少

2020-08-07 10:27:49

基礎 - Plunify視頻處理或數據壓縮 - 恒揚數據采用 FPGA 實現深綠 MPP:一個超動力 Greenplum 數據倉庫解決方案 - Vitesse Data數據與科學計算分論壇數據中心 AI 加速

2019-01-03 15:19:42

《企業網D1Net》12月9日訊(上海)澳大利亞證券交易所(ASX)表示,總部位于日本的KVH公司正在悉尼的ASX新數據中心托管中心設立匯集點(POP),以實現超低延遲的網絡。 新的ASX澳大利亞

2011-12-13 15:11:38

)定位為下一代數據中心選擇的網絡技術有三大驅動因素:性能、智能、效率。 任何存儲結構的關鍵要求是高性能、智能且高效的端到端網絡解決方案,該解決方案針對存儲進行了優化,能夠可靠高效并安全地交付各種數據

2018-08-16 15:08:07

你們有控制中心的C++代碼嗎?我只在程序文件夾中找到了C代碼,但是我想要C++源代碼。 以上來自于百度翻譯 以下為原文Do you guys have the C++ code

2018-12-12 14:48:41

熱量指南。其中許多重點是優化內部設備以實現最佳資源利用,包括降低冷卻功耗。 3.使用通道遏制:這是一種防止數據中心供應側冷空氣與排氣側熱風混合的技術。它涉及使用物理障礙并顯著提高冷卻效率。 4.

2018-08-16 15:35:12

仿真期間的控制臺輸出:-------------------------------------------------- ----------信息:[SDAccel 60-348]使用軟件加速器執行

2020-04-20 09:49:40

平臺是專門針對圖像和語言識別等機器學習應用而精心打造。此外,百度還計劃采用這些平臺來開發商業可行的自動駕駛汽車。百度數據中心采用的功能強大的集中式加速器群可根據用戶需要進行快速配置,以滿足極為嚴苛

2016-12-15 17:15:52

OpenCL開發,也支持C/C++開發,對于軟件開發人員而言,學習成本很低;3) SDAccel支持gdb調試,支持printf()打印調試(僅適用于基于OpenCL的kernel函數);4) 將

2017-09-25 10:06:29

針對用C/C++語言進行的語義分析,設計一種中間結構,即元數據結構。元數據結構實現了源代碼的語義層次上的抽象,通過元數據結構和相關應用語義配置,過濾出源程序中符合應用

2009-04-18 09:02:58 29

29 Visual C++ 6.0利用ADO 開發數據庫應用程序:如圖,這個Demo程序簡單的實現了SQL語言查詢分析器功能,下面我們就以這個程序為例,逐步分 析其實現過程。1、點擊“開始”->“程序

2009-05-10 10:57:08 84

84 由于沒有類似java的“反射”機制,標準C++下實現RMI似乎有些困難。為C++程序員所熟悉的Boost庫雖然有RCF實現了類似RMI的功能,但RCF本身需依賴于Boost::serlization支持,而serlization需要

2010-11-17 18:12:33 14

14 以下是漢源高科萬兆光纖收發器在數據中心的一些應用案例:大型互聯網公司數據中心背景:大型互聯網公司的數據中心需要處理海量的用戶數據和高并發的業務請求,對網絡帶寬和傳輸穩定性要求極高。解決方案:采用漢源

2025-03-20 19:16:23

實驗 用Visual C++做數據庫開發

一、實驗目的1、了解數據庫的訪問方式,掌握ADO 方式訪問數據庫2、用 Visual C++制作簡單的數據

2009-05-10 10:54:26 2667

2667 針對C語言編程者的Verilog開發指南實例

本文舉例說明了如何用軟件實現脈寬調制(PWM),如何將該設計轉換成一個可以在FPGA中運行的邏輯塊,并能利用

2009-12-27 13:26:43 1173

1173 Altera公司(NASDAQ: ALTR)今天發布FPGA和SoC FPGA的開放計算語言(OpenCL?)標準開發計劃。OpenCL標準是基于C語言的開放標準,適用于并行編程。Altera的OpenCL計劃結合了FPGA的并行能力以及OpenCL標準

2011-11-16 16:12:08 1035

1035 開放計算語言(OpenCL)編程模型與Altera的并行FPGA體系結構相結合,實現了功能強大的系統加速解決方案。面向OpenCL的Altera SDK為您提供了設計環境,工程師很容易在FPGA上實現OpenCL應用。

2012-11-06 14:56:42 2201

2201 產品名錄。Altera是唯一能夠提供FPGA最優OpenCL解決方案的公司,支持軟件開發人員充分利用FPGA大規模并行體系結構來實現系統加速。Altera將在10月16-17日在加州圣克拉拉舉辦的2013 Linley處理器大會上演示其OpenCL解決方案。

2013-10-17 15:55:07 1647

1647 All Programmable技術和器件的全球領先企業賽靈思公司 (NASDAQ: XLNX) 今日宣布,其面向OpenCL?、C和C++ 的SDAccel? 開發環境現已順利通過Khronos OpenCL 1.0標準一致性測試。

2015-01-19 10:07:08 1221

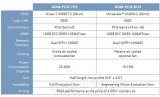

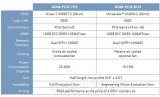

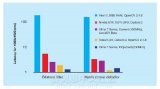

1221 完整的OpenCL、C和C++開發環境,將數據中心的性能功耗比提升高達25倍

2015-05-28 11:25:56 2422

2422 Achronix Semiconductor市場營銷副總裁Steve Mensor表示:“Accelerator-6D加速板為采用PCIe擴展卡的數據中心、高性能計算等細分市場帶來了特有的價值,該加速

2016-06-27 17:47:52 3556

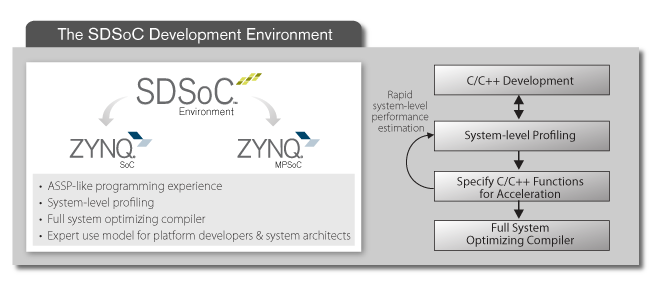

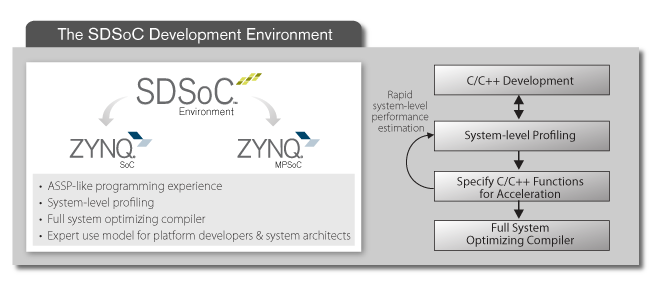

3556 SDSoC? 開發環境可為異構 Zynq? All Programmable SoC 及 MPSoC 部署提供類似嵌入式 C/C++/OpenCL 應用的開發體驗,其中包括簡單易用的 Eclipse IDE 和綜合設計環境。

2017-01-13 12:39:11 2356

2356 Virtex-7系列的VX690T FPGA開發的ADM-PCIE-7V3 FPGA加速板卡是目前商業成品之一,能夠直接支持最初發布SDAccel開發環境版本,這塊板

2017-02-08 12:37:12 914

914

SuperVessel將包括賽靈思SDAccel開發環境,支持用C、C++和OpenCL實現FPGA加速 All Programmable 技術和器件的全球領先企業賽靈思公司與IBM公司今天聯合宣布

2017-02-08 16:06:08 494

494 歡迎 ?11? 月 ?16 ~ 19? 日蒞臨德克薩斯州奧斯汀 ?SC15? 第 ?381? 號展位,您不僅可親眼目睹能夠為數據中心和 ?HPC? 應用實現計算、存儲以及網絡加速的最新異

2017-02-08 20:33:11 238

238 大獎表彰賽靈思利用基于 C、C++ 和 OpenCL 的 FPGA 編程、編譯和可重配置運行時間技術,將數據中心的性能功耗比提升 25 倍 All Programmable技術和器件的全球領先企業賽

2017-02-09 02:31:12 435

435 賽靈思(Xilinx)推出首款支持OpenCL的開發工具。現場可編程門陣列(FPGA)廠商正積極推出可支持OpenCL設計工具的新一代解決方案,期能協助FPGA深入到主流異質架構運算領域,并加速軟件定義數據中心軟硬件運算架構的整合

2017-02-10 06:15:06 1421

1421 近年來,云計算和大數據應用呈爆發式增長,在推動數據中心產業升級的同時,也為數據中心的應用開發與運行維護帶來了一系列問題。

2017-02-10 06:15:34 1544

1544

編程模型。利用這一 SDK,熟悉 C 語言的系統開發人員和編程人員能夠迅速方便的在高級語言環境中開發高性能、高功效、基于 FPGA 的應用。Altera 面向 OpenCL 的 SDK 使得 FPGA 能夠與主處理器協同工作,加速并行計算,而功耗遠遠小于硬件方案。 Altera 將在 SuperCom

2017-09-15 15:46:56 0

0 內即時可重配置功能的軟件工作流,能最大化數據中心的硬件加速ROI,從而克服這一障礙。SDAccel 是一種獨特而完整的基于FPGA 的解決方案,它的功能和簡便易用性遠遠超越了競爭對手的工具。

2017-11-17 15:38:45 1318

1318

IC 推向更廣泛的軟件工程師用戶,賽靈思近期新增了兩款SDxTM 開發環境系列成員。新推出的SDAccelTM 開發環境使沒有任何FPGA經驗的數據中心設備編程員都能夠運用OpenCLTM、C 或C++語言針對數據中心和云計算基礎設施對賽靈思FPGA進行編程。

2017-11-17 16:52:01 3590

3590 一般加速分為兩種,第一是基于ASIC的可以針對特定應用進行加速的專用加速器,另一種是可以降低用戶運營和數據分析成本的通用加速器,FPGA適用于多種場景。 數據在源源不斷產生,數據中心需要越來越多

2018-06-18 10:25:00 5726

5726

應用大比拼開擂 基于vivado HLS的幀差圖像實現 基于FPGA的實時移動目標的追蹤 類似嵌入式 C/C++/OpenCL 應用開發的體驗 SDSoC 開發環境可為異構 Zynq SoC 及 MPSoC 部署

2018-05-21 14:16:00 2572

2572 是賽靈思SDx軟件定義開發環境系列成員之一,包括擴展庫、開發板、設計服務生態系統支持,可實現嵌入式C/C++語言應用開發。該SDSoC?開發環境正式版還強化了集成設計環境(IDE)的功能與特性,讓編程和平臺開發更加簡便容易。

2018-08-21 09:32:00 3084

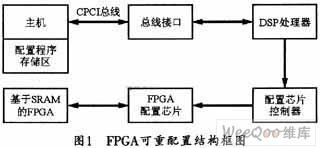

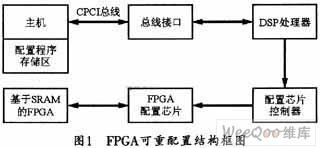

3084 結合對FPGA重配置方案的軟硬件設計,本文通過PC機并通過總線(如PCI總線)將配置數據流下載到硬件功能模塊的有關配置芯片,從而完成配置FPGA的全過程。該方法的軟件部分基于Visual C++的開發環境,并用C++語言開發動態連接庫,以用于軟件設計應用程序部分的調用。

2018-12-30 09:26:00 3644

3644

你既想利用 Android NDK 開發原生 C/C++ Android 應用,又希望在你得心應手的 Visual Studio 中工作?

如今,絕大多數開發人員被迫學習新的開發環境,比如

2019-03-15 15:10:50 2273

2273 、騰訊云、百度云、IBM、Facebook都采用了FPGA加速服務器。人工智能的廣泛應用場景的架構多樣性,可以充分發揮FPGA的優勢和特點,開創新型FPGA在數據中心的新局面。”

2018-11-01 16:47:04 1846

1846 SDAccel編譯器支持OpenCL C,C和C ++,用于定義FPGA執行的內核功能。

了解如何利用用C / C ++編寫的現有函數作為FPGA上運行的OpenCL應用程序的加速內核。

2018-11-20 06:40:00 3371

3371 視頻討論了SDAccel設計環境如何加速RTL加速器與軟件框架的集成,并實現多個IP的快速集成,按鈕驗證,性能調整以及設備之間的可移植性,云

2018-11-20 06:24:00 4575

4575 Xilinx與Nimbix公司合作,Nimbix公司是大數據和機器學習的異構加速器云的領先提供商,利用C / C ++和OpenCL的FPGA計算密度創建下一代應用。

2018-11-29 06:11:00 4077

4077 在本視頻中,Nimbix的首席技術官Leo Reiter討論了使用SDAccel開發環境和Xilinx FPGA卡在Nimbix云加速工作流中實現FPGA開發和運行時間的民主化。

觀看此視頻,了解如何開始使用wi

2018-11-29 06:06:00 2230

2230 面向OpenCL,C和C ++的SDAccel開發環境利用FPGA將數據中心單位功耗性能提升高達25倍。作為SDx系列的成員,SDAccel是首個面向OpenCL,C和C ++進行架構優化的編譯器,并結合了

庫,開發板,可在FPGA上實現類似CPU / GPU的開發運行體驗。

2018-11-27 06:49:00 3680

3680 本視頻演示了SDAccel開發環境在一個標準X86_64位工作站上運行的情況,以展示其為您所帶來的生產力的提升;以及該開發環境對OpenCL,C,C ++等等支持情況。該工作站包含一個

Alpha Data的ADM-PCIE-7V3加速卡。

2018-11-27 06:45:00 2850

2850 本文檔的主要內容詳細介紹的是C++入門教程之C++程序設計的課件資料免費下載主要內容包括了:1. 認識C++2. C++的現狀和發展3. C++程序的一般開發過程4. 簡單的C++程序5. C++程序的構成、書寫6. 集成開發環境

2018-12-07 08:00:00 33

33 本文檔的主要內容詳細介紹的是C++程序設計的基礎知識初步了解C++的資料免費下載包括了:1 認識C++,2 C++的現狀和發展,3 C++程序的一般開發過程,4 簡單的C++程序,5 C++程序的構成、書寫,6 集成開發環境

2019-06-10 08:00:00 25

25 華為云正式發布的FP1 OpenCL實例以賽靈思 SDAccel 2017.1版本為基礎,可以為用戶提供全套軟件驅動。借助這個開發環境,用戶無需RTL設計經驗,就可以使用OpenCL,C和C++等多種高級語言開發所需的加速算法。

2019-07-29 14:10:47 2478

2478 現在正在為數據中心加速和其他高計算強度設計打造第三代 3D IC 突破性技術。一旦這一技術與新一代 CCIX 加速架構和我們的軟件定義 SDAccel 開發環境相結合,將為加速計算、存儲和網絡應用提供一個全新的高密度靈活型平臺。”

2019-07-30 14:08:43 2794

2794 展示了賽靈思 SDAccel 開發環境的運行情況,并演示了一個軟件程序員是如何在OpenCL中捕獲一個應用,并利用 FPGA 對其完成加速的。整個過程中該程序員完全不需要是一個FPGA專家或對賽靈思器件設計流程特別熟悉即可獨立完成。

2019-08-01 11:03:25 2079

2079 Xilinx 已經形成一個聯盟成員的全球生態系統,可提供各種平臺、庫和設計服務幫助全球設計團隊充分利用在其 OpenCL、C 和 C++ 應用中基于 FPGA 的加速。

2019-08-01 09:28:00 2912

2912 SDAccel 開發環境 2015.1 版本新增了調試和特性分析功能,讓基于 Eclipse 的 IDE 變得更簡單易用,可加速 OpenCL、C 和 C++ 內核的開發與部署。此外,新版

2019-08-01 09:22:02 2697

2697

OpenCL、C和C++的SDAccel開發環境,將單位功耗性能提高達25倍,從而利用FPGA實現數據中心應用加速。

2019-08-01 08:45:34 3303

3303 適用于OpenCL,C和C ++的Xilinx SDAccel集成開發環境符合Khronos OpenCL 1.0規范,并包含OpenCL可安裝客戶端驅動程序(ICD)。通過ICD擴展,OpenCL

2019-08-12 11:12:50 3324

3324

FPGA在云端數據中心爆發點在哪里?包朝偉表示,目前Xilinx和Altera已經在數據中心加速卡實現了第一步。

2019-09-04 15:15:16 1085

1085 數據中心邏輯芯片是百億美元市場,低延遲+高吞吐奠定FPGA核心優勢。根據 Intel披露的數據,數據中心領域邏輯芯片市場規模2017年達25億美元,2022 年有望達到80-100億美元。數據中心FPGA主要用在硬件加速,相比GPU,FPGA在數據中心的核心優勢在于低延遲及高吞吐。

2019-10-10 15:00:36 1625

1625 SDSoC? 開發環境可為異構Zynq? 全可編程SoC及MPSoC部署提供類嵌入式 C/C++ 應用的開發體驗,其中包括簡單易用的 Eclipse IDE 和綜合設計環境。SDSoC提供業界

2019-11-12 14:12:08 1796

1796

實現這一編程思想的轉變,是因為 FPGA 借助 OpenCL 實現了編程,程序員只需要通過 C/C++ 添加適當的 pragma 就能實現 FPGA 編程。為了讓您用 OpenCL 實現的 FPGA

2020-07-16 17:58:28 7215

7215

實現這一編程思想的轉變,是因為 FPGA 借助 OpenCL 實現了編程,程序員只需要通過 C/C++ 添加適當的 pragma 就能實現 FPGA 編程。為了讓您用 OpenCL 實現的 FPGA

2020-08-10 17:42:22 932

932

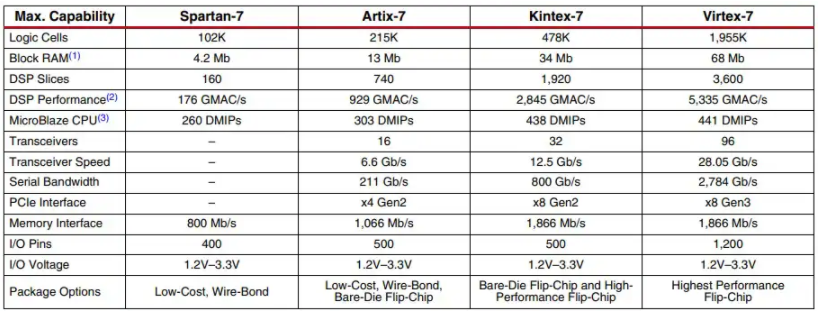

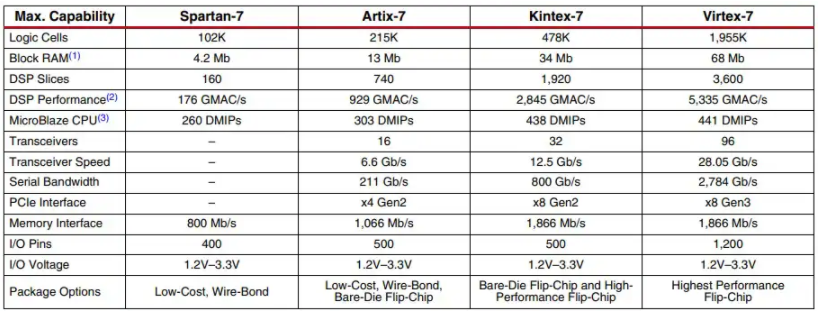

PipeCNN可實現性 PipeCNN論文解析:用OpenCL實現FPGA上的大型卷積網絡加速 2.1 已實現的PipeCNN資源消耗 3. 實現大型神經網絡的方法 4. Virtex-7高端FPGA概覽、7

2021-04-19 11:12:02 3242

3242

本案例介紹了如何使用Silexica的SLX FPGA優化人臉檢測數據中心的OpenCL AI內核。 引言 FPGA正越來越多地被用作數據中心的協處理器。這一轉變背后的驅動力是利用FPGA的并行特性

2021-05-08 14:55:09 2668

2668

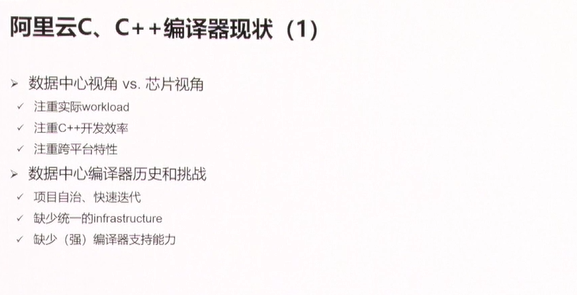

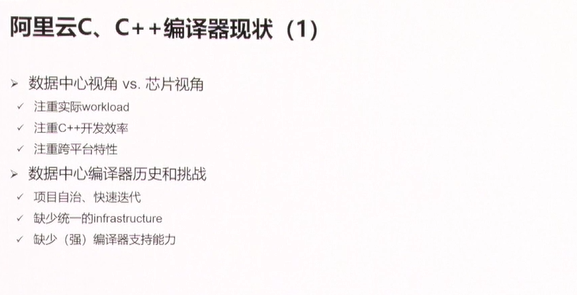

本文主要詳細介紹了阿里云C、C++編譯器(GCC、LLVM)工作現狀、主流編譯器(GCC、LLVM)開源社區參與現狀以及多架構(RISC-V)對數據中心的挑戰。

2021-06-23 15:26:44 3558

3558

一、C++概述1.嵌入式開發中為什么選擇C++語言?(1)面向過程編程的特點C語言特點:C語言是在實踐的過程中逐步完善的 ·沒有深思熟慮的設計過程 ·使用時存在很多“灰色地帶

2021-10-20 20:21:08 16

16 本文簡要介紹了如何在IAR中配置C++開發環境,由于C++的封裝支持,引入面向對象的開發思路可以使得用C++進行單片機獲得更高的開發效率

2021-12-03 11:36:09 4

4 虛擬機的設計與實現:C\C++

2022-02-21 15:10:39 0

0 HLS的FPGA開發方法是只抽象出可以在C/C++環境中輕松表達的應用部分。通過使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 2261

2261

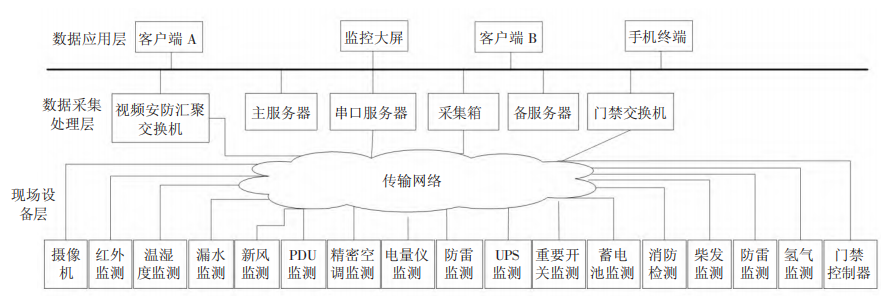

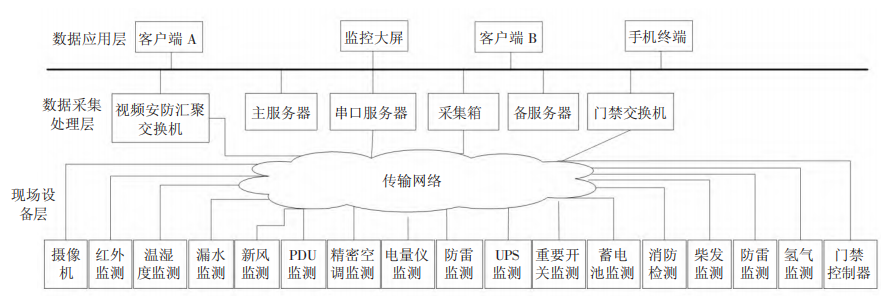

摘 要:結合銀行數據中心建設項目,設計銀行數據中心機房動力環境監控系統,分析銀行數據中心機房監控對象、搭建系統監控架構,給出監控實現方法,*后針對運行一段時間出現的問題,提出優化措施和建議,對同類工程建設具有一定借鑒意義。

2023-04-06 15:31:27 1384

1384

在傳統數據中心部署方案中,計算和數據處理都是由CPU完成,存儲和網絡資源也是圍繞CPU進行部署。然而,由于人工智能和物聯網市場的爆發,云端數據量呈指數級增長,CPU便成為系統規模和效率提升的瓶頸,GPU、FPGA、ASIC等高性能芯片開始涌入數據中心市場,其中FPGA的典型產品形態就是加速卡。

2023-05-20 11:37:51 2422

2422

C++開發人員將有這些問題歸咎于C,而C開發人員則認為C++過于瘋狂。我覺得站在C的角度看C++,這種說法也很正確。作為C的超集,C++確實很瘋狂。一個經驗豐富的C開發人員面對C++可能沒有熟悉的感覺。C++不是C,這就足以引發互聯網上的激烈爭論。

2023-05-26 09:27:47 877

877

電子發燒友網站提供《基于FPGA的數據中心Load Balancer加速解決方案.pdf》資料免費下載

2023-09-13 09:32:07 0

0 FPGA 芯片在數據中心領域主要用于硬件加速,在云服務器廠商中已有廣泛部署。數據中心使用 FPGA 芯片代替傳統的 CPU 方案后,處理其自定義算法時可實現顯著的加速效果。因此近年來,微軟 Azure、亞馬遜 AWS、阿里云的服務器上都開始部署 FPGA 加速器用于運算加速。

2023-11-16 09:55:46 1482

1482

華為云CodeArts IDE 定位華為云開發者桌面 ,是華為云面向開發者提供的一款智能化桌面集成開發環境。CodeArts IDE for C/C++集成了華為自研的C/C++語言服務,并集良好

2023-11-29 17:40:02 1665

1665

函數,可實際上C++中沒有。但是別著急,其實C++中有兩種簡單的方法可以實現類似Java中的instanceof的功能。 在 C++ 中,確定對象的類型是編程中實際需求,使開發人員能夠做出動態決策

2024-07-18 10:16:21 1343

1343

? 再來看一篇FPGA的綜述,我們都知道微軟包括國內的云廠商其實都在數據中心的服務器中部署了FPGA,所以這篇論文就以數據中心的視角,來看下FPGA這個硬件加速器。 還是一樣,想要論文原文的可以私信

2025-01-14 10:29:31 1303

1303

源代碼加密對于很多研發性單位來說是至關重要的,當然每家企業的業務需求不同所用的開發環境及開發語言也不盡相同,今天主要來講一下c++及git開發環境的源代碼防泄密保護方案。企業源代碼泄密場景一、在很多

2025-02-12 15:26:11 973

973

電子發燒友App

電子發燒友App

評論