1.引言

現(xiàn)場可編程門陣列 ( Field programmable gatearrays, FPGA) 是一種可編程使用的信號處理器件,用戶可通過改變配置信息對其功能進行定義, 以滿足設計需求。 與傳統(tǒng)數(shù)字電路系統(tǒng)相比, FPGA 具有可編程、 高集成度、高速和高可靠性等優(yōu)點, 通過配置器件內部的邏輯功能和輸入/輸出端口, 將原來電路板級的設計放在芯片中進行,提高了電路性能,降低了印刷電路板設計的工作量和難度, 有效提高了設計的靈活性和效率。設計者采用 FPGA 的優(yōu)點:

(1) 減少對所需器件品種的需求, 有助于降低電路板的體積重量;

(2) 增加了電路板完成后再修改設計的靈活性;

(3) 設計修改靈活, 有助于縮短產(chǎn)品交付時間;

(4) 器件減少后, 焊點減少,從而可提高可靠度。尤其值得一提的是, 在電路運行頻率越來越高的情況下,采用 FPGA 實現(xiàn)的復雜電路功能減小了板級電路上 PCB 布線不當帶來的電磁干擾問題, 有助于保證電路性能。

FPGA 也是 現(xiàn) 階 段 航 天 專 用 集 成 電 路 (ASIC, Application specificintegrated circuit) 的最佳實現(xiàn)途徑。 使用商用現(xiàn)貨 FPGA 設計微小衛(wèi)星等航天器的星載電子系統(tǒng), 可以降低成本。利用 FPGA 內豐富的邏輯資源, 進行片內冗余容錯設計, 是滿足星載電子系統(tǒng)可靠性要求的一個好辦法。目前,隨著對衛(wèi)星技術的不斷發(fā)展、 用戶技術指標的不斷提高以及市場競爭的日益激烈,功能度集成和輕小型化已經(jīng)成為星載電子設備的一個主流趨勢。 采用小型化技術能夠使星載電子設備體積減小、重量減輕、 功耗降低, 提高航天器承載有效載荷的能力以及功效比。采用高功能集成的小型化器件,可以減小印制板的尺寸, 減少焊盤數(shù)量, 還有利于充分利用冗余技術提高系統(tǒng)的容錯能力。 星載數(shù)字電路小型化的關鍵是器件選用,包括嵌人式高集成度器件的選用,其中, 高密度可編程邏輯器件 FPGA 的選用是一個重要的實現(xiàn)方式。

目前,在航天遙感器的設計中, FPGA 被廣泛地應用于主控系統(tǒng) CPU 的功能擴展CCD 圖像傳感器驅動時序的產(chǎn)生以及高速數(shù)據(jù)采集。本文回顧了 FPGA 的發(fā)展, 分析了其主要結構,并對航天應用 FPGA 進行了綜述。 指出了航天應用對FPGA 及其設計的要求, 重點分析了空間輻射效應對FPGA 可靠性的影響, 并總結了提高 FPGA 抗輻照的可靠性設計方法。 最后, 對航天應用 FPGA 的發(fā)展進行了展望。

2. FPGA航天應用

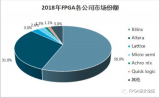

可編程邏輯器件以其設計方便、設計便于修改、功能易于擴展, 在航天、空間領域中得到了越來越廣泛的應用。 一種是以 Actel 公司產(chǎn)品為代表的一次編程反熔絲型 FPGA, 一種是以Xilinx 公司產(chǎn)品為代表的基于 SRAM 的可重新配置的 FPGA。

2.1 航天應用 FPGA 的分類

FPGA 按其編程性, 目前具有航天成功應用經(jīng)驗的 FPGA 主要有兩類: 一類是只能編程一次的一次性編程 FPGA。 另一類是能多次編程的可重編程 FPGA,如 SRAM 型 FPGA、 Flash 型 FPGA, 這類 FPGA 一般具有在系統(tǒng)編程(ISP, In system programming) 能力。

2.1.1一次性編程 FPGA

此類產(chǎn)品采用反熔絲開關元件, 具有體積小、版圖面積小、 低抗輻射抗干擾、 互連線特性阻抗低的特點, 不需要外接 PROM 或 EPROM, 掉電后電路的配置數(shù)據(jù)不會丟失,上電后即可工作, 適用于航天、 軍事、 工業(yè)等各領域。 這類產(chǎn)品中, 具有代表性并已取得航天應用成功經(jīng)驗的產(chǎn)品是 ACTEL 公司的抗輻射加固反熔絲型 FPGA。與傳統(tǒng) FPGA 平面型散布 的 邏 輯 模塊 、 連 線 、開關矩陣的布局不同, 反熔絲型 FPGA 采用緊湊、 網(wǎng)格化密集布局的平面邏輯模塊結構。利用位于上下邏輯模塊層之間、 金屬對金屬的可編程反熔絲內部連接元件實現(xiàn)器件的連接,減小了通道和布線資源所占用的空間。 在編程之前,該連接元件為開路狀態(tài), 編程時, 反熔絲結構局部的小區(qū)域內具有足夠高的電流密度, 瞬間產(chǎn)生較大的熱功耗,融化絕緣層介質形成永久性通路。

2.1.2可重編程 FPGA

此類產(chǎn)品采用 SRAM 或 Flash EPROM 控制的開關元件, 其優(yōu)點是可反復編程。 配置程存放在 FPGA外的存儲器中, 系統(tǒng)上電時, 配置程加載到 FPGA中完成硬件功能的定制化。 其中, SRAM 型 FPGA 還可以在系統(tǒng)運行中改變配置, 實現(xiàn)系統(tǒng)功能的動態(tài)重構。但是, 此類FPGA 掉電后存儲的用戶配置邏輯會丟失, 只能上電后重新由外部存儲器加載。 FlashEPROM 型 FPGA 具 有 非 易 失 性 和 可 重 構 的 雙 重 優(yōu)點, 但不能動態(tài)配置, 功耗也比 SRAM 型FPGA 高。此類 FPGA 由于配置數(shù)據(jù)存儲在 FPGA 內 的 SRAM存儲器中, 可編程邏輯開關采用多路選擇器實現(xiàn),內部邏輯功能采用基于 SRAM 結構的查找表實現(xiàn) ,這些部位都屬于單粒子翻轉效應敏感型半導體結構。因此, 在航天應用中要特別注意。具有代表性的、并取得航天應用成功經(jīng)驗的產(chǎn)品是 Xilinx 公司的基于SRAM 型 Virtex 系列的 FPGA 產(chǎn)品。

2.2 FPGA 航天應用現(xiàn)狀

FPGA 在國內外的航天、 空間領域, 特別是商用衛(wèi)星得到了廣泛的應用。 據(jù)統(tǒng)計,在國內外深空探測、 科學及商用衛(wèi)星共 60 個項目中都用到了 FPGA,軍用衛(wèi)星項目中也有多個項目用到 FPGA。

2.2.1 Acte FPGA 的航天應用

Actel 的耐輻射和抗輻射 FPGA 自從在 1997 年火星探路者 (Mars Pathfinder) 以及隨后的勇氣號、 機遇號任務中取得成功后, 其 FPGA 繼續(xù)用于 NASA、ESA 的火星探測任務。 Actel 的耐輻射和抗輻射器件用于火星探測器的控制計算機,執(zhí)行從地球到火星6 個月飛行的導航功能。 在火星探索者漫游器 (ExplorerRover) 的照相機、 無線通信設備中均采用了 Actel 器件。 ESA 的火星快車軌道衛(wèi)星中, 固態(tài)記錄器使用了 20 多個 Actel FPGA 器件。Actel 公 司的 FPGA 器 件 已 用 于 德 國 航 天 領 域 (DLR) 雙光譜紅外探測 (BIRD) 衛(wèi)星中。 BIRD 是全球首個采用紅外傳感器技術的衛(wèi)星, 以探測和研究地球上的高溫事件,如森林山火、 火山活動、油井和煤層燃燒等。 超過 20 個高可靠性 FPGA 用干衛(wèi)星有效載荷數(shù)據(jù)處理、 存儲器管理、 接口和控制、 協(xié)處理以及紅外攝影機的傳感器控制等多個關鍵性功能中。

2.2.2 Xilinx FPGA 的航天應用

同 ACTEL 相比, Xilinx 公司用于航天、 空間領域的產(chǎn)品研制較晚, 但是, 其功能強大、性能高、可重新配置的民用塑封產(chǎn)品向宇航級產(chǎn)品的過渡、全面提高抗空間輻射能力,逐漸成為空間電子產(chǎn)品設計中常用的 FPGA 產(chǎn)品, 并將獲得越來越廣泛的應用。

Xilinx 的 Virtex 耐輻射 FPGA 被用于 2003 年發(fā)射的澳大利亞的軍民混用通信衛(wèi)星 Optus CL, 在衛(wèi)星的 UHF 有效載荷中, XilinxVirtex FPGA (XQVB300)用來實現(xiàn)地球數(shù)據(jù)的信號處理算法,并使用了 Xilinx提供的 IP 核。

Xilinx 的加固 FPGA XQR4062XL 被用于 2002 年發(fā)射的澳大利亞科學衛(wèi)星 Fedsat (聯(lián)合衛(wèi)星, 用于研究磁層) 的高性能計算有效載荷。 HPC-1 是第一例在星載計算機系統(tǒng)的標準運行中采用 FPGA 實現(xiàn)了可配置計算技術 RCT。 目前正在開發(fā)的 RHC-II 將使用Xilinx FPGA 實現(xiàn)星上數(shù)據(jù)處理。

此外 , GRACE ( NASA) 的 敏 感 器 中 使 用 了XQR4O36XL 產(chǎn)品。

在火星探測漫游器Discovery 和 Spirit 中都成功應用了 Xilinx FPGA 產(chǎn)品。 兩片宇航 FPGA VirtexTMFPGA XQVR100O 被用于火星漫游器車輪電機控制、機械臂控制和其他儀表中, 4 片耐輻照 4000 系列的FPGA XQR4062XL 用于控制火星著陸器的關鍵點火設備, 保證著陸器按規(guī)定程序下降及成功著陸。歐洲第一個彗星軌道器和著陸器 ROSETTA 上總共有 45 片 FPGA,都選用 ACTEL RT14I00A, 承擔了控制、 數(shù)據(jù)管理、 電源管理等重要功能, 并且飛行中任何一片 FPGA 都不得斷電。

Xilinx 最新發(fā)布的 Virtex-5QVFPGA 具有非常高的抗輻射性, TID 耐性為 700 kraD 以上,SEU (Sin-gle Event Upset, 單粒子翻轉) 閂鎖 (Latch Up) 耐性超過 100 MeV·cM2/Mg,主要面向人造衛(wèi)星和宇宙飛船上的遙感處理、圖像處理以及導航儀等用途。 因此,基于 FPGA 系統(tǒng)構成無需為了輻射措施而增加冗余,可以削減系統(tǒng)開發(fā)所需要的時間和成本。其規(guī)模也達到了 13 萬個邏輯單元, 集成了最高速度為 3.125 Gbit/s的高速收發(fā)器, 并強化了 DSP 功能,作為航天領域用 FPGA 中屬業(yè)界最高水準。

3. 輻射效應及其影響

航天、空間電子設備由于其所處的軌道以及使用環(huán)境的不同, 受到的輻射影響也不相同。 從總體上來說, 對 FPGA 影響比較大的輻射效應主要有: 總劑量效應 ( TID: Total ionizing Dose)、 單粒子翻轉 (SEU: Single event upset)、單 粒 子 閂 鎖 ( SEL: Single event latchup)、單粒子功能中斷 ( SEFI: Single eventfunc-tional interrupt) 、 單 粒 子 燒 毀 ( SEB: Single eventburnout)、單 粒 子 瞬 態(tài) 脈 沖 ( SET: Single event tran-射效應產(chǎn)生的機理不盡相同, 引起 FPGA 的失效形式也不同。

總劑量效應:光子或高能離子在集成電路的材料中電離產(chǎn)生電子空穴對, 最終形成氧化物陷阱電荷或者在氧化層與半導體材料的界面處形成界面陷阱電荷,使器件的性能降低甚至失效。

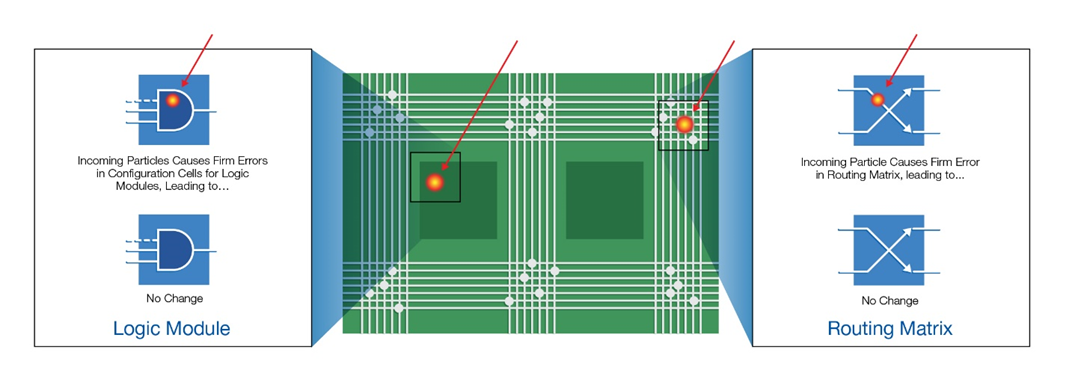

單粒子翻轉:具有一定能量的重粒子與存儲器件或邏輯電路 PN 結發(fā)生碰撞, 在重粒子運動軌跡周圍形成的電荷被靈敏電極收集并行成瞬態(tài)電流, 如果電流超過一定值就會觸發(fā)邏輯電路, 形成邏輯狀態(tài)的翻轉。 單粒子翻轉敏感區(qū)域是指 FPGA 中易于受到單粒子效應影響的區(qū)域, 包括FPGA 的配 置 存 儲 器 、DCM、 CLB、 塊存儲區(qū)域。

單粒子閂鎖: CMOS 器件的 PNPN 結構成了可控硅結構。 質子或重粒子的入射可以觸發(fā)PNPN 結導通, 進入大電流再生狀態(tài), 產(chǎn)生單粒子閂鎖。 只有降低電源電壓才能退出閂鎖狀態(tài)。

單粒子功能中斷:質子或重粒子入射時引起器件的控制邏輯出現(xiàn)故障, 進而中斷正常的控制功能。FPGA 中單粒子功能中斷的敏感部分為配置存儲器、上電復位電路、 SelectMAP 接口和JATAG 接口。

單粒子燒毀:入射粒子產(chǎn)生的瞬態(tài)電流導致敏感的寄生雙極結晶體管導通。 雙極結晶體管的再生反饋機制造成收集結電流不斷增大,直至產(chǎn)生二次擊穿, 造成漏極和源極的永久短路,燒毀電路。 FPGA發(fā)生單粒子燒毀的概率較小。

單粒子瞬態(tài)脈沖:帶電粒子入射產(chǎn)生的瞬態(tài)電流脈沖影響到下一級邏輯電路的輸入, 造成該邏輯電路輸出紊亂。單粒子瞬態(tài)脈沖可能引起 FPGA 內部邏輯電路的短時錯誤。 單粒子瞬態(tài)脈沖對于<0.25 μM 工藝的 FPGA 影響較大。

位移損傷:單粒子位移損傷是單個粒子入射引起晶格原子移位、 形成缺陷群、引起的永久性損傷。

上述輻射效應對 FPGA 造成的影響有的是永久性的, 如總劑量效應、 單粒子燒毀、 位移損傷; 有的是能夠恢復的, 如單粒子翻轉、 單粒子功能中斷、 單粒 子 瞬 態(tài) 脈 沖 。 以 上 單粒 子 效 應 中 SEL、 SEB 和SEGR 均有可能對器件造成永久性損傷。 因此,一般星上系統(tǒng)都會采用抗 SEL 的器件。 SEU 和 SET 雖然是瞬時影響,但其發(fā)生率遠高于以上 3 種, 反而更應引起重視。 接下來根據(jù)對上述輻射影響的分析, 研究提高 FPGA 抗輻射效應的可靠性設計方法。

隨著 SRAM 型的 FPGA 隨 著 工 藝 水 平 的 提 高 、規(guī)模的增大和器件核電壓的降低,抗總劑量效應性能不斷提高, 但是更容易受 SEU 和 SET 的影響。

針對 單 粒 子 效 應 的 問 題 , MAPLD、 NSREC、RADECS 會議提交的報告認為, Virtex-II 系列產(chǎn)品抗總 劑 量 輻 射 能 力 達 到 200 krad, 抗 SEL 的 能力 為LET 160 MeV·cm /mg 以下無閂鎖, 同時, 需要考慮SEU、 SET、 SEFL 等單粒子效應

4. 航天應用

FPGA 的可靠性設計在航天、空間電子設備中, FPGA 主要用于替換標準邏輯, 還用于 SOC 技術, 提供嵌人式微處理器、存儲器、 控制器 、 通信接口等 。 其中 , 可靠性是FPGA 設計的主要需求。

根據(jù)功能及其重要性的不同,空間電子系統(tǒng)設計分為關鍵與非關鍵兩大類, 航天器控制為關鍵類,科學儀表為非關鍵類。航天器控制系統(tǒng)對 FPGA 的一般需求: 高可靠、 抗輻射加固和故障安全。 科學儀器對 FPGA 的設計要求一般為高性能、 耐輻射和失效安全, 其可靠性則是由性能需求決定的,對 FPGA 的需求也因系統(tǒng)而異, 如測量分辨率、 帶寬、 高速存儲、 容錯能力等。

航天用 FPGA 的可靠性設計主要通過器件自身的硬件設計以及軟件設計來實現(xiàn)。

4.1 FPGA

的硬件可靠性設計FPGA 的硬件可靠性設計主要是針對空間輻射效應的影響, 借助制造工藝和設計技術較為徹底地解決了單粒子效應防護問題。一般從以下幾個方面進行設計: FPGA 整體設計加固、 內部設計間接檢測輻射效應的自檢模塊、引入外部高可靠性的監(jiān)測模塊。

整體加固設計是指在電子設備的外面采用一定厚度的材料進行整體輻射屏蔽,減少設備所受的輻射效應, 經(jīng)常采用的材料有鋁、 鉭和脂類化合物等。這種方法在航天電子元器件中使用較多, 也比較成熟。例如, 作為美國軍用微電子產(chǎn)品主要供應商的Honeywell, 加固 ASIC 技術覆蓋范圍寬。 Aeroflex 采用 “設計加固、商用 IC 工藝線流片” 的方式提供性能先進的加固ASIC 產(chǎn)品, 具備數(shù)模混合加固 ASIC的研制能力。 這種采用商業(yè)線流片生產(chǎn)軍用和加固微電子產(chǎn)品的技術線路,既有利于擺脫工藝加固對器件發(fā)展的約束, 又有利于滿足用戶對先進加固器件的需求, 降低成本,縮短供貨時間。

Atmel 為用戶提供了高性能、 小尺寸、 低功耗的各類器件的工藝資源, 包括用于航天的耐輻照高速、低功 耗 數(shù) 模 混 合 CMOS 工 藝以 及 內 嵌 EEPROM 的CMOS 工藝。 國內從事軍用微電子器件研制的單位很多,包括國有科研單位和非國有 IC 研制公司。 但是,能夠完成抗輻照加固 IC 研制的單位并不多。 國內自行研制的加固 ASIC 產(chǎn)品已經(jīng)在衛(wèi)星中得到了成功應用。

采用體硅外延層,也可以防止發(fā)生 SEI。 例如, Xilinx 的 virtex-II 耐輻射產(chǎn)品是在軍品等級器件的基礎上進一步采用外延襯底設計,抗總劑量電離效應能力按照 MIL-STD-883 Method 1019進行批次采樣考核。自檢模塊的目的是通過某些模塊的正常運行來預測整個 FPGA 運行的正常性。 自檢模塊由分布在FPGA 重要布線區(qū)域附近的簡單邏輯電路實現(xiàn), 也可以由多模冗余模塊表決結果或者余數(shù)檢測法以及奇偶校驗法等其他產(chǎn)生的結果直接提供輸出。

4.2 FPGA 的軟件可靠性設計航天應用

FPGA 的軟件可靠性設計是指應用軟件程序配置來屏蔽輻射效應造成的運行失常。其中,冗余設計方法是被公認為比較可靠的對付輻射效應的方法。 常用的冗余設計有三模冗余法(TMR, Triplemoduleredundancy) 和部分三模冗余法 (PTMR, Partialtriple module redundancy)。 雖然 TMR 能夠提高系統(tǒng)的可靠性, 但也會使模塊速度降低、 占用資源和功率增加。 綜合考慮其他設計指標, 可以根據(jù)實際情況對關鍵部分使用部分三模冗余法。

冗余結構盡管可以保證系統(tǒng)可靠性,但卻不能及時發(fā)現(xiàn)并糾正錯誤, 或為發(fā)現(xiàn)錯誤而引入了過多的組合邏輯,當應用于 FPGA 時, 增加了容錯電路自身出錯的可能性。除此之外, 星載系統(tǒng)無人值守的運行特點使得系統(tǒng)重構與故障恢復也非常困難。

對配置存儲器的回讀校驗和重配置(或局部重配置) 是一種有效的抵抗輻射效應的方法, 通過對部分配置的重加載能夠修復 SEU 效應造成的影響, 其頻率應是最壞情況 SEU 效應發(fā)生率的10 倍。 在重加載邏輯設計中, 需要對重加載的實現(xiàn)方式、 加載內容進行仔細設計, 并不是所有的內容都可以重加載,也不是所有的內容都需要重新配置。

在系統(tǒng)設計中,采用高可靠性的反熔絲 FPGA負責從非易失大容量存儲器中讀取 Xilinx FPGA 的配置數(shù)據(jù)對其進行配置。 在運行期間, 對最容易受輻射效應影響的配置存儲器按列進行讀操作, 然后與標準數(shù)據(jù)進行比對, 對出現(xiàn)錯誤的列進行局部重配置。

FPGA的可編程IO也容易受到輻射粒子影響產(chǎn)生 SEU 和 SEL。 對輸入輸出腳設計三模冗余設計方法是一種非常有效方法,但是這種方法將需要占用 3 倍的 I/O 資源。 如果 SET 作用在時鐘電路或者其他數(shù)據(jù)、 控制線上容易產(chǎn)生短脈沖抖動, 有可能會造成電路的誤觸發(fā)或者數(shù)據(jù)鎖存的錯誤,在設計時可采用同步復位設計內部復位電路、控制線使能信號線, 邏輯數(shù)據(jù)在鎖存時盡可能配合使能信號。

5.FPGA航天應用發(fā)展趨勢

目前,在深微亞米半導體工藝下, 傳統(tǒng)的 FPGA設計技術在器件良率、 功耗、 互聯(lián)線延時、信號完整性、 可測性設計等方面面臨挑戰(zhàn)[9]。 基于傳統(tǒng)技術的 FPGA 仍然在向高密度、 高性能、 低功耗的方向發(fā)展, 使得 FPGA 從最開始的通用型半導體器件向平臺化的系統(tǒng)級器件發(fā)展。 基于異步電路的 FPGA 設計、3D 集成技術、 新型半導體結構的應用將是 FPGA 技術發(fā)展的熱點。

航天、空間應用方面, 國外航天對 FPGA 空間應用的總結和預測分析表明, 空間應用對 FPGA 選用呈現(xiàn)出以下趨勢:

(1) 器件工作電壓從 5 V 變?yōu)?3.3 V、 2.5 V 甚至l.8 V;

(2)從使用總劑量加固 FPGA 發(fā)展到使用耐總劑量 FPGA產(chǎn)品;

(3) 從 SEU 敏感寄存器 FPGA 的應用發(fā)展為使用內建寄存器 TMR 結構的 FPGA;

(4) 從只使用一次編程的反熔絲型FPGA 發(fā)展為使用基于SRAM/EEPROM 的可重置型FPGA。

這種選用趨勢帶來的突出問題是:從寄存器對SEU 敏感變?yōu)?FPGA 對 SEU 敏感;配置存儲 FPGA的設計復雜性已經(jīng)同 ASIC 的復雜程度相當。

6.結論

本文對航天應用中FPGA的使用進行了綜述。分析了FPGA的結構特點, 針對航天、空間環(huán)境的輻照條件,分析了航天應用FPGA的失效模式及可靠性設計方法。 最后,對航天應用FPGA及其可靠性設計技術的發(fā)展進行了展望。

電子發(fā)燒友App

電子發(fā)燒友App

評論