最近是IC相關專業學生找工作的高峰期,大家可以在文章末尾或者知識星球留言討論筆試或者面試題哦。跨時鐘域的處理在面試中常常被問到,今天IC君就來聊一聊這個話題。

2018-09-25 09:39:09 8323

8323 跨時鐘域通俗地講,就是模塊之間有數據交互,但是模塊用的不是同一個時鐘進行驅動。

2020-10-08 17:00:00 3185

3185

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。 在本篇文章中,主要

2020-11-21 11:13:01 4997

4997

跨時鐘域路徑分析報告分析從一個時鐘域(源時鐘)跨越到另一個時鐘域(目標時鐘)的時序路徑。

2020-11-27 11:11:39 6743

6743

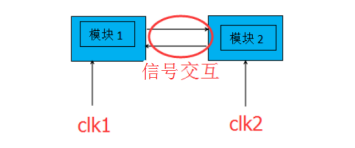

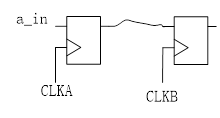

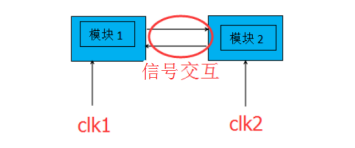

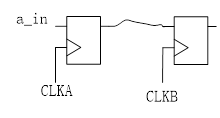

1、跨時鐘域與亞穩態 跨時鐘域通俗地講,就是模塊之間有數據交互,但是模塊用的不是同一個時鐘進行驅動,如下圖所示: 左邊的模塊1由clk1驅動,屬于clk1的時鐘域;右邊的模塊2由clk2驅動,屬于

2020-10-16 15:47:45 1451

1451

假如考慮處理器和存儲器的工作頻率為500MHz,帶有存儲器控制器的浮點引擎的工作頻率為666.66MHz,總線接口和高速接口工作頻率為250MHz,則該設計具有多個時鐘,被視為多個時鐘域的設計。

2022-07-12 11:59:02 2327

2327

假如考慮處理器和存儲器的工作頻率為500MHz,帶有存儲器控制器的浮點引擎的工作頻率為666.66MHz,總線接口和高速接口工作頻率為250MHz,則該設計具有多個時鐘,被視為多個時鐘域的設計。

2022-08-01 18:07:51 1507

1507

我在知乎看到了多bit信號跨時鐘的問題,于是整理了一下自己對于跨時鐘域信號的處理方法。

2022-10-09 10:44:57 8118

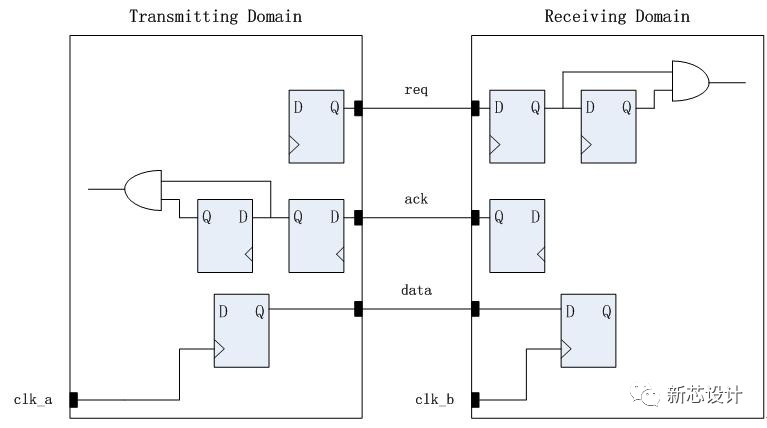

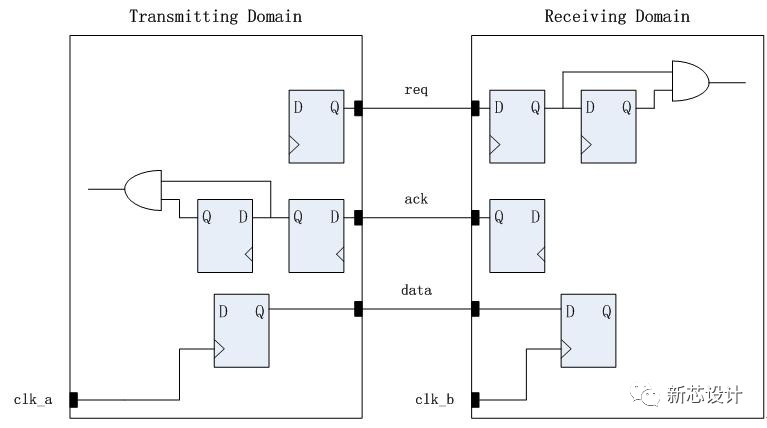

8118 對于多位寬數據,我們可以采用握手方式實現跨時鐘域操作。該方式可直接使用xpm_cdc_handshake實現,如下圖所示。

2023-05-06 09:22:16 2101

2101

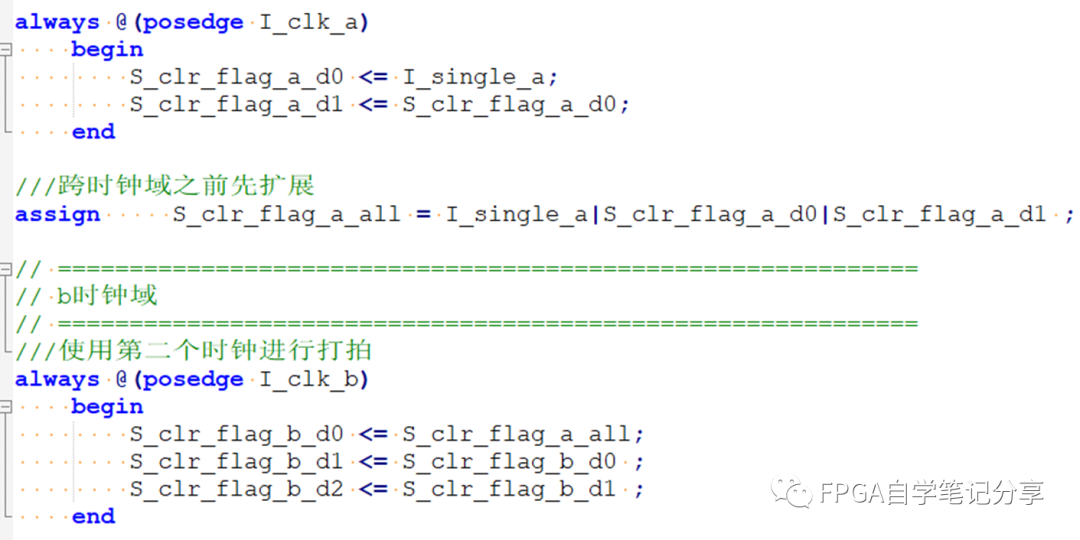

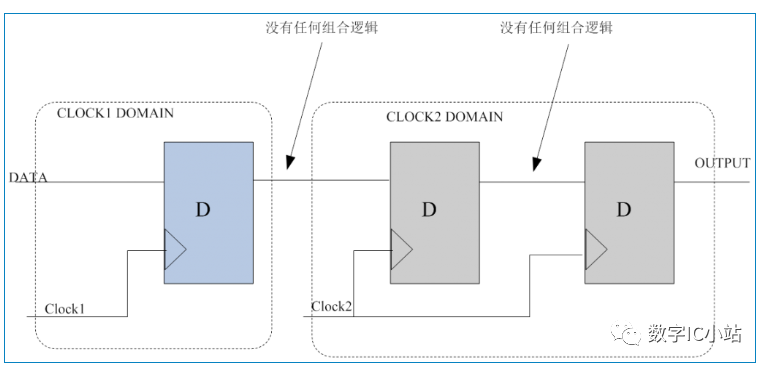

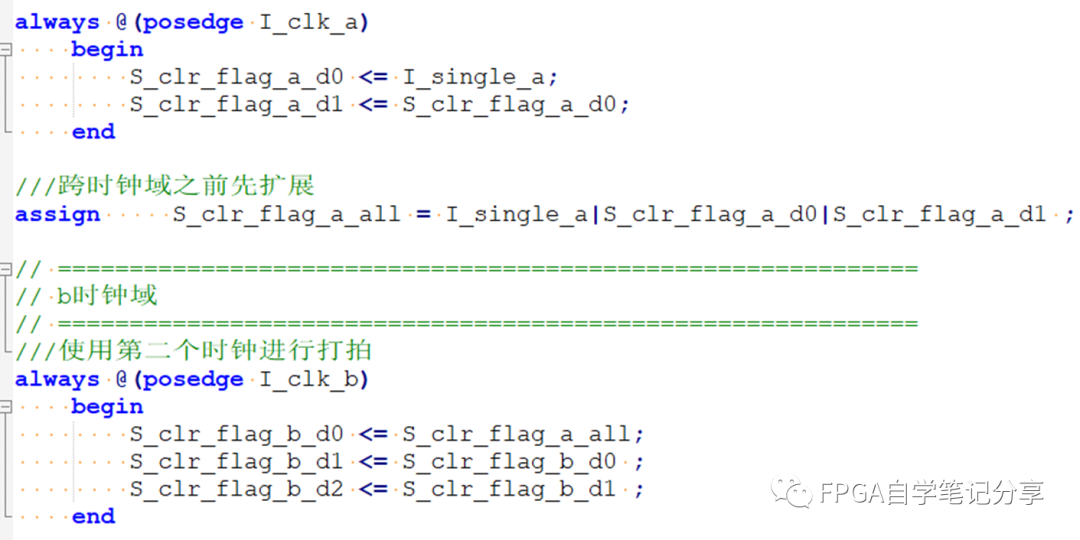

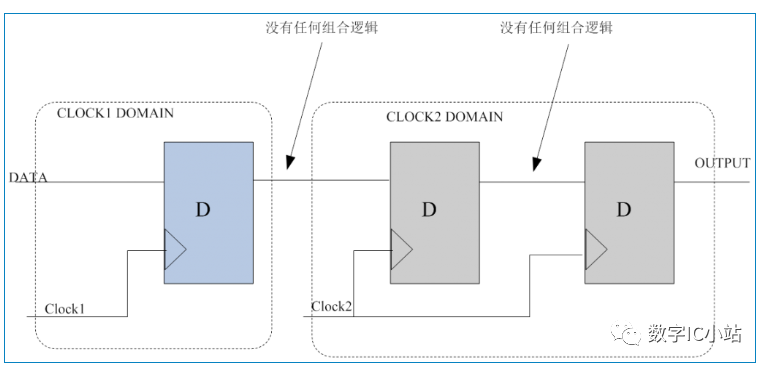

跨時鐘域之間不能存在組合邏輯。 跨時鐘域本身就容易產生亞穩態,如果在跨時鐘域之間存在組合邏輯會大大增加競爭冒險出現的概率。 這一點在實際設計中通常會因為粗心而導致設計異常,如下邊代碼中

2023-05-24 15:11:32 1427

1427

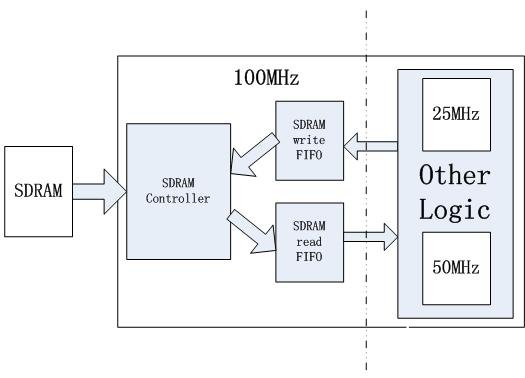

在很久之前便陸續談過亞穩態,FIFO,復位的設計。本次亦安做一個簡單的總結,從宏觀上給大家展示跨時鐘域的解決方案。

2024-01-08 09:42:26 1702

1702

單片機內部結構分析存儲器的工作原理

2021-02-04 07:46:15

單片機內部結構分析存儲器的工作原理

2021-02-04 07:51:10

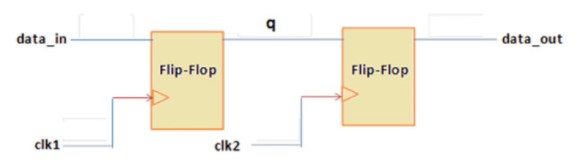

出現了題目中的跨時鐘域的同步問題?怎么辦?十年不變的老難題。為了獲取穩定可靠的異步時鐘域送來的信號,一種經典的處理方式就是雙寄存器同步處理(double synchronizer)。那為啥要雙寄存器呢

2020-08-20 11:32:06

解釋了什么時候要用到FALSE PATH: 1.從邏輯上考慮,與電路正常工作不相關的那些路徑,比如測試邏輯,靜態或準靜態邏輯。 2. 從時序上考慮,我們在綜合時不需要分析的那些路徑,比如跨越異步時鐘域

2018-07-03 11:59:59

DDS的原理及特點是什么?AD9851的工作原理及特性是什么?AD9851在跳頻通信中的應用是什么?

2021-05-28 06:00:09

(10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

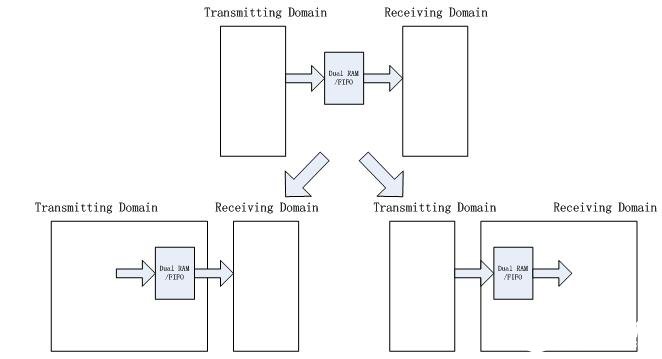

第三級寄存器,由于第二級寄存器對于亞穩態的處理已經起到了很大的改善作用,第三級寄存器在很大程度上可以說只是對于第二級寄存器的延拍,所以意義是不大的。02方法二:異步雙口RAM處理多bit數據的跨時鐘域,一般

2021-03-04 09:22:51

控制器總線接口高速接口假如考慮處理器和存儲器的工作頻率為500MHz,帶有存儲器控制器的浮點引擎的工作頻率為666.66MHz,總線接口和高速接口工作頻率為250MHz,則該設計具有多個時鐘,被視為多個

2022-06-24 16:54:26

方式邊界對齊的數據存放方法主存的基本結構和工作過程存儲系統的層次結構半導體存儲器靜態MOS存儲器 SRAM靜態MOS存儲單元靜態MOS存儲器的結構動態MOS存儲器 DRAM四管動態MOS存儲元的工作原理

2021-07-28 07:59:20

雙口RAM如何實現跨時鐘域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

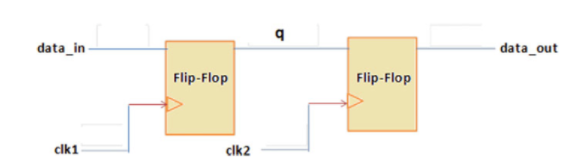

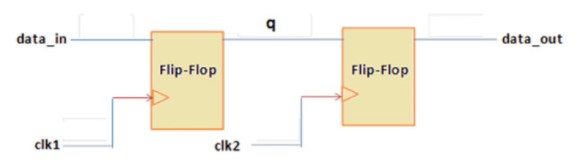

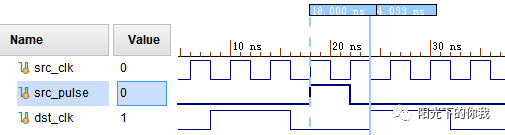

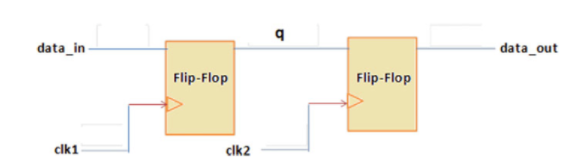

單bit數據的跨時鐘域問題。 打兩拍的方式,其實說白了,就是定義兩級寄存器,對輸入的數據進行延拍。如下圖所示。 應該很多人都會問,為什么是打兩拍呢,打一拍、打三拍行不行呢? 先簡單說下兩級

2021-01-08 16:55:23

第三級寄存器,由于第二級寄存器對于亞穩態的處理已經起到了很大的改善作用,第三級寄存器在很大程度上可以說只是對于第二級寄存器的延拍,所以意義是不大的。02方法二:異步雙口RAM處理多bit數據的跨時鐘域,一般

2021-02-21 07:00:00

異步bus交互(一)— 兩級DFF同步器跨時鐘域處理 & 亞穩態處理1.問題產生現在的芯片(比如SOC,片上系統)集成度和復雜度越來越高,通常一顆芯片上會有許多不同的信號工作在不同的時鐘頻率

2022-02-17 06:34:09

串行通信中的IIC總線工作原理51本身不帶IIC總線 ,使用程序模擬IIC通信協議常用的串行總線協議UART、1-wire、I2C和SPI總線UART:是以異步方式進行通信(一條數據輸入線,一條

2021-12-08 07:52:26

關于cdc跨時鐘域處理的知識點,不看肯定后悔

2021-06-21 07:44:12

單片機內部存儲結構分析存儲器的工作原理半導體存儲器的分類

2021-04-02 07:01:26

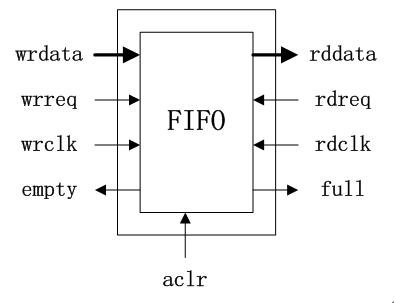

沒有順序關系的控制信號。但是不能使用同步器來同步數據信號,因為會采樣到錯誤數據。在時鐘域之間同步數據的兩種常用方法是:(1)使用握手信號在時鐘域之間傳遞數據(2)使用FIFO(先進先出存儲器)。

2022-04-11 17:06:57

CPU之間怎么進行通信?FIFO的工作原理是什么?如何利用多端口存儲器設計多機系統?

2021-05-26 07:04:50

跨時鐘域處理是什么意思?如何處理好跨時鐘域間的數據呢?有哪幾種跨時鐘域處理的方法呢?

2021-11-01 07:44:59

數據的跨時鐘域問題。打兩拍的方式,其實說白了,就是定義兩級寄存器,對輸入的數據進行延拍。如下圖所示。應該很多人都會問,為什么是打兩拍呢,打一拍、打三拍行不行呢?先簡單說下兩級寄存器的原理:兩級寄存

2020-09-22 10:24:55

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。在本篇文章中,主要

2021-07-29 06:19:11

數據的跨時鐘域問題。打兩拍的方式,其實說白了,就是定義兩級寄存器,對輸入的數據進行延拍。如下圖所示。應該很多人都會問,為什么是打兩拍呢,打一拍、打三拍行不行呢?先簡單說下兩級寄存器的原理:兩級寄存

2020-10-20 09:27:37

邏輯出身的農民工兄弟在面試時總難以避免“跨時鐘域”的拷問,在諸多跨時鐘域的方法里,握手是一種常見的方式,而Stream作為一種天然的握手信號,不妨看看它里面是如做跨時鐘域的握手

2022-07-07 17:25:02

1、跨時鐘域信號的約束寫法 問題一:沒有對設計進行全面的約束導致綜合結果異常,比如沒有設置異步時鐘分組,綜合器對異步時鐘路徑進行靜態時序分析導致誤報時序違例。 約束文件包括三類,建議用戶應該將

2022-11-15 14:47:59

【眾想】大黃蜂STM32視頻教程----劉洋邊講邊寫外設篇3-CAT24WCxx存儲器工作原理http://www.stmcu.org/module/forum/thread-607050-1-1.html

2016-08-01 16:50:02

詳細介紹了AD公司最新推出的一種數字信號發送芯片AD6623的內部結構和工作原理,給出了一種將其應用在多模式通信中的應用方案.

2009-04-24 16:31:32 32

32 關鍵詞 GPRS、DTU、路由器摘要 本本文重點講述跨網關通信中關路由器和 DTU 的設置

2009-11-05 14:47:34 13

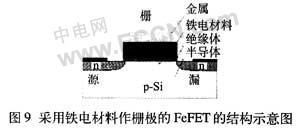

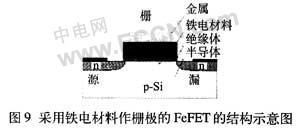

13 鐵電存儲器工作原理和器件結構

?

1 鐵電存儲器簡介

隨著IT技術的不斷發展,對于非易失性存儲器的需求越來越大,讀寫速度

2009-10-25 09:59:50 13010

13010

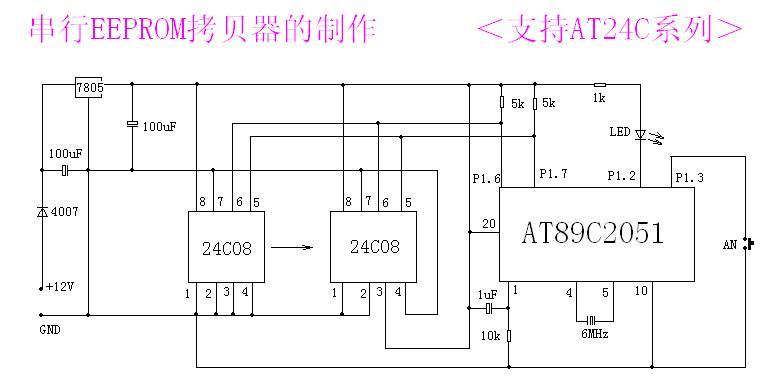

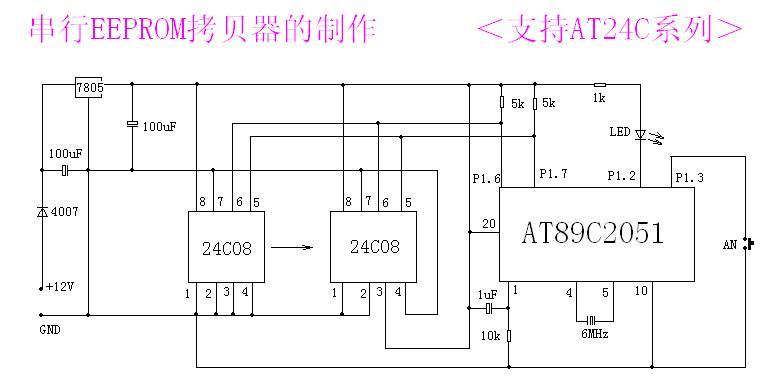

串行存儲器拷貝器的工作原理及制作

匯編源程序 ORG 0000H LJMP MAIN ORG 002DHMAIN:MOV SP,#40H MOV 34H,#0FFH

2009-12-26 17:53:46 1849

1849

廣色域電視,廣色域電視工作原理是什么?

前言 液晶顯示器憑借輕薄時尚的外觀以及健康無輻射的特點,正

2010-03-27 15:18:03 1660

1660 介紹了摻餌光纖放大器的工作原理和它在光通信中的應用,重點分析了EDFA適合在1.54腳n 處的光信號放大,并展望了EDFA的發展前景。

2011-11-23 15:54:38 58

58 跨時鐘域信號的同步方法應根據源時鐘與目標時鐘的相位關系、該信號的時間寬度和多個跨時鐘域信號之間的時序關系來選擇。如果兩時鐘有確定的相位關系,可由目標時鐘直接采集跨

2012-05-09 15:21:18 63

63 跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還在校的本科生,跨時鐘域處理也是面試中經常常被問到的一個問題。 在本篇文章中,主要

2017-11-15 20:08:11 14725

14725 這一章介紹一下CDC也就是跨時鐘域可能存在的一些問題以及基本的跨時鐘域處理方法。跨時鐘域的問題主要存在于異步

2017-11-30 06:29:00 8600

8600

基于FPGA的數字系統設計中大都推薦采用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經常不可避免。如果對跨時鐘域

2018-09-01 08:29:21 6010

6010

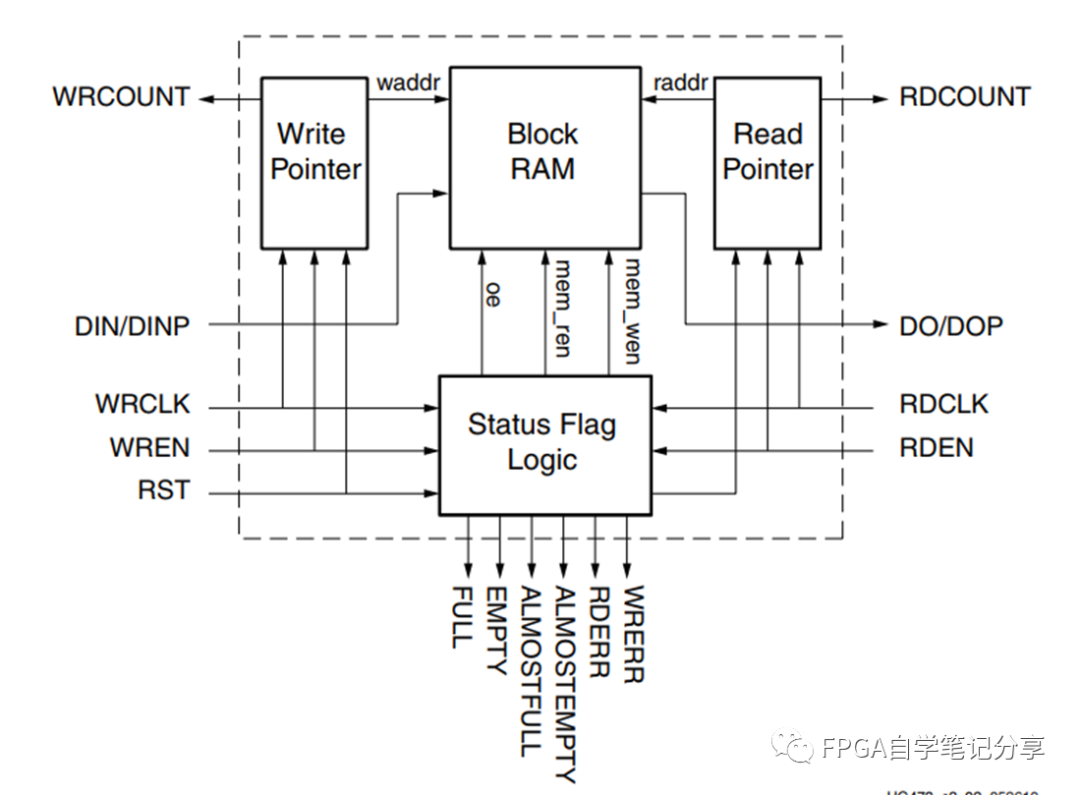

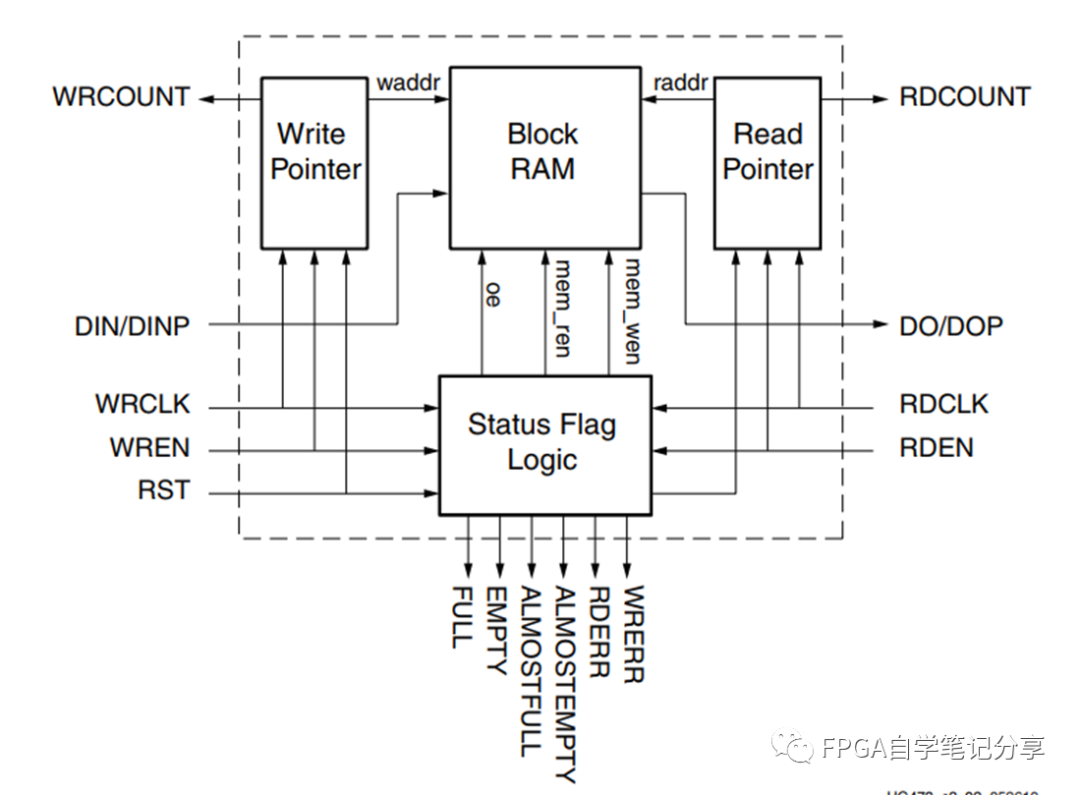

跨時鐘域的問題:前一篇已經提到要通過比較讀寫指針來判斷產生讀空和寫滿信號,但是讀指針是屬于讀時鐘域的,寫指針是屬于寫時鐘域的,而異步FIFO的讀寫時鐘域不同,是異步的,要是將讀時鐘域的讀指針與寫時鐘域的寫指針不做任何處理直接比較肯定是錯誤的,因此我們需要進行同步處理以后進行比較。

2018-09-05 14:29:36 6636

6636 半導體存儲器是數字系統特別是計算機系統中的重要組成,分為RAM和ROM兩大類。學習半導體存儲器的組成結構、工作原理及其應用。

2018-10-17 08:00:00 0

0 了解使用帶存儲器接口的時鐘的最常見問題。

這將涵蓋LVDS時鐘的抖動,時鐘共享和AC耦合。

2018-11-27 06:50:00 3501

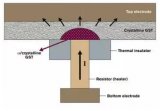

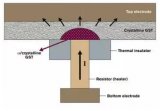

3501 代表的多種新型存儲器技術因具備高集成度、低功耗等特點而受到國內外研究者的廣泛關注,本文介紹相變存儲器的工作原理、技術特點及其國內外最新研究進展。 一、相變存儲器的工作原理 相變存儲器(Phase Change Random Access Memo

2019-03-19 15:43:01 10827

10827

1、存儲器構造 存儲器就是用來存放數據的地方。它是利用電平的高低來存放數據的,也就是說,它存放的實際上是電平的高、低,而不是我們所習慣認為的1234這樣的數字,這樣,我們的一個謎團就解開了,計算機也

2019-05-20 15:48:57 42541

42541 跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現象。在FPGA領域,互動的異步時鐘域的數量急劇增加。通常不止數百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 3895

3895 跨時鐘域處理是 FPGA 設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個 FPGA 初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。 這里主要介紹三種

2022-12-05 16:41:28 2398

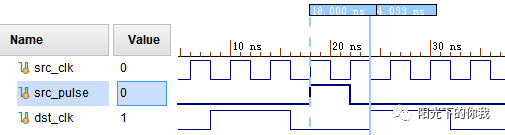

2398 ,基本原理就是把脈沖信號進行展寬。 脈沖同步器應用場景: 適用單bit脈沖信號跨時鐘域。慢到快,快到慢均可,源脈沖間隔至少要為2個目的時鐘周期,否則會被漏采。當然,在慢到快時鐘比率大于2倍以上時也是可以實時采樣的。 脈沖同步器原理框圖:

2021-03-22 09:54:50 4212

4212 總線半握手跨時鐘域處理 簡要概述: 在上一篇講了單bit脈沖同步器跨時鐘處理,本文講述控制信號基于脈沖同步機制的總線單向握手跨時鐘域處理。由于是單向握手,所以比全握手同步效率高一些。 總線半握手

2021-04-04 12:32:00 3675

3675

每一個做數字邏輯的都繞不開跨時鐘域處理,談一談SpinalHDL里用于跨時鐘域處理的一些手段方法。

2021-04-27 10:52:30 4984

4984

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。 在本篇文章中,主要

2021-09-18 11:33:49 23260

23260

(10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 存儲器是現代信息技術中用于保存信息的記憶設備,其概念很廣,有很多層次,在數字系統中,只要能保存二進制數據的都可以是存儲器;在集成電路中,一個沒有實物形式的具有存儲功能的電路也叫存儲器,如RAM

2022-02-07 10:43:26 10619

10619 每一個做數字邏輯的都繞不開跨時鐘域處理,談一談SpinalHDL里用于跨時鐘域處理的一些手段方法。

2022-07-11 10:51:44 2797

2797 時鐘域clock domain:以寄存器捕獲的時鐘來劃分時鐘域。

單時鐘域single clock domain,數據發送和接收是同一個時鐘

多時鐘域multiple clock domain,數據發送和接收是不是同一個時鐘

2022-08-29 15:11:21 3317

3317 ,這是個什么地方呢?這個地方就是單片機內部的只讀存儲器即ROM(READ ONLY MEMORY)。為什么稱它為只讀存儲器呢?剛才我們不是明明把兩個數字寫進去了嗎?

2022-10-10 10:13:45 1804

1804 存儲器是用來存儲程序和各種數據信息的記憶部件,更通俗地說,存儲器就是用來存放數據的地方。存儲器可分為主存儲器(簡稱主存或內存)和輔助存儲器(簡稱輔存或外存)兩大類,本文將詳細為您科普存儲器的工作原理等知識。

2022-10-11 16:58:43 4874

4874 跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。

2022-10-18 09:12:20 9685

9685 時鐘域clock domain:以寄存器捕獲的時鐘來劃分時鐘域。單時鐘域single clock domain,數據發送和接收是同一個時鐘。

2022-12-26 15:21:04 2610

2610 在一些較為簡單的數字電路中,只有一個時鐘,即所有的觸發器都使用同一個時鐘,那么我們說這個電路中只有一個時鐘域。

2023-03-15 13:58:28 5364

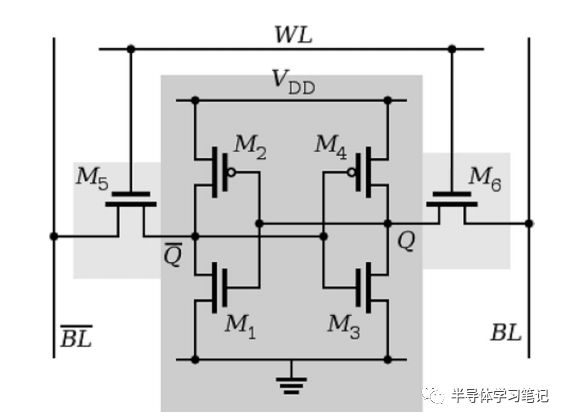

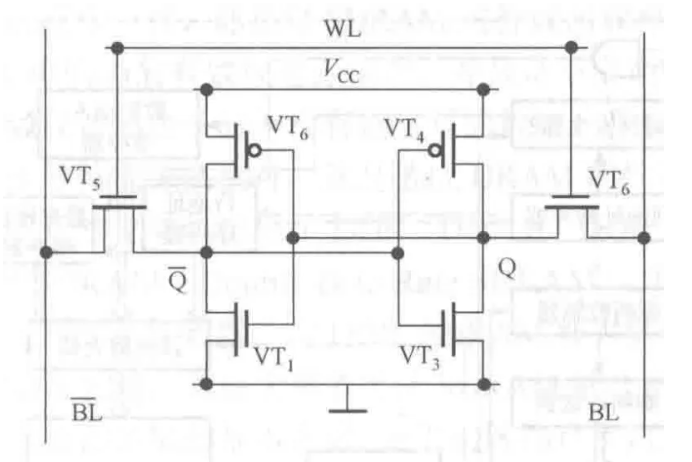

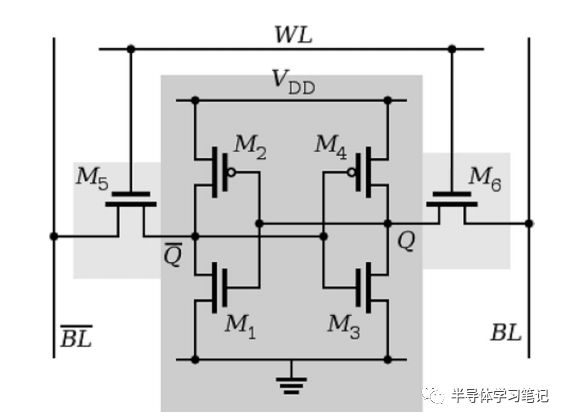

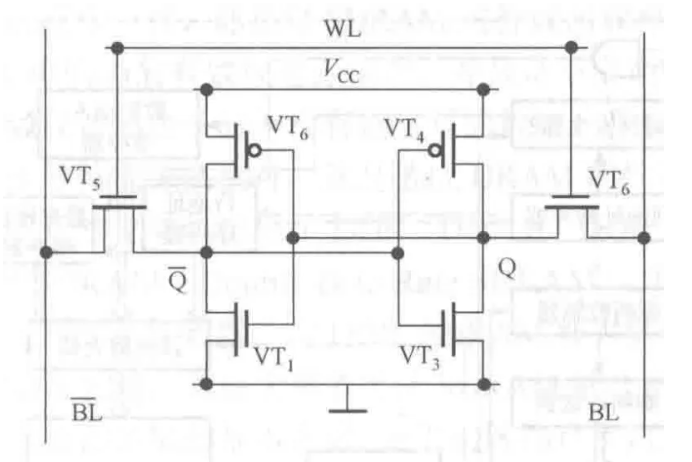

5364 SRAM也是易失性存儲器,但是,與DRAM相比,只要設備連接到電源,信息就被存儲,一旦設備斷開電源,就會失去信息。

這個設備比DRAM要復雜得多,它一般由6個晶體管組成,因此被稱為6T存儲器(如圖1)。

2023-03-21 14:27:01 11788

11788

單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可直接使用xpm_cdc_single

2023-04-13 09:11:37 2057

2057 FIFO是實現多位寬數據的異步跨時鐘域操作的常用方法,相比于握手方式,FIFO一方面允許發送端在每個時鐘周期都發送數據,另一方面還可以對數據進行緩存。需要注意的是對FIFO控制信號的管理,以避免發生

2023-05-11 14:01:27 4891

4891

跨時鐘域操作包括同步跨時鐘域操作和異步跨時鐘域操作。

2023-05-18 09:18:19 1349

1349

跨時鐘域是FPGA設計中最容易出錯的設計模塊,而且一旦跨時鐘域出現問題,定位排查會非常困難,因為跨時鐘域問題一般是偶現的,而且除非是構造特殊用例一般的仿真是發現不了這類問題的。

2023-05-25 15:06:00 2919

2919

上一篇文章已經講過了單bit跨時鐘域的處理方法,這次解說一下多bit的跨時鐘域方法。

2023-05-25 15:07:19 1622

1622

所謂數據流跨時鐘域即:時鐘不同但是時間段內的數據量一定要相同。

2023-05-25 15:19:15 2725

2725

FPGA多bit跨時鐘域適合將計數器信號轉換為格雷碼。

2023-05-25 15:21:31 3677

3677

??類似于電源域(電源規劃與時鐘規劃亦是對應的),假如設計中所有的 D 觸發器都使用一個全局網絡 GCLK ,比如 FPGA 的主時鐘輸入,那么我們說這個設計只有一個時鐘域。假如設計有兩個輸入時鐘,分別給不同的接口使用,那么我們說這個設計中有兩個時鐘域,不同的時鐘域,有著不同的時鐘頻率和時鐘相位。

2023-06-21 11:53:22 4098

4098

CDC(Clock Domain Conversion)跨時鐘域分單bit和多bit傳輸

2023-06-21 14:59:32 3055

3055 在數字電路中,跨時鐘域處理是個很龐大的問題,因此將會作為一個專題來陸續分享。今天先來從處理單bit跨時鐘域信號同步問題來入手。

2023-06-27 11:25:03 2623

2623

跨時鐘域是如何產生的呢?現在的芯片(比如SOC,片上系統)集成度和復雜度越來越高,通常一顆芯片上會有許多不同的信號工作在不同的時鐘頻率下。

2023-06-27 11:39:41 2253

2253

跨時鐘域(CDC)的應從對亞穩定性和同步性的基本了解開始。

2023-06-27 14:25:21 1945

1945

單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可直接使用xpm_cdc_single,如下圖代碼所示。參數DEST_SYNC_FF決定了級聯觸發器

2023-08-16 09:53:23 2215

2215

存儲器是計算機中的重要組成部分,用于存儲程序、數據和控制信息等。根據存儲信息的介質和訪問方式的不同,存儲器可以分為隨機存儲器(RAM)、只讀存儲器(ROM)和硬盤存儲器等幾類。本文將介紹存儲器的工作原理、分類及結構。

2023-09-09 16:18:27 8486

8486 Flash存儲器是一種非易失性存儲器,即使在供電電源關閉后仍能保持片內信息。

2023-09-09 16:22:28 8170

8170 fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據? 在FPGA設計中,通常需要跨時鐘域進行數據通信。跨時鐘域通信就是在不同的時鐘域之間傳輸數據。 當從一個時鐘域傳輸數據到另一個時鐘域

2023-10-18 15:23:51 1901

1901 請問雙口RAM能用來進行跨時鐘域傳輸數據嗎? 雙口RAM是一種用于在兩個時鐘域之間傳輸數據的存儲器,因此它確實可以用于跨時鐘域傳輸數據。在本篇文章中,我們將深入探討雙口RAM的工作原理以及如何利用

2023-10-18 15:24:01 1533

1533 對于數字設計人員來講,只要信號從一個時鐘域跨越到另一個時鐘域,那么就可能發生亞穩態。我們稱為“跨時鐘域”即“Clock Domain Crossing”,或CDC。

2024-01-08 09:39:56 1344

1344

存儲器,作為計算機系統中的核心部件之一,扮演著存儲和檢索數據的角色。無論是程序的執行,還是數據的處理,都離不開存儲器的支持。本文將對存儲器進行詳細的介紹,包括其定義、分類、工作原理以及在計算機系統中的重要性。

2024-05-12 16:56:00 3882

3882 在計算機系統中,存儲器是不可或缺的組成部分,負責存儲程序和數據以供處理器使用。隨著計算機技術的不斷發展,存儲器的種類和性能也在不斷提升。本文將詳細探討存儲器的工作原理及基本結構,以幫助讀者更好地理解計算機系統的存儲機制。

2024-05-12 17:05:00 4023

4023 EEPROM(Electrically Erasable Programmable Read-Only Memory,電可擦可編程只讀存儲器)是一種非易失性存儲器,它能夠在不移除電源的情況下進行

2024-08-05 17:41:29 3220

3220 外部存儲器是指用于存儲數據的獨立設備,它們通常與計算機或其他電子設備連接,并提供額外的存儲空間,允許用戶在不改變主設備內部存儲的情況下保存和訪問大量數據。常見的外部存儲器包括硬盤、U盤(優盤)、光盤、軟盤、磁帶等。下面將詳細介紹這些外部存儲器的工作原理、作用以及它們的特點。

2024-09-05 10:42:58 7384

7384 高速緩沖存儲器(Cache)的工作原理,是基于計算機程序和數據訪問的局部性原理,即程序在執行過程中,對數據的訪問往往呈現出時間和空間的局部性。具體來說,就是程序在某一時間段內,會集中訪問某一小塊內存

2024-09-10 14:14:53 2059

2059 存儲器中的數據是否會因為斷電而丟失,取決于存儲器的類型及其工作原理。在深入探討這個問題之前,我們首先需要了解存儲器的基本分類及其特性。

2024-09-26 15:23:38 7868

7868 (DRAM)那樣周期性地刷新以維持數據。然而,與只讀存儲器(ROM)或閃存不同,SRAM在電力供應停止時,其儲存的數據仍然會消失,因此也被歸類為易失性存儲器(volatile memory)。

2024-09-26 16:25:30 8016

8016

鐵電存儲器(Ferroelectric RAM, FRAM)與閃存(Flash)是兩種不同類型的非易失性存儲器,它們在工作原理、性能特點、應用場景等方面存在顯著的差異。

2024-09-29 15:25:32 4371

4371 采樣到的信號質量!最常用的同步方法是雙級觸發器緩存法,俗稱延遲打拍法。信號從一個時鐘域進入另一個時鐘域之前,將該信號用兩級觸發器連續緩存兩次,可有效降低因為時序不滿足而導致的亞穩態問題。 具體如下圖所示:來自慢時鐘clk

2024-11-16 11:55:32 1854

1854

電子發燒友App

電子發燒友App

評論