請問雙口RAM能用來進行跨時鐘域傳輸數據嗎?

雙口RAM是一種用于在兩個時鐘域之間傳輸數據的存儲器,因此它確實可以用于跨時鐘域傳輸數據。在本篇文章中,我們將深入探討雙口RAM的工作原理以及如何利用它來進行跨時鐘域傳輸數據。

一、雙口RAM的工作原理

雙口RAM是一種有兩個讀寫口的存儲器,因此可以在兩個時鐘域之間傳輸數據。它通常由一個存儲單元陣列和控制邏輯電路組成。其中,存儲單元陣列負責存儲數據,控制邏輯電路則負責管理存儲單元陣列和控制兩個讀寫口的數據傳輸。

在雙口RAM中,有一個時鐘信號,被稱為主時鐘(CLKA),控制寫入和讀取數據的時序。主時鐘和另一個時鐘信號,被稱為次時鐘(CLKB),可以有不同的頻率和相位。從而使得在兩個不同的時鐘域中可以并發地進行數據讀寫操作。

當從A端向B端寫入數據時,數據會被存儲在存儲單元陣列中,并且通過控制邏輯電路,實現從A端到B端的數據傳輸。類似地,從B端向A端寫入數據時,數據也會被存儲在存儲單元陣列中,并通過控制邏輯電路從B端到A端傳輸數據。

二、使用雙口RAM進行跨時鐘域傳輸數據

在實際應用中,雙口RAM可以被用于跨時鐘域傳輸數據。當我們需要在兩個時鐘域之間傳輸數據時,可以使用雙口RAM將數據存儲在中間緩存中,然后轉移到目標時鐘域。這個過程稱為“雙口RAM作為數據交換器”。

在使用雙口RAM進行跨時鐘域傳輸數據時,需要注意以下幾點:

1. 時鐘域轉換

由于操作時鐘不同,我們需要確保在兩個時鐘域中的數據傳輸操作在時間上是協同的。為此,需要使用時鐘域轉換電路將一個時鐘域的信號轉換為另一個時鐘域的信號。

2.數據抖動

在雙口RAM中,數據傳輸操作時間會受到時鐘抖動的影響。因此,需要對時鐘進行周期性重新校準,以避免數據丟失或傳輸錯誤。

3.數據寬度匹配

由于雙口RAM的數據位寬是固定的,因此需要確保在傳輸數據時,源和目標數據位寬是匹配的。如果不匹配,則需要進行數據轉換或者使用多個雙口RAM進行數據傳輸。

三、總結

雙口RAM能夠在兩個時鐘域之間傳輸數據。它基于存儲單元陣列和控制邏輯電路,可以實現在兩個時鐘域中并發地進行讀寫操作。在使用雙口RAM進行跨時鐘域傳輸數據時,需要進行時鐘域轉換、重校準時鐘抖動以及確保數據寬度匹配等處理。雙口RAM作為數據交換器在硬件設計中有著廣泛的應用,實現了在不同時鐘域之間的數據交換。

-

存儲器

+關注

關注

39文章

7750瀏覽量

172086 -

RAM

+關注

關注

8文章

1400瀏覽量

120928 -

時鐘信號

+關注

關注

4文章

508瀏覽量

30062

發布評論請先 登錄

關于1061雙網口配置問題求解

機器視覺網卡的雙口、單口有什么區別?雙口網卡適合哪些場景?

兩個MCU之間快速傳輸數據的方法

CW32F030 UART的主要特性

位域解讀

基于FPGA的高效內存到串行數據傳輸模塊設計

數據預處理軟核加速模塊設計

使用MCU200T開發板的UART口進行數據傳輸

ram ip核的使用

SPI以太網口芯片DM9051ANX在ESP32 C3進行iPerf測試

黑芝麻智能跨域時間同步技術:消除多域計算單元的時鐘信任鴻溝

【RK3568+PG2L50H開發板實驗例程】FPGA部分 | ROM、RAM、FIFO 的使用

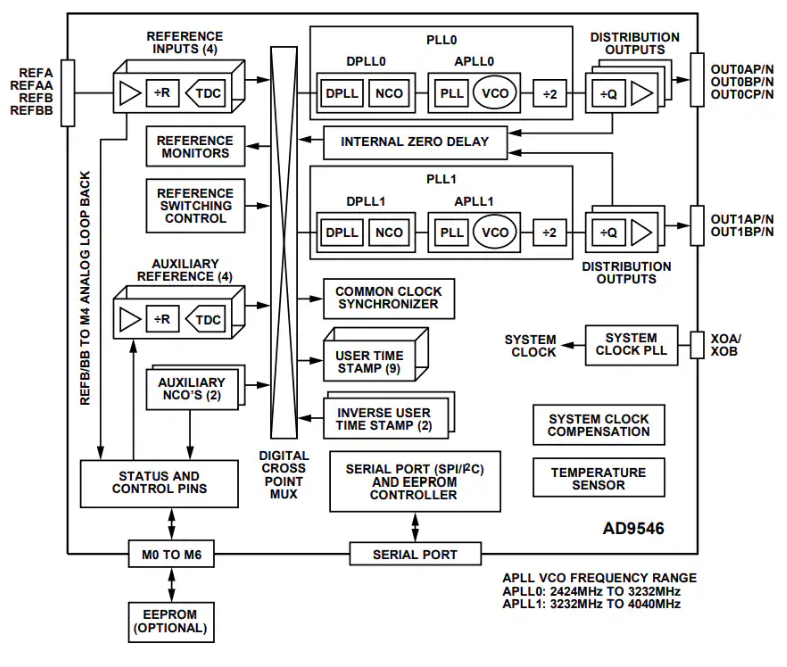

Analog Devices Inc. AD9546雙通道DPLL 數字化時鐘同步器數據手冊

跨異步時鐘域處理方法大全

請問雙口RAM能用來進行跨時鐘域傳輸數據嗎?

請問雙口RAM能用來進行跨時鐘域傳輸數據嗎?

評論