上一篇文章已經(jīng)講過(guò)了單bit跨時(shí)鐘域的處理方法,這次解說(shuō)一下多bit的跨時(shí)鐘域方法:

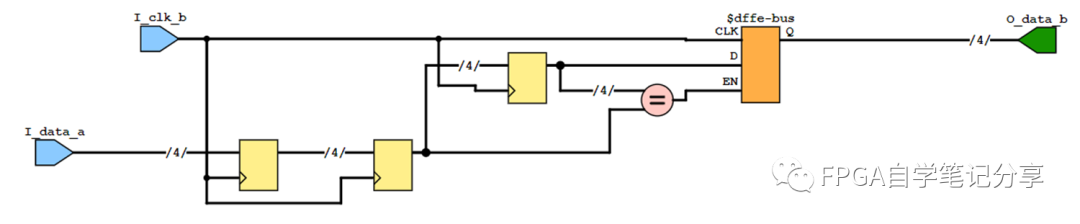

1、打兩拍,比較,具體代碼如下所示。

// ============================================================

// File Name: cm_cdc_4bit

// VERSION : V1.0

// DATA : 2022/9/28

// Author : FPGA干貨分享

// ============================================================

// 功能:4bit慢變信號(hào)跨時(shí)鐘域模塊

// ============================================================

`timescale 1ns/1ps

module cm_cdc_4bit (

input wire I_clk_a , ///輸入時(shí)鐘a

input wire I_clk_b , ///輸入時(shí)鐘b

input wire [3:0] I_data_a , ///a時(shí)鐘輸入信號(hào)

output reg [3:0] O_data_b ///b時(shí)鐘輸出信號(hào)

);

// ============================================================

// wire reg

// ============================================================

reg [3:0] S_data_b_d0 ;

reg [3:0] S_data_b_d1 ;

reg [3:0] S_data_b_d2 ;

// ============================================================

// a時(shí)鐘域

// ============================================================

// ============================================================

// b時(shí)鐘域

// ============================================================

///使用第二個(gè)時(shí)鐘進(jìn)行打拍

always @(posedge I_clk_b)

begin

S_data_b_d0 <= I_data_a ;

S_data_b_d1 <= S_data_b_d0 ;

S_data_b_d2 <= S_data_b_d1 ;

end

//打兩拍之后的信號(hào)進(jìn)行處理

always @(posedge I_clk_b)

if(S_data_b_d2 == S_data_b_d1)

O_data_b <= S_data_b_d2;

else

O_data_b <= O_data_b ;

endmodule

第二種方法就是計(jì)數(shù)器轉(zhuǎn)gray碼。

下一篇將為大家講解格雷碼與二進(jìn)制碼的轉(zhuǎn)換代碼及仿真。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1662文章

22480瀏覽量

638515 -

信號(hào)

+關(guān)注

關(guān)注

12文章

2921瀏覽量

80365 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2320瀏覽量

98456 -

bit

+關(guān)注

關(guān)注

0文章

48瀏覽量

32866 -

時(shí)鐘域

+關(guān)注

關(guān)注

0文章

53瀏覽量

10057

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

關(guān)于跨時(shí)鐘域信號(hào)的處理方法

我在知乎看到了多bit信號(hào)跨時(shí)鐘的問(wèn)題,于是整理了一下自己對(duì)于跨時(shí)鐘域信號(hào)的處理

如何處理好FPGA設(shè)計(jì)中跨時(shí)鐘域問(wèn)題?

時(shí)鐘域處理的方法,這三種方法可以說(shuō)是 FPGA 界最常用也最實(shí)用的

發(fā)表于 09-22 10:24

三種FPGA界最常用的跨時(shí)鐘域處理法式

處理的方法,這三種方法可以說(shuō)是FPGA界最常用也最實(shí)用的方法,這三種方法包含了單bit和多bit

發(fā)表于 02-21 07:00

FPGA初學(xué)者的必修課:FPGA跨時(shí)鐘域處理3大方法

處理的方法,這三種方法可以說(shuō)是FPGA界最常用也最實(shí)用的方法,這三種方法包含了單bit和多bit

發(fā)表于 03-04 09:22

如何處理好FPGA設(shè)計(jì)中跨時(shí)鐘域間的數(shù)據(jù)

介紹3種跨時(shí)鐘域處理的方法,這3種方法可以說(shuō)是FPGA

發(fā)表于 07-29 06:19

FPGA跨時(shí)鐘域處理簡(jiǎn)介

(10)FPGA跨時(shí)鐘域處理1.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4

發(fā)表于 02-23 07:47

FPGA界最常用也最實(shí)用的3種跨時(shí)鐘域處理的方法

介紹3種跨時(shí)鐘域處理的方法,這3種方法可以說(shuō)是FPGA

發(fā)表于 11-15 20:08

?1.5w次閱讀

(10)FPGA跨時(shí)鐘域處理

(10)FPGA跨時(shí)鐘域處理1.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4

發(fā)表于 12-29 19:40

?7次下載

三種跨時(shí)鐘域處理的方法

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問(wèn)題,而如何處理好跨

FPGA跨時(shí)鐘域處理方法(二)

FPGA跨時(shí)鐘域處理方法(二)

評(píng)論